一种基于FPGA和MBS架构的spacewire总线控制器的制作方法

一种基于fpga和mbs架构的spacewire总线控制器

技术领域

1.本发明属于spacewire总线控制器技术领域,具体涉及一种基于fpga和mbs架构的spacewire总线控制器。

背景技术:

2.spacewire总线作为面向航天的高速,点对点全双工的串行总线,有hoci和comi两种接口,其中hoci简单易控,传输速率慢;comi传输速率快但是控制方法复杂。常用的控制方法有两种,软件控制和硬件控制,软件控制灵活但是复杂不易使用,硬件控制使用起来方便但是不灵活。为了改善两种接口的使用性能和易操作性,设计了本控制器。

技术实现要素:

3.本发明的目的是为解决上述问题,提供一种基于fpga和mbs架构的spacewire总线控制器,采用fpga+mbs控制,由fpga搭建底层逻辑,mbs实现上层控制。由于基本逻辑由fpga搭建,使得mbs控制电路很简单,且mbs也能驱动底层,更加灵活的适应各种应用。

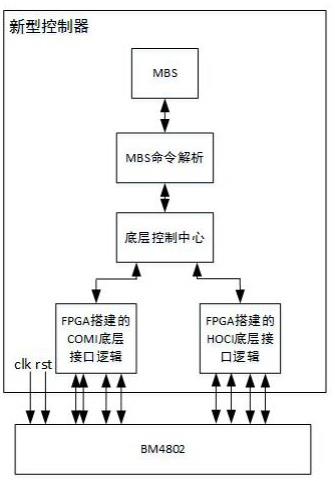

4.为实现上述目的,本发明提供以下技术方案:一种基于fpga和mbs架构的spacewire总线控制器,包含fpga、mbs、hoci接口和comi接口,所述mbs实现上层控制,所述fpga搭建底层逻辑,所述 hoci接口和comi接口用于fpga搭建不同的寄存器读写电路,所述mbs将命令传送到mbs命令解析,所述mbs命令解析将命令传送到底层控制中心,所述底层控制中心选择所需要使用的由fpga搭建的hoci底层接口逻辑或由fpga搭建的comi底层接口逻辑,来发送开始读写命令和读写寄存器开始地址以及读写长度命令。

5.进一步的:所述fpga搭建的comi底层接口逻辑包含一个双口ram,所述mbs和bm4802将命令传送给仲裁模块,所述仲裁模块区分读、写命令并通过ram读控制和ram写控制将数据存储至双口ram中。

6.进一步的:所述控制器使用的spacewire芯片为bm4802控制芯片。

7.进一步的:所述由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑留给mbs的命令口是相同的。

8.与现有技术相比,本发明的有益效果在于:1. mbs软件可灵活控制,且mbs对由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑不区分使用方法,mbs可直接发送命令,增加了可读性与复用性;2. 当使用hoci接口读写数据时,mbs只需发一次命令,由fpga解析可循环去读写bm4802的fifo,提高了软件直接控制hoci接口时的效率, mbs可一次配置读写次数,不需要每读一个数都要重新配置;3. fpga搭建的comi底层接口逻辑增加了大容量双口ram,减少了板卡上的ram缓存,使硬件更加简洁的同时减小了成本;4. fpga+mbs的结合使得hoci接口具备了comi接口的一部分特性,极大程度的提高了hoci接口的传输速率。

附图说明

9.为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是为了更清楚地说明本发明实施例或现有技术中的技术方案,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

10.图1为本发明整体结构示意图;图2为本发明底层hoci接口控制状态机示意图。

具体实施方式

11.为了使本领域技术人员更好地理解本发明的技术方案能予以实施,下面结合具体实施例对本发明作进一步说明,但所举实施例只作为对本发明的说明,不作为对本发明的限定。

12.如图1~2所述的一种基于fpga和mbs架构的spacewire总线控制器,包含fpga和mbs,所述mbs实现上层控制,所述fpga搭建底层逻辑,所述hoci接口和comi接口用于fpga搭建不同的寄存器读写电路,所述mbs将命令传送到mbs命令解析,所述mbs命令解析将命令传送到底层控制中心,所述底层控制中心选择所需要使用的由fpga搭建的hoci底层接口逻辑或由fpda搭建的comi底层接口逻辑,来发送开始读写命令和读写寄存器开始地址以及读写长度命令。

13.所述fpga搭建的comi底层接口逻辑包含一个双口ram,所述mbs和bm4802将命令传送给仲裁模块,所述仲裁模块区分读、写命令并通过ram读控制和ram写控制将数据存储至双口ram中。

14.所述由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑留给mbs的命令口是相同的,即mbs不需要区分hoci接口和comi接口,可以直接发送命令。

15.优选的:采用fpga搭建不同的寄存器读写电路,通过hoci底层接口逻辑和comi底层接口逻辑实现对spacewire 接口芯片bm4802的读写控制。

16.使用comi接口读写数据时,mbs只需发一次命令,由fpga解析可循环去读写bm4802的fifo,提高了软件直接控制hoci接口时的效率。

17.本发明的关键点和保护点:1. mbs软件可灵活控制,且mbs对由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑不区分使用方法,mbs可直接发送命令,增加了可读性与复用性;2. 当使用hoci接口读写数据时,mbs只需发一次命令,由fpga解析可循环去读写bm4802的fifo,提高了软件直接控制hoci接口时的效率, mbs可一次配置读写次数,不需要每读一个数都要重新配置;3. fpga搭建的comi底层接口逻辑里增加了大容量双口ram,减少了板卡上的ram缓存,使硬件更加简洁的同时减小了成本;4. fpga+mbs的结合使得hoci接口具备了comi接口的一部分特性,极大程度的提高了hoci接口的传输速率。

18.本控制器采用fpga搭建不同的寄存器读写电路,通过hoci底层接口逻辑和comi底层接口逻辑实现对spacewire 接口芯片bm4802的读写控制,两个接口控制电路留给mbs的

命令口是一致的,即对于mbs来说,对两种接口是不需要区分使用方法的,只需要配置底层控制中心使用由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑,发开始读写命令和读写寄存器开始地址以及读写长度。本控制器使mbs的软件工作量大大减少,出错率亦跟随较少,使得调试效率得到极大的提高,同时增加了可复用性。

19.本发明中未做详细描述的内容均为现有技术。

20.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

技术特征:

1.一种基于fpga和mbs架构的spacewire总线控制器,包含fpga、mbs、hoci接口和comi接口,其特征在于:所述mbs实现上层控制,所述fpga搭建底层逻辑,所述hoci接口和comi接口用于fpga搭建不同的寄存器读写电路,所述mbs将命令传送到mbs命令解析,所述mbs命令解析将命令传送到底层控制中心,所述底层控制中心选择所需要使用的由fpga搭建的hoci底层接口逻辑或由fpga搭建的comi底层接口逻辑,来发送开始读写命令和读写寄存器开始地址以及读写长度命令。2.根据权利要求1所述的一种基于fpga和mbs架构的spacewire总线控制器,其特征在于:所述fpga搭建的comi底层接口逻辑包含一个双口ram,所述mbs和bm4802将命令传送给仲裁模块,所述仲裁模块区分读、写命令并通过ram读控制和ram写控制将数据存储至双口ram中。3.根据权利要求1所述的一种基于fpga和mbs架构的spacewire总线控制器,其特征在于:所述控制器使用的spacewire芯片为bm4802控制芯片。4.根据权利要求1所述的一种基于fpga和mbs架构的spacewire总线控制器,其特征在于:所述由fpga搭建的comi底层接口逻辑和fpga搭建的hoci底层接口逻辑留给mbs的命令口是相同的。

技术总结

本发明涉及了一种基于FPGA和MBS架构的spacewire总线控制器,由MBS实现上层控制,FPGA搭建底层逻辑。采用FPGA搭建不同的寄存器读写电路,通过HOCI底层接口逻辑和COMI底层接口逻辑实现对spacewire接口芯片BM4802的读写控制。本控制器的底层逻辑由FPGA搭建,简化了MBS的使用,也能使底层驱动更加灵活的适应各种应用场景,且对HOCI接口和COMI接口不区分使用方法,MBS可直接发送命令,增加了底层驱动可读性与复用性;COMI底层接口逻辑里增加了大容量双口RAM,减少了板卡上的RAM缓存,使硬件更加简洁的同时减小了成本。同时FPGA+MBS的结合使得HOCI接口具备了COMI接口的一部分特性,当使用HOCI接口读写数据时,MBS只需发一次命令,由FPGA解析可循环去读写BM4802的FIFO,极大程度的提高了HOCI接口的传输速率。度的提高了HOCI接口的传输速率。度的提高了HOCI接口的传输速率。

技术研发人员:陈润娜 薛时凯 戴春泉 邵志阳 权衡

受保护的技术使用者:理工雷科电子(西安)有限公司

技术研发日:2021.09.28

技术公布日:2021/12/6

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1