一种FPGA模块的制作方法

一种fpga模块

技术领域

1.本实用新型涉及可编程器件领域,具体涉及一种fpga模块。

背景技术:

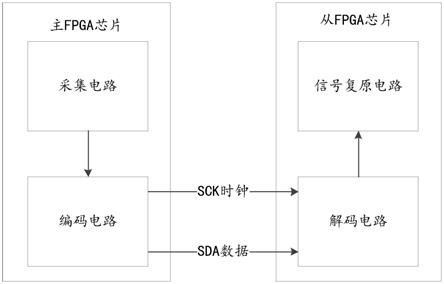

2.fpga是在pal、gal等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。fpga器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。fpga的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块ram,布线资源,内嵌专用硬核,底层内嵌功能单元。由于fpga具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

3.随着fpga的发展,fpga需要实现的功能也就越来越多,现有的fpga因执行功能繁多,内部资源及管脚不够用,严重制约了fpga的发展。

技术实现要素:

4.本实用新型所要解决的技术问题是提供一种fpga模块,可以解决内部资源及管脚不够用。

5.本实用新型解决上述技术问题的技术方案如下:一种fpga模块,包括主fpga芯片和从fpga芯片;所述主fpga芯片内部集成有采集电路和编码电路,所述采集电路与所述编码电路电连接;所述从fpga芯片内部集成有解码电路和信号复原电路,所述解码电路与所述信号复原电路电连接;所述编码电路通过sck时钟信号线以及sda数据信号线与所述解码电路电连接。

6.本实用新型的有益效果是:在本实用新型中,主fpga芯片将内部的信号传递给从fpga芯片,通过从fpga芯片来实现具体功能,即本实用新型通过将主fpga芯片的功能分步化,将以前一个fpga芯片无法完成的功能分成两个fpga来完成,为功能布局提供了便利;本实用新型把主fpga芯片中的部分功能转移到从fpga芯片中,数据处理过程简单高效且稳定性高。

7.在上述技术方案的基础上,本实用新型还可以做如下改进。

8.进一步,所述采集电路包括第一寄存器以及分别与所述第一寄存器电连接的第一触发器和第一计数器;所述编码电路包括第一移位寄存器以及与所述第一移位寄存器电连接的第二触发器;所述第一寄存器的输出端与所述第一移位寄存器的输入端电连接。

9.进一步,所述解码电路包括第二移位寄存器以及与所述第二移位寄存器电连接的第三触发器;信号复原电路包括第二寄存器以及分别与所述第二寄存器电连接的第四触发器和第二计算器;所述第二移位寄存器的输出端与所述第二寄存器的输入端电连接;所述第一移位寄存器的输出端通过sck时钟信号线以及sda数据信号线与所述第二移位寄存器的输入端连接。

10.进一步,所述sck时钟信号线的执行频率范围为1mhz~2mhz。

11.采用上述进一步方案的有益效果是:主fpga芯片和从fpga芯片共用一个sck时钟,实现两个fpga芯片同步的功能;sck执行频率在1mhz~2mhz,低速率,保证数据传输正确性。

12.进一步,所述sda数据信号线的接口报文传输频率为1khz。

13.采用上述进一步方案的有益效果是:sda为串口数据传输,可传输多数据信息,节省了主fpga芯片的管脚资源;接口报文传输频率为1khz,足够一次的报文传输,多余为空闲状态。

附图说明

14.图1为本实用新型一种fpga模块的整体结构示意图;

15.图2为本实用新型一种fpga模块中主fpga芯片的结构示意图;

16.图3为本实用新型一种fpga模块中从fpga芯片的结构示意图。

具体实施方式

17.以下结合附图对本实用新型的原理和特征进行描述,所举实例只用于解释本实用新型,并非用于限定本实用新型的范围。

18.如图1所示,一种fpga模块,包括主fpga芯片和从fpga芯片;所述主fpga芯片内部集成有采集电路和编码电路,所述采集电路与所述编码电路电连接;所述从fpga芯片内部集成有解码电路和信号复原电路,所述解码电路与所述信号复原电路电连接;所述编码电路通过sck时钟信号线以及sda数据信号线与所述解码电路电连接。

19.在本实用新型中,主fpga芯片将内部的信号传递给从fpga芯片,通过从fpga芯片来实现具体功能,即本实用新型通过将主fpga芯片的功能分步化,将以前一个fpga芯片无法完成的功能分成两个fpga来完成,为功能布局提供了便利;本实用新型把主fpga芯片中的部分功能转移到从fpga芯片中,数据处理过程简单高效且稳定性高。

20.在本具体实施例中,如图2所示,所述采集电路包括第一寄存器以及分别与所述第一寄存器电连接的第一触发器和第一计数器;所述编码电路包括第一移位寄存器以及与所述第一移位寄存器电连接的第二触发器;所述第一寄存器的输出端与所述第一移位寄存器的输入端电连接。

21.采集电路对需要传递的内部数据进行采集,并存储下来;编码电路对存储的数据进行编码并传输给下一级的从fpga芯片。采集电路的作用是采集数据并保证采集数据频率在预设范围内,方便编码电路进行编码,同时多个被采集数据经采集后变成同频,便于一起进行编码。编码电路就是一个并串转化的电路。

22.在本具体实施例中,如图3所示,所述解码电路包括第二移位寄存器以及与所述第二移位寄存器电连接的第三触发器;信号复原电路包括第二寄存器以及分别与所述第二寄存器电连接的第四触发器和第二计算器;所述第二移位寄存器的输出端与所述第二寄存器的输入端电连接;所述第一移位寄存器的输出端通过sck时钟信号线以及sda数据信号线与所述第二移位寄存器的输入端连接。

23.解码电路解码出报文内的信息数据,并存储下来;信号复原电路对存储的解码数据进行复原,恢复出主fpga芯片传输的数据;同时从fpga芯片根据恢复的主fpga数据来实

现相应的功能。

24.所述sck时钟信号线的执行频率范围为1mhz~2mhz。主fpga芯片和从fpga芯片共用一个sck时钟,实现两个fpga芯片同步的功能;sck执行频率在1mhz~2mhz,低速率,保证数据传输正确性。

25.所述sda数据信号线的接口报文传输频率为1khz。sda为串口数据传输,可传输多数据信息,节省了主fpga芯片的管脚资源;接口报文传输频率为1khz,足够一次的报文传输,多余为空闲状态。

26.需要说明的是,本实用新型并不涉及计算机程序的改进,编码电路的编码功能是编码电路的现有功能,本实用新型旨在保护各硬件结果以及各硬件结构之间的连接关系。

27.以上所述仅为本实用新型的较佳实施例,并不用以限制本实用新型,凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

技术特征:

1.一种fpga模块,其特征在于:包括主fpga芯片和从fpga芯片;所述主fpga芯片内部集成有采集电路和编码电路,所述采集电路与所述编码电路电连接;所述从fpga芯片内部集成有解码电路和信号复原电路,所述解码电路与所述信号复原电路电连接;所述编码电路通过sck时钟信号线以及sda数据信号线与所述解码电路电连接。2.根据权利要求1所述的fpga模块,其特征在于:所述采集电路包括第一寄存器以及分别与所述第一寄存器电连接的第一触发器和第一计数器;所述编码电路包括第一移位寄存器以及与所述第一移位寄存器电连接的第二触发器;所述第一寄存器的输出端与所述第一移位寄存器的输入端电连接。3.根据权利要求2所述的fpga模块,其特征在于:所述解码电路包括第二移位寄存器以及与所述第二移位寄存器电连接的第三触发器;信号复原电路包括第二寄存器以及分别与所述第二寄存器电连接的第四触发器和第二计算器;所述第二移位寄存器的输出端与所述第二寄存器的输入端电连接;所述第一移位寄存器的输出端通过sck时钟信号线以及sda数据信号线与所述第二移位寄存器的输入端连接。4.根据权利要求1至3任一项所述的fpga模块,其特征在于:所述sck时钟信号线的执行频率范围为1mhz~2mhz。5.根据权利要求1至3任一项所述的fpga模块,其特征在于:所述sda数据信号线的接口报文传输频率为1khz。

技术总结

本实用新型涉及一种FPGA模块,包括主FPGA芯片和从FPGA芯片;主FPGA芯片内部集成有采集电路和编码电路,采集电路与编码电路电连接;从FPGA芯片内部集成有解码电路和信号复原电路,解码电路与信号复原电路电连接;编码电路通过SCK时钟信号线以及SDA数据信号线与解码电路电连接。在本实用新型中,主FPGA芯片将内部的信号传递给从FPGA芯片,通过从FPGA芯片来实现具体功能,即本实用新型通过将主FPGA芯片的功能分步化,将以前一个FPGA芯片无法完成的功能分成两个FPGA来完成,为功能布局提供了便利;本实用新型把主FPGA芯片中的部分功能转移到从FPGA芯片中,数据处理过程简单高效且稳定性高。性高。性高。

技术研发人员:王映波 杨乐 刘森林

受保护的技术使用者:中域高科(武汉)信息技术有限公司

技术研发日:2021.04.13

技术公布日:2021/11/2

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1