端子和数据输入/输出电路布局的制作方法

背景技术:

1、高数据可靠性、高存储器存取速度、减小的芯片大小和较低功率消耗是半导体存储器所需要的特征。

2、在用于半导体装置的常规外围电路系统中,举例来说,衬垫和数据队列电路(或数据输入/输出电路)以跨越层的对应方式布置。数据队列电路或数据输入/输出电路在下文中统称为“dq电路”。被配置成耦合到半导体装置外部的外部电路系统的每一衬垫位于其相应dq电路附近(例如,在其正上方),以便保持衬垫与dq电路之间的布线具有足够短以具有相同低阻抗的相同长度。近年来,已致力于减少由包含在存储器装置的半导体裸片上的外围电路系统占据的外围电路区的面积。举例来说,每一dq电路的大小已变得更小,以便通过更短布线(例如,时钟信号线clk,其提供到dq电路的时钟信号)提高驱动能力以实现更快操作。然而,在减少衬垫的面积方面存在限制。

技术实现思路

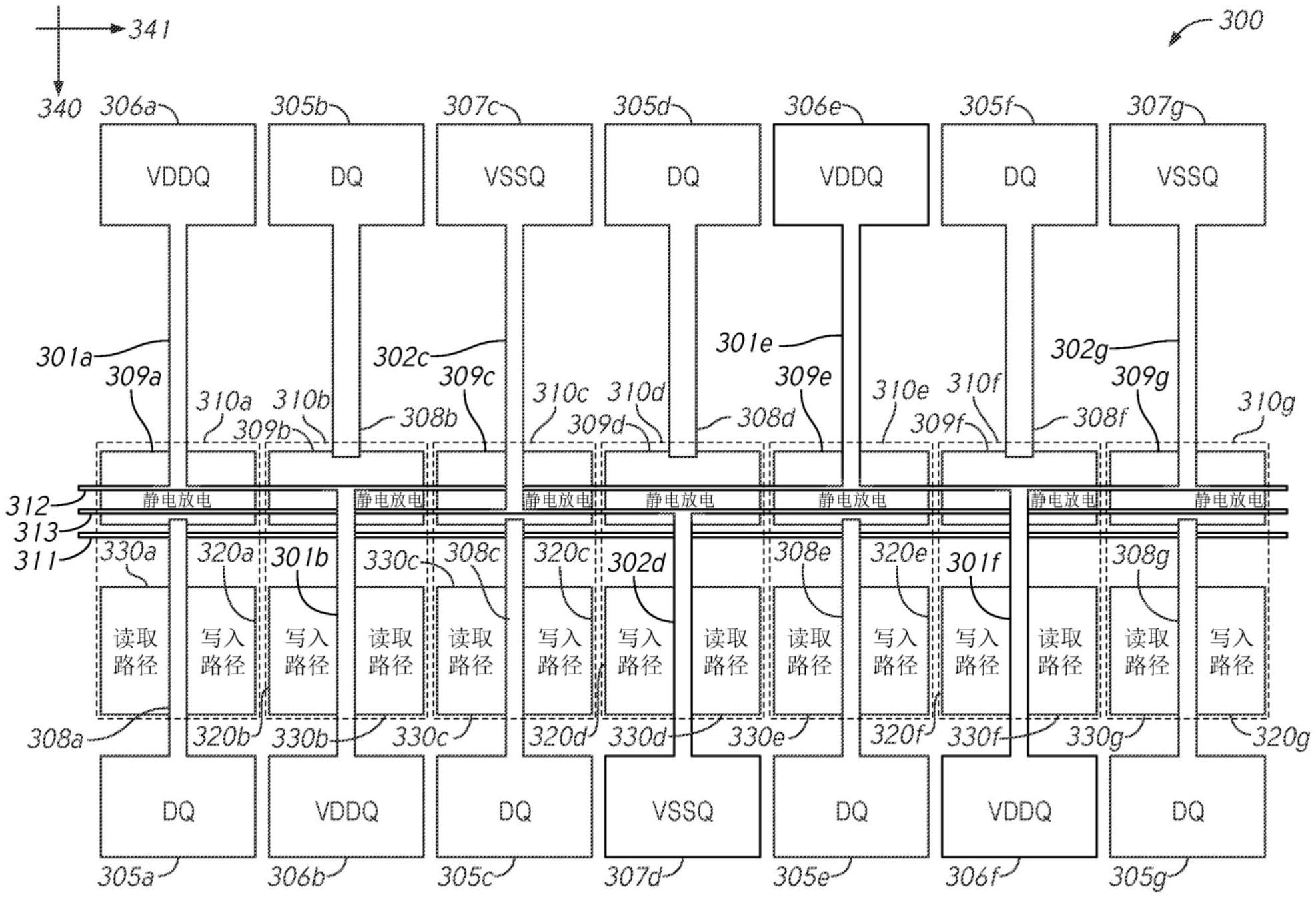

1、公开了具有包含电路区的减小面积的端子和数据输入/输出电路布局的设备。根据本公开的实施例的示例设备包含:存储器单元阵列,其包含多个存储器区;多个数据衬垫;以及多个数据队列(dq)电路。多个数据衬垫包含奇数编号的数据衬垫和偶数编号的数据衬垫。多个数据队列(dq)电路包含在一方向上交替地布置的奇数编号的dq电路和偶数编号的dq电路。每一dq电路可耦合在多个数据衬垫中的对应数据衬垫与存储器单元阵列的多个存储器区中的对应存储器区之间。耦合到对应奇数编号的dq电路的奇数编号的数据衬垫可布置在多个dq电路的一侧处,并且耦合到对应偶数编号的dq电路的偶数编号的dq衬垫可布置在多个dq电路的相对侧处。

2、根据本公开的实施例的另一示例设备包含第一数据队列(dq)电路和第二dq电路、第一数据衬垫和第二数据衬垫,以及第一电力衬垫和第二电力衬垫。第一dq电路在第一总线上接收第一读取数据且提供第一读取数据,且进一步被配置成在第一总线上接收第一写入数据且提供第一写入数据。第一数据衬垫从第一dq电路接收第一读取数据,且进一步接收第一写入数据且将第一写入数据提供到第一dq电路。第一电力衬垫相对于第一dq电路安置在第一数据衬垫对面。邻近于第一dq电路的第二dq电路在第二总线上接收第二读取数据且提供第二读取数据,且进一步在第二数据总线上接收第二写入数据且提供第二写入数据。邻近于第一电力衬垫的第二数据衬垫从第二dq电路接收第二读取数据,且进一步接收第二写入数据且将第二写入数据提供到第二dq电路。邻近于第一数据衬垫的第二电力衬垫相对于第二dq电路安置在第二数据衬垫对面。

3、根据本公开的实施例的另一示例设备包含第一数据队列(dq)电路和第二dq电路、第一数据衬垫和第二数据衬垫、第一导体和第二导体、邻近于第二数据衬垫的第一电力衬垫,以及邻近于第一数据衬垫的第二电力衬垫。第一dq电路和第二dq电路从存储器单元阵列接收读取数据且提供读取数据,且进一步被配置成接收写入数据且将写入数据提供到存储器单元阵列。第一数据衬垫和第二数据衬垫中的每一衬垫从对应dq电路接收读取数据,且进一步接收写入数据且将写入数据提供到对应dq电路。第一导体和第二导体中的每一导体将对应数据衬垫耦合到对应dq电路。第一数据衬垫和第一电力衬垫相对于第一dq电路安置在彼此对面。第二数据衬垫和第二电力衬垫相对于第二dq电路安置在彼此对面。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述奇数编号的dq电路包含第一dq电路,且所述偶数编号的dq电路包含在所述方向上邻近于所述第一dq电路的第二dq电路,

3.根据权利要求2所述的设备,其中所述第一电路组件和所述第二电路组件相对于所述第一dq电路与所述第二dq电路之间的边界以对称方式安置。

4.根据权利要求3所述的设备,其中所述第一dq电路和所述第二dq电路中的每一dq电路包括第一路径块和第二路径块,且

5.根据权利要求4所述的设备,其中所述第一dq电路和所述第二dq电路的所述第二路径块中的每一第二路径块包括:

6.根据权利要求4所述的设备,其中所述第一dq电路和所述第二dq电路的所述第二路径块中的每一第二路径块包括:

7.根据权利要求2所述的设备,其中所述第一dq电路包括第一静电放电(esd)保护电路,所述第一esd保护电路耦合到对应第一数据衬垫,且被配置成保护所述第一dq电路免于由于来自所述第一数据衬垫的静电放电而导致的失效,

8.根据权利要求7所述的设备,其进一步包括:

9.根据权利要求8所述的设备,其中所述第一esd保护电路和所述第二esd保护电路以及所述第一dq电路和所述第二dq电路安置在基础层上,且

10.根据权利要求8所述的设备,其中所述第一导体和所述第二导体由分布导电层制成。

11.一种设备,其包括:

12.根据权利要求11所述的设备,其中所述第一dq电路和所述第二dq电路中的每一dq电路包括电路,且

13.根据权利要求11所述的设备,其中所述第一电力衬垫被配置成将第一电源提供到所述第一dq电路,且所述第二电力衬垫被配置成将第二电源提供到所述第一dq电路。

14.根据权利要求11所述的设备,其进一步包括:

15.根据权利要求14所述的设备,其中所述第二电力衬垫、所述第一数据衬垫和所述第三电力衬垫在所述方向上对准。

16.根据权利要求15所述的设备,其中所述第一数据衬垫、所述第一dq电路和所述第一电力衬垫在垂直于所述方向的另一方向上对准。

17.一种设备,其包括:

18.根据权利要求17所述的设备,其进一步包括:

19.根据权利要求17所述的设备,其中所述第一dq电路包括通过所述第二导体耦合到所述第二数据衬垫的第一esd保护电路,

20.根据权利要求18所述的设备,其中所述第一dq电路包括通过所述第二导体耦合到所述第二数据衬垫的第一esd保护电路,

技术总结

描述了用于提供包含在半导体装置的外部端子中的衬垫的设备。示例设备包含存储器单元阵列、数据队列(DQ)电路、数据衬垫和电力衬垫。所述存储器单元阵列可包含一或多个存储器单元。在写入操作中,所述数据衬垫接收写入数据且将所述写入数据提供到所述DQ电路。所述DQ电路接收所述写入数据且将所述写入数据提供到所述存储器单元阵列。在读取操作中,所述DQ电路从所述存储器单元阵列接收读取数据且提供所述读取数据。所述数据衬垫从所述DQ电路接收所述读取数据且提供所述读取数据。所述电力衬垫提供电源电压。所述数据衬垫和所述电力衬垫相对于所述DQ电路安置在彼此对面。

技术研发人员:石井利尚

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!