一种有效避免故障注入攻击的方法与流程

1.本发明涉及信息技术领域,具体为一种有效避免故障注入攻击的方法。

背景技术:

2.soc(system on chip)芯片是设备或系统的核心,其中包含cpu(处理器)、硬件功能模块及运行软件等。许多soc芯片启动或复位后会从efuse中读取一些关键信息(配置信息、关键数据、加密密钥等),再根据这些关键信息进行后续的控制、运算及软件解密等操作。攻击者为了获取这些关键数据及软件代码,会采用多种方法对其进行攻击,以便获取efuse数据,故障注入便是其中一种常用的手段。

3.故障注入实现方式是在精准的时间点将特定电压波动或时钟波动注入到soc芯片,人为地产生故障,使得soc内部的cpu跳过特定的指令或得到错误计算结果。利用大量重复的故障注入,攻击者就可能绕开安全措施,非法获取efuse的数据,最终拿到密钥,以至于可以读取用户存放在f l ash的软件代码及敏感数据,并以此对系统进行攻击。

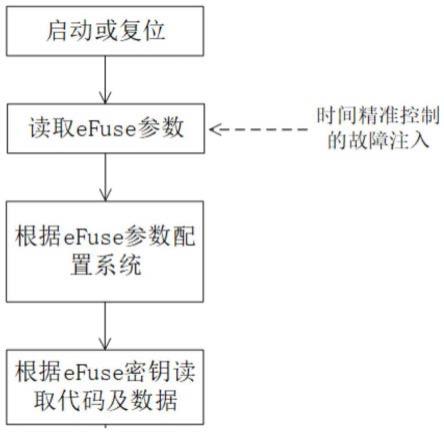

4.故障注入的精准时间点及注入故障类型是通过重复、密集地注入故障的方式尝试出来的。如果soc芯片启动流程一成不变,则很容易被这种故障注入方法突破,具体过程见说明书附图1。

技术实现要素:

5.(一)解决的技术问题

6.针对现有技术的不足,本发明提供了一种有效避免故障注入攻击的方法,解决了现有技术中被故障注入方法攻击,导致efuse的数据被非法获取的问题。

7.(二)技术方案

8.为实现以上目的,本发明通过以下技术方案予以实现:一种有效避免故障注入攻击的方法,包括soc芯片,所述soc芯片包含有cpu、efuse和trng模块;

9.所述trng模块用于产生随机数;

10.所述cpu通过随机数计算得到随机时间和随机数据长度;

11.所述cpu分批次从efuse读取随机数据长度的信息,每次读取后延时一个随机时间。

12.优选的,在所述cpu分批次从efuse读取随机数据长度的信息之后还有:cpu对efuse读取的信息进行控制、运算、解密。

13.优选的,所述随机时间在一毫秒到一百毫秒之间。

14.优选的,所述随机数据长度在1~8bits之间。

15.(三)有益效果

16.本发明提供了一种有效避免故障注入攻击的方法。具备以下有益效果:

17.本发明无需额外增加硬件成本,通过soc芯片所具有的trng模块,增强对故障注入攻击的保护能力,在soc芯片复位启动时实施避免故障注入攻击的程序,启动后不会对底层

驱动、操作系统、应用程序等带来任何影响。

附图说明

18.图1为现有技术中故障注入的流程图;

19.图2为本发明中的分批次从efuse中读取信息的流程图。

具体实施方式

20.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

21.实施例:

22.如图1-2所示,本发明实施例提供一种有效避免故障注入攻击的方法,在启动或复位soc芯片后,soc芯片所包含的cpu读取trng模块产生的随机数值,之后cpu对随机数值进行计算得到一个5ms的随机时间,即本次cpu从efuse读取信息后的延迟时间,cpu对随机数值进行计算得到一个2bits的随机数据长度,即本次cpu从efuse读取信息的数据长度为2bits,每次读取一次efuse数据之后,cpu再从trng模块重新读取随机数值,之后依次计算的随机时间和数据长度为20ms和2bits、35ms和5bits、40ms和3bits

……

,直至efuse被读取完成。

23.具体为:soc芯片分批次从efuse读取2bits的数据信息,延时5ms,读取2bits的数据信息,延时20ms;读取5bits的数据信息,延时35ms;读取3bits的数据信息、延时40ms

……

,直至efuse被读取完成,由于随机时间和随机数据长度是不确定的,使得攻击者无法准确捕捉重复注入故障的时机,有效地避免系统被故障注入的方法攻破。

24.其中trng模块具体指真随机数生成器,efuse指一次性可编程存储器,其内存储的信息包括配置信息、关键数据、加密密钥。

25.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

技术特征:

1.一种有效避免故障注入攻击的方法,包括soc芯片,其特征在于:所述soc芯片包含有cpu、efuse和trng模块;所述trng模块用于产生随机数;所述soc芯片通过随机数计算得到随机时间和随机数据长度;所述soc芯片分批次从efuse读取随机数据长度的信息,每次读取后延时一个随机时间。2.根据权利要求1所述的一种有效避免故障注入攻击的方法,其特征在于,在所述soc芯片分批次从efuse读取随机数据长度的信息之后还有:soc芯片对efuse读取的信息进行控制、运算、解密。3.根据权利要求1所述的一种有效避免故障注入攻击的方法,其特征在于:所述随机时间在一毫秒到一百毫秒之间。4.根据权利要求1所述的一种有效避免故障注入攻击的方法,其特征在于:所述随机数据长度在1~8bits之间。

技术总结

本发明提供一种有效避免故障注入攻击的方法,涉及信息技术领域。该有效避免故障注入攻击的方法,包括SoC芯片,所述SoC芯片包含有CPU、eFuse和TRNG模块,所述TRNG模块用于产生随机数,所述SoC芯片通过随机数计算得到随机时间和随机数据长度,所述SoC芯片分批次从eFuse读取随机数据长度的信息,每次读取后延时一个随机时间。本发明无需额外增加硬件成本,通过SoC芯片所具有的TRNG模块,增强对故障注入攻击的保护能力,在SoC芯片复位启动时实施避免故障注入攻击的程序,启动后不会对底层驱动、操作系统、应用程序等带来任何影响。应用程序等带来任何影响。应用程序等带来任何影响。

技术研发人员:曾小光 蒋荟林 吴家富 胡坚珉

受保护的技术使用者:忆月启函(上海)科技有限公司

技术研发日:2022.02.16

技术公布日:2022/10/24

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1