自动生成芯片设计RTL代码的方法、电子设备和介质与流程

本发明涉及芯片设计,尤其涉及一种自动生成芯片设计rtl代码的方法、电子设备和介质。

背景技术:

1、在芯片设计过程中,通常需要建立多个模块以及多个层级之间的互联,尤其是gpu这种大规模的芯片设计,手动建立互联效率极低,因此需要自动互联。现有技术中,通常采用脚本(例如excel),使用pin互联。例如把所有的管脚列到excel里去,然后通过脚本在excel里抓信号来做适配的互联,但现有技术至少具有以下缺点:把所有信号放置在excel里,维护困难,处理excel速度非常慢,且excel本身描述的一些内容比较简单,很难去自定义一些互联规则,可扩展性差。此外,现有技术均是基于底层信号层建立互联关系的,采用现有的方式进行芯片设计,需要编写大量的底层信号代码(例如verilog代码),设计效率低,容易出错,且扩展性差,不能实现灵活配置及重构。由此可知,如何提供一种不易出错、高效、可扩展、可重构、可配置的芯片设计技术成为亟待解决的技术问题。

技术实现思路

1、本发明目的在于,提供一种自动生成芯片设计rtl代码的方法、电子设备和介质,基于高层次抽象层建立互联,提高了芯片设计的效率,不易出错,且能够实现可重构、可配置,可扩展性强。

2、根据本发明第一方面,提供了自动生成芯片设计rtl代码的方法,包括:

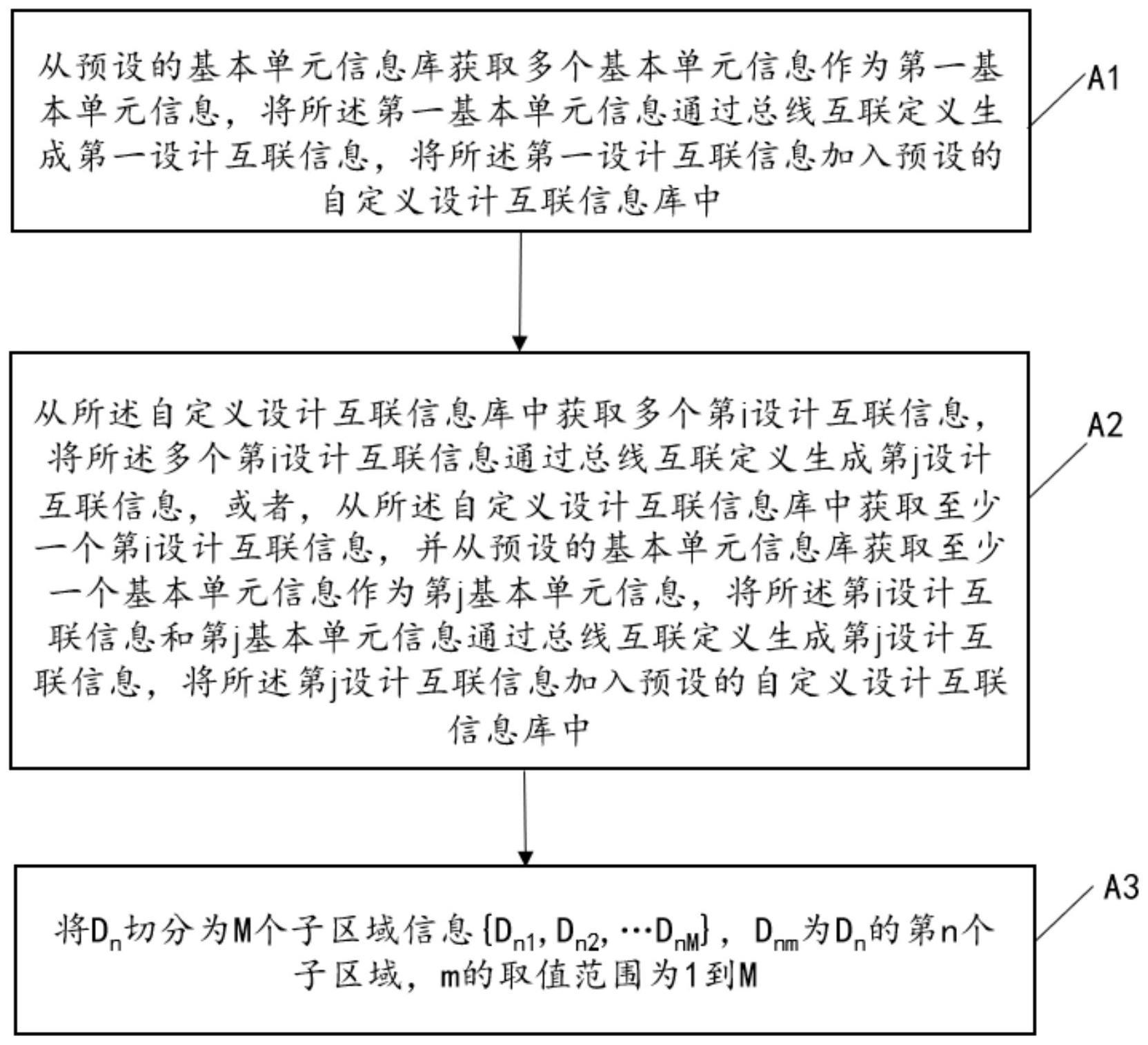

3、步骤a1、从预设的基本单元信息库获取多个基本单元信息作为第一基本单元信息,将所述第一基本单元信息通过总线互联定义生成第一设计互联信息,将所述第一设计互联信息加入预设的自定义设计互联信息库中,所述基本单元信息库中存储多个基本单元信息,所述基本单元信息为rtl代码;

4、步骤a2、从所述自定义设计互联信息库中获取多个第i设计互联信息,将所述多个第i设计互联信息通过总线互联定义生成第j设计互联信息,或者,从所述自定义设计互联信息库中获取至少一个第i设计互联信息,并从预设的基本单元信息库获取至少一个基本单元信息作为第j基本单元信息,将所述第i设计互联信息和第j基本单元信息通过总线互联定义生成第j设计互联信息,将所述第j设计互联信息加入预设的自定义设计互联信息库中,j的取值范围为2到n,n为目标设计层级总数,i的取值范围为1到j-1;

5、步骤a3、基于第n设计互联信息生成芯片设计rtl代码。

6、根据本发明第二方面,提供一种电子设备,包括:至少一个处理器;以及,与所述处理器通信连接的存储器;其中,所述存储器存储有可被所述处理器执行的指令,所述指令被设置为用于执行本发明第一方面所述的方法。

7、根据本发明第三方面,提供一种计算机可读存储介质,所述计算机指令用于执行本发明第一方面所述的方法。

8、本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种自动生成芯片设计rtl代码的方法、电子设备和介质可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:

9、本发明只需对基本单元信息编写底层rtl代码,然后基于基本单元信息通过总线互联组成第一设计互联信息,即第一层级的设计互联信息,后续所有层级的设计互联信息均由已生成的设计互联信息、基本单元信息堆叠,且所有组成部分均通过总线互联定义,生成每一层级的设计互联信息,即仅通过高层次的抽象描述,通过简单的总线互联定义,即可生成每一层级的设计互联信息,无需编写大量的底层信号代码,且不出错,提高了芯片设计的效率。

10、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

技术特征:

1.一种自动生成芯片设计rtl代码的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,

3.根据权利要求2所述的方法,其特征在于,

4.根据权利要求2所述的方法,其特征在于,:

5.根据权利要求2所述的方法,其特征在于,:

6.根据权利要求3-5中任意一项所述的方法,其特征在于:

7.根据权利要求1所述的方法,其特征在于:

8.根据权利要求7所述的方法,其特征在于,:

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,存储有计算机可执行指令,所述计算机可执行指令用于执行前述权利要求1-8中任一项所述的方法。

技术总结

本发明涉及一种自动生成芯片设计RTL代码的方法、电子设备和介质,方法包括步骤A1、获取多个基本单元信息作为第一基本单元信息,通过总线互联定义生成第一设计互联信息,加入自定义设计互联信息库中;步骤A2、从自定义设计互联信息库中获取多个第i设计互联信息,通过总线互联定义生成第j设计互联信息,或者,获取至少一个第i设计互联信息,并获取至少一个基本单元信息作为第j基本单元信息,通过总线互联定义生成第j设计互联信息,加入预设的自定义设计互联信息库中;步骤A3、基于第N设计互联信息生成芯片设计RTL代码。本发明基于高层次抽象层建立互联,提高了芯片设计的效率,不易出错,且能够实现可重构、可配置,可扩展性强。

技术研发人员:请求不公布姓名

受保护的技术使用者:沐曦集成电路(上海)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!