一种任意波形发生器同步方法与流程

本发明涉及仪器,具体涉及一种任意波形发生器同步方法。

背景技术:

1、在某些前沿科技研究领域,需要多个任意波形发生器协同工作,当任意波形发生器数量增多以后,任意波形发生器发送的波形存在相位抖动现象,这在对同步性要求较高的应用中是不允许的,因此提供一种任意波形发生器同步方法是一个需要解决的技术问题。

技术实现思路

1、本发明为了克服以上技术的不足,提供了一种两个pxie机箱中任意波形发生器之间的波形同步的方法。

2、本发明克服其技术问题所采用的技术方案是:

3、一种任意波形发生器同步方法,包括如下步骤:

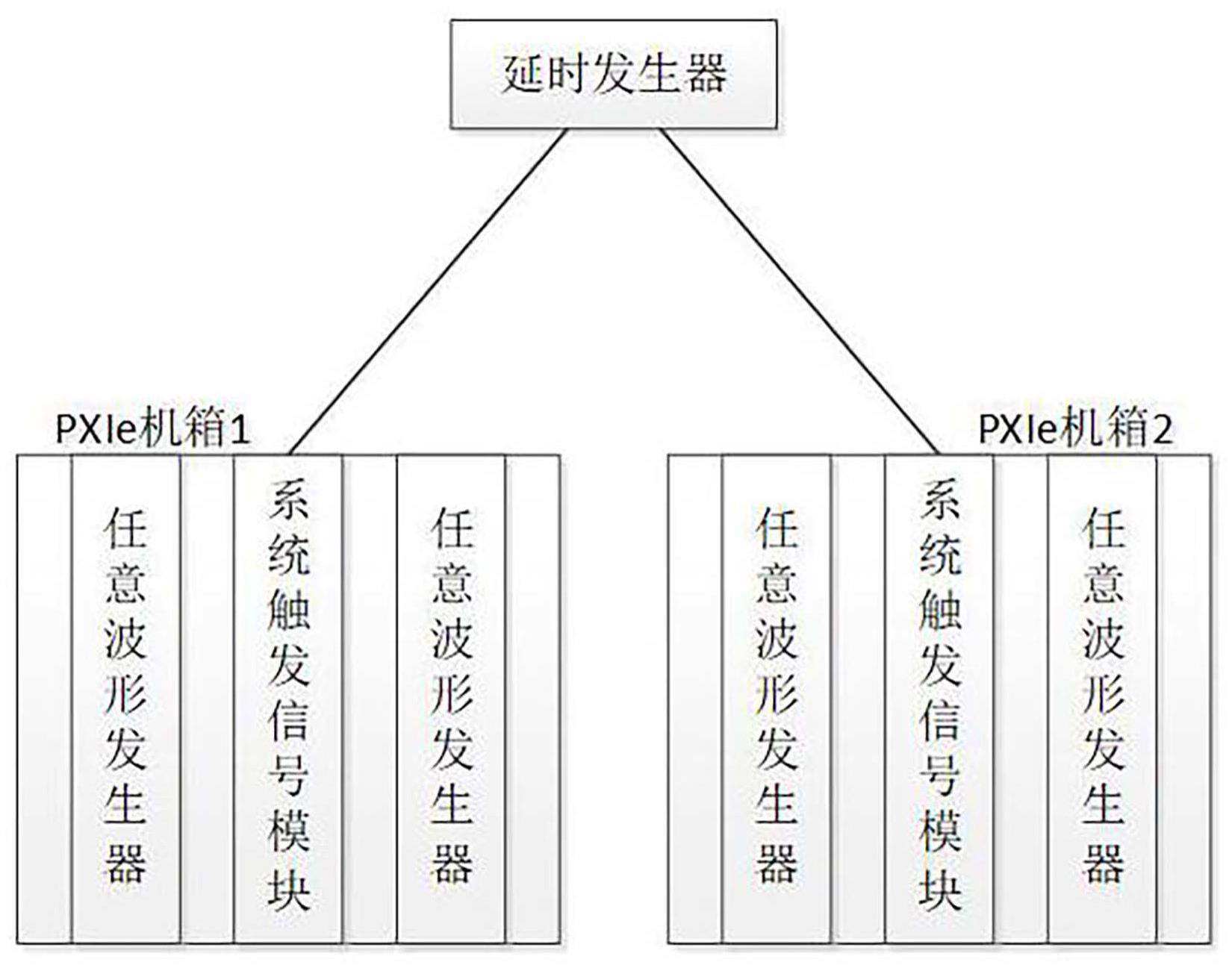

4、a)建立由测控计算机、时钟源、延时发生器和两个pxie机箱组成的系统,时钟源为延时发生器和pxie机箱提供参考时钟,pxie机箱中各防止一个系统触发信号模块和若干个任意波形发生器,系统触发信号模块和任意波形发生器的时钟同步到pxie机箱使用的时钟;

5、b)pxie机箱通过机箱背板路由延时发生器触发信号到系统触发信号模块,系统触发信号模块分发外部触发信号到各个任意波形发生器,任意波形发生器fpga采样外部触发信号的上升沿;

6、c)设置延时发生器输出两路同步触发信号,两路同步触发信号分别输入两个pxie机箱的触发信号输入端口;

7、d)测控计算机发送设置外部触发信号周期与fpga时钟周期比值的指令到任意波形发生器;

8、e)任意波形发生器执行设置比值的指令后采样外部触发信号;

9、f)当任意波形发生器采样到外部触发信号上升沿,则执行步骤g),如果任意波形发生器没有采样到外部触发信号上升沿,则返回执行步骤e);

10、g)开始对任意波形发生器fpga时钟周期进行计数;

11、h)当对fpga时钟周期的计数值达到外部触发信号周期与fpga时钟周期的比值时,执行步骤i),如果fpga时钟周期的计数值没有达到外部触发信号周期与fpga时钟周期的比值时,返回执行步骤g);

12、i)任意波形发生器产生内部触发信号并对fpga时钟周期重新计数;

13、j)测控计算机为任意波形发生器加载波形数据并启动波形发送;

14、k)任意波形发生器在内部触发信号的触发下发送波形。

15、进一步的,步骤a)中时钟源为延时发生器和pxie机箱提供10mhz参考时钟。

16、进一步的,步骤b)中系统触发信号模块通过pxi_star分发外部触发信号到各个任意波形发生器,任意波形发生器fpga使用时钟周期为4ns的时钟的上升沿采样外部触发信号的上升沿。

17、进一步的,步骤c)中延时发生器输出两路同步触发信为周期为200μs的方波。

18、进一步的,当需要改变任意波形发生器的内部触发信号周期时,测控计算机向任意波形发生器发送指令重新设置外部触发信号周期与fpga时钟周期的比值。

19、本发明的有益效果是:设置延时发生器输出两路同步触发信号,两路同步触发信号分别输入两个pxie机箱的触发信号输入端口,pxie机箱通过机箱背板路由延时发生器触发信号到各自的系统触发信号模块,系统触发信号模块通过pxi_star分发外部触发信号到所在机箱的任意波形发生器,测控计算机发送设置外部触发信号周期与fpga时钟周期比值的指令到任意波形发生器,任意波形发生器执行设置比值指令后采样外部触发信号,以外部触发信号上升沿为起点对fpga时钟周期进行计数,每当计数值达到设置的比值时产生内部触发信号并重新计数,任意波形发生器启动波形发送后在内部触发信号的触发下发送波形,实现两个pxie机箱中任意波形发生器之间的波形同步。

技术特征:

1.一种任意波形发生器同步方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的任意波形发生器同步方法,其特征在于:步骤a)中时钟源为延时发生器和pxie机箱提供10mhz参考时钟。

3.根据权利要求1所述的任意波形发生器同步方法,其特征在于:步骤b)中系统触发信号模块通过pxi_star分发外部触发信号到各个任意波形发生器,任意波形发生器fpga使用时钟周期为4ns的时钟的上升沿采样外部触发信号的上升沿。

4.根据权利要求1所述的任意波形发生器同步方法,其特征在于:步骤c)中延时发生器输出两路同步触发信为周期为200μs的方波。

5.根据权利要求1所述的任意波形发生器同步方法,其特征在于:当需要改变任意波形发生器的内部触发信号周期时,测控计算机向任意波形发生器发送指令重新设置外部触发信号周期与fpga时钟周期的比值。

技术总结

一种任意波形发生器同步方法,设置延时发生器输出两路同步触发信号,两路同步触发信号分别输入两个PXIe机箱的触发信号输入端口,PXIe机箱通过机箱背板路由延时发生器触发信号到各自的系统触发信号模块,系统触发信号模块通过PXI_STAR分发外部触发信号到所在机箱的任意波形发生器,测控计算机发送设置外部触发信号周期与FPGA时钟周期比值的指令到任意波形发生器,任意波形发生器执行设置比值指令后采样外部触发信号,以外部触发信号上升沿为起点对FPGA时钟周期进行计数,每当计数值达到设置的比值时产生内部触发信号并重新计数,任意波形发生器启动波形发送后在内部触发信号的触发下发送波形,实现两个PXIe机箱中任意波形发生器之间的波形同步。

技术研发人员:李清石,胡广建,赵鑫鑫,刘强,金长新

受保护的技术使用者:浪潮集团有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!