一种存储结构及存储器的制作方法

本发明涉及存储,尤其涉及一种存储结构及存储器。

背景技术:

1、目前,现有技术在采用两片以上的存储芯片进行容量扩展时,一般是将该两片以上的存储芯片排列在pcb板(printed circuit board,印制电路板)上,然后在pcb板上进行布线,以将该两片以上的存储芯片的命令线连接在一起以及将该两片以上的存储芯片的地址线连接在一起。从而实现存储容量的扩展。

2、现有技术虽然能够实现存储容量扩展,但是该种方式会浪费pcb板上的布线资源,封装成本高。

技术实现思路

1、鉴于上述问题,提出了本发明以便提供一种存储结构及存储器,在实现存储容量扩展的过程中避免了增加pcb板的布线资源,降低了封装成本。

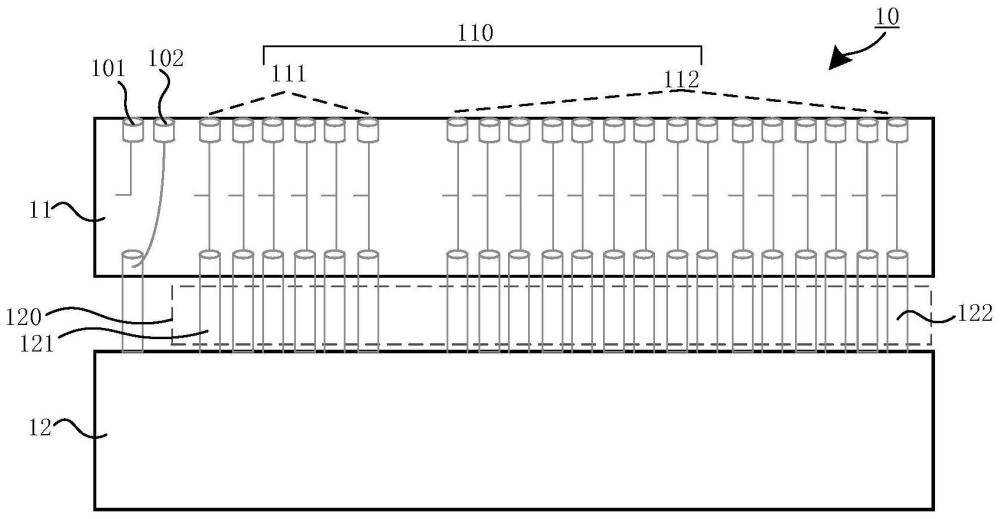

2、第一方面,提供了一种存储结构,包括:第一存储芯片和第二存储芯片;所述第一存储芯片堆叠设置在所述第二存储芯片一侧,所述第一存储芯片和所述第二存储芯片之间三维连接;所述第一存储芯片设置有用于连接至预设的电路板的多个引脚,所述第一存储芯片的信号传输线与所述引脚连接,所述第二存储芯片的信号传输线穿过所述第一存储芯片与所述引脚连接;所述存储结构被配置为在接收到预设的第一片选信号后,通过所述第一存储芯片的信号传输线对所述第一存储芯片进行读或写;还被配置为在接收到预设的第二片选信号后,通过所述第二存储芯片的信号传输线对所述第二存储芯片进行读或写。

3、可选的,所述第一存储芯片的信号传输线包括第一地址命令线和第一数据线;所述第二存储芯片的信号传输线包括第二地址命令线和第二数据线;所述多个引脚包括命令引脚组和数据引脚组。

4、可选的,第二地址命令线连接至所述第一地址命令线,所述第二数据线连接至所述第一数据线;所述第一地址命令线连接至所述命令引脚组;所述第一数据线连接至所述数据引脚组。

5、可选的,所述第二地址命令线穿过所述第一存储芯片连接至所述命令引脚组,所述第二数据线穿过所述第一存储芯片连接至所述数据引脚组;所述第一地址命令线连接至所述命令引脚组;所述第一数据线连接至所述数据引脚组。

6、可选的,所述第二地址命令线连接至所述第一地址命令线,所述第二数据线穿过所述第一存储芯片连接至所述数据引脚组;所述第一地址命令线连接至所述命令引脚组;所述第一数据线连接至所述数据引脚组。

7、可选的,所述第一存储芯片设置有第一片选接口和第二片选接口;所述第一片选接口接收所述第一片选信号,以使所述存储结构基于所述第一片选信号通对所述第一存储芯片进行读或写;所述第二片选接口接收所述第二片选信号,以使所述存储结构基于所述第二片选信号对所述第二存储芯片进行读或写。

8、可选的,所述第一存储芯片设置有第一片选接口以及多路选择器,所述多路选择器连接所述第一片选接口以及被配置为接收初始片选信号和控制信号;所述多路选择器被配置为在基于所述控制信号和所述初始片选信号向所述第一片选接口输出第一片选信号,以使所述存储结构基于所述第一片选信号通对所述第一存储芯片进行读或写;所述多路选择器被配置为在基于所述控制信号和所述初始片选信号向所述第一片选接口输出第二片选信号,以使所述存储结构基于所述第二片选信号通对所述第二存储芯片进行读或写。

9、可选的,所述多路选择器包括反相器、第一与门和第二与门;所述反相器的输出端连接所述第一与门的第一输入端,所述反相器的输入端被配置为接入所述控制信号,所述第一与门的第二输入端被配置为接入所述初始片选信号;所述第二与门的第一输入端被配置为接入所述初始片选信号,所述第二与门的第二输入端被配置为接入所述控制信号;所述第一与门的输出端和所述第二与门的输出端均连接所述第一片选接口。

10、可选的,还包括第三存储芯片;所述第三存储芯片堆叠设置在所述第二存储芯片远离所述第一存储芯片的一侧,所述第二存储芯片和所述第三存储芯片之间三维连接;所述第三存储芯片的信号传输线穿过所述第二存储芯片和所述第一存储芯片与所述引脚连接;所述存储结构被配置为在接收到预设的第三片选信号后,通过所述第三存储芯片的信号传输线对所述第三存储芯片进行读或写。

11、第二方面,提供了一种存储器,包括:前述第一方面中任一所述的存储结构;以及逻辑芯片,所述逻辑芯片设置于所述第二存储芯片远离所述第一存储芯片的一侧,且所述逻辑芯片与所述第二存储芯片之间三维连接。

12、本发明实施例中提供的技术方案,至少具有如下技术效果或优点:

13、本发明实施例提供的一种存储结构及存储器,其中存储结构包括:第一存储芯片和第二存储芯片;第一存储芯片堆叠设置在第二存储芯片一侧,第一存储芯片和第二存储芯片之间三维连接;第一存储芯片设置有用于连接至预设的电路板的多个引脚,第一存储芯片的信号传输线与所述引脚连接,第二存储芯片的信号传输线穿过第一存储芯片与引脚连接;存储结构被配置为在接收到预设的第一片选信号后,通过第一存储芯片的信号传输线对第一存储芯片进行读或写;还被配置为在接收到预设的第二片选信号后,通过第二存储芯片的信号传输线对第二存储芯片进行读或写。在本发明实施例的存储结构中通过将第一存储芯片和第二存储芯片进行三维连接,通过第一片选信号和第二片选信号分别对第一存储芯片和第二存储芯片进行读写,实现了存储结构的容量扩展;同时,第二存储芯片的信号传输线穿过第一存储芯片与电路板上的引脚连接,从而节省了电路板布线面积以及引脚占用面积,降低了封装成本及物料成本。

14、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种存储结构,其特征在于,包括:第一存储芯片和第二存储芯片;所述第一存储芯片堆叠设置在所述第二存储芯片一侧,所述第一存储芯片和所述第二存储芯片之间三维连接;所述第一存储芯片设置有用于连接至预设的电路板的多个引脚,所述第一存储芯片的信号传输线与所述引脚连接,所述第二存储芯片的信号传输线穿过所述第一存储芯片与所述引脚连接;

2.根据权利要求1所述的存储结构,其特征在于,所述第一存储芯片的信号传输线包括第一地址命令线和第一数据线;

3.根据权利要求2所述的存储结构,其特征在于,

4.根据权利要求2所述的存储结构,其特征在于,

5.根据权利要求2所述的存储结构,其特征在于,

6.根据权利要求3~5任一项所述的存储结构,其特征在于,

7.根据权利要求3~5任一项所述的存储结构,其特征在于,

8.根据权利要求7所述的存储结构,其特征在于,所述多路选择器包括反相器、第一与门和第二与门;所述反相器的输出端连接所述第一与门的第一输入端,所述反相器的输入端被配置为接入所述控制信号,所述第一与门的第二输入端被配置为接入所述初始片选信号;所述第二与门的第一输入端被配置为接入所述初始片选信号,所述第二与门的第二输入端被配置为接入所述控制信号;所述第一与门的输出端和所述第二与门的输出端均连接所述第一片选接口。

9.根据权利要求1所述的存储结构,其特征在于,还包括第三存储芯片;所述第三存储芯片堆叠设置在所述第二存储芯片远离所述第一存储芯片的一侧,所述第二存储芯片和所述第三存储芯片之间三维连接;所述第三存储芯片的信号传输线穿过所述第二存储芯片和所述第一存储芯片与所述引脚连接;

10.一种存储器,其特征在于,包括:

技术总结

本发明公开了一种存储结构及存储器,其中存储结构包括:第一存储芯片和第二存储芯片;第一存储芯片堆叠设置在第二存储芯片一侧,第一存储芯片和第二存储芯片之间三维连接;第一存储芯片设置有用于连接至预设的电路板的多个引脚,第一存储芯片的信号传输线与引脚连接,第二存储芯片的信号传输线穿过第一存储芯片与引脚连接;存储结构被配置为在接收到预设的第一片选信号后,通过第一存储芯片的信号传输线对第一存储芯片进行读或写;还被配置为在接收到预设的第二片选信号后,通过第二存储芯片的信号传输线对第二存储芯片进行读或写。本发明在实现存储容量扩展的过程中避免了增加PCB板的布线资源,降低了封装成本。

技术研发人员:李乾男,张衍芳

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!