片上系统、指令系统、编译系统及相关产品的制作方法

本披露一般地涉及片上系统(soc)领域。更具体地,本披露涉及一种片上系统、指令处理装置、指令执行方法、编译装置、编译方法、板卡及机器可读存储介质。

背景技术:

1、由于摩尔定律和登纳德缩放定律(dennard scaling)的结束,通用cpu的性能增益持续下跌。领域特定的架构(domain-specific architecture,dsa)成为继续提高整个计算系统的性能和效率的最具前景和可行的方式。dsa迎来了大爆发,其被视为打开了计算机架构的新黄金时代。提出了各种各样的dsa以加速特定应用,例如各种xpu,包括用于数据流处理的dpu、用于图像处理的gpu、用于神经网络的npu、用于张量处理的tpu等。随着越来越多的dsa,尤其是用于计算目的的dsa(也称为ip),被集成到片上系统(soc)中以获得高效率,当前计算系统中硬件的异构性也在持续增长,从标准化变为定制化。

2、当前,ip通常仅暴露ip相关的硬件接口,这迫使soc利用在主机cpu上运行的代码、将ip当做独立的设备进行管理。由于极难直接为应用开发者管理硬件异构性,通常花费大力气构建编程框架以帮助应用开发者管理这种硬件异构性。例如,用于深度学习的流行编程框架包括pytorch、tensorflow、mxnet等,它们都为应用开发者提供了高级、易用的python接口。

3、然而不幸的是,由于较低的生产率和硬件利用率,这种在以cpu为中心的soc中软件管理的异构性妨碍了用户应用在不同的soc上高效地运行。低生产率源于编程框架和应用二者。对于编程框架开发者,为了支持不同的soc,编程框架必须利用不同的ip实现它们各自的高级抽象接口,这需要大量的开发工作。对于应用开发者,soc中不同ip的差异要求同一应用具有不同的实现,导致沉重的编程负担。并且,这对于编程框架不支持的ip而言,情况可能变得甚至更差,因为需要手动管理硬件异构性。低硬件利用率与cpu为中心的soc和具有某些通用性的ip有关。在当前的soc中,主机cpu必须将ip视为独立的设备,并利用在主机cpu上运行的代码(也即,以cpu为中心)来管理不同ip之间的协同,导致控制和数据交换两方面上均存在不可忽略的开销。此外,随着集成很多具有某些通用性的ip,领域特定的编程框架可能无法利用其他领域的可用ip来执行同一功能。例如,使用dla需要在nivdiategra xavier中显式编程。

4、然而,目前很少有研究调查关于增长的硬件异构性导致的编程生产率问题,大部分研究仍然专注于提高单个ip的性能和能源效率。有些工作通过在某些场景中针对基于流的应用按链来调度ip或者在硬件中添加捷径(shortcut)来开发soc性能。还有的提议了一种分形方法来解决编程生产率问题,不过是在不同规模的机器学习加速器上。结果,日益增长的硬件异构性彻底改变了构建未来soc系统的范式,并提出了如何构建具有高生产率和高硬件利用率的soc系统的关键问题。

技术实现思路

1、为了至少部分地解决背景技术中提到的一个或多个技术问题,本披露从多个方面提供了解决方案。一方面,提供了一种新的统一的片上系统架构框架(其可以称为片上系统即处理器,soc-as-a-processor,简称saap),其消除了软件角度的硬件异构性,以提高编程生产率和硬件利用率。另一方面,提供了一种架构自由的混合规模指令集,以支持高生产率和saap的新部件,包括用于片上管理的存储小泡(vesicle),以及用于数据通路的片上互连,从而构建高效的saap架构。再一方面,提供了一种编译方法,用于将各种高级编程语言的程序代码编译成混合规模指令。本披露其他方面还针对指令中的分支预测、异常和中断等方面提供了解决方案。

2、在第一方面中,本披露公开一种片上系统(soc),包括:系统控制器,用于管理硬件流水线,包括从系统内存取回指令、对指令进行译码和分派;以及多个异构ip核,组成所述硬件流水线中的执行单元,用于执行所述系统控制器分派的指令。

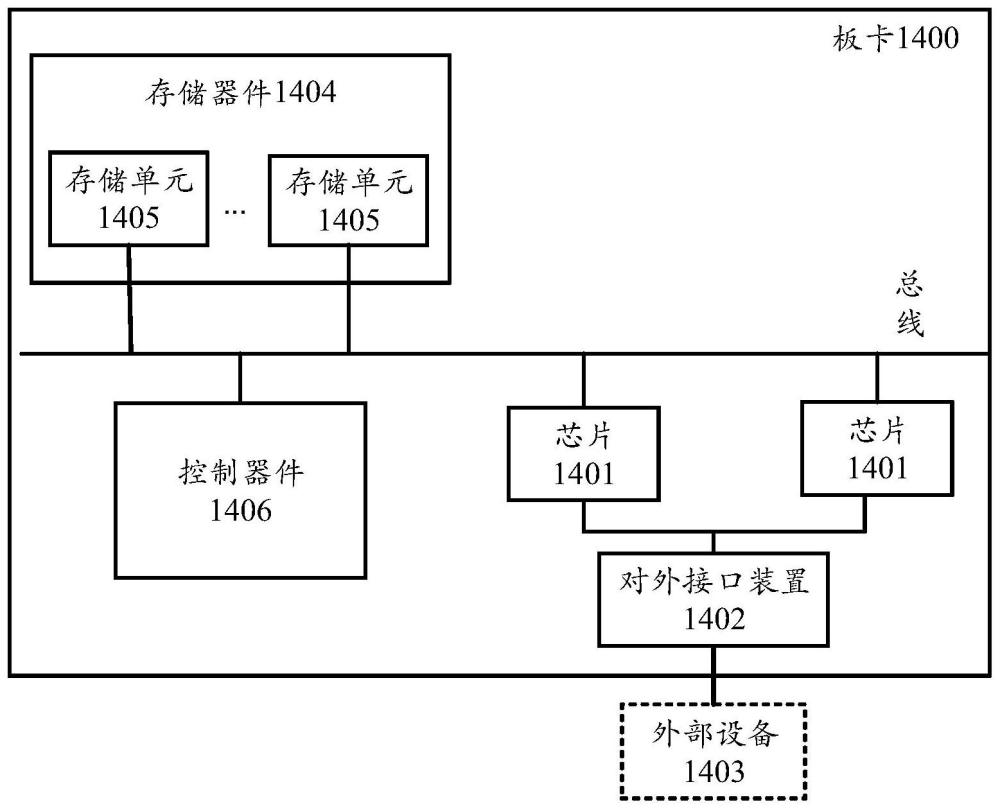

3、在第二方面中,本披露公开一种板卡,包括前述第一方面的片上系统。

4、根据如上提供的片上系统和板卡,可以为具有异构ip核的soc提供一种新的统一的架构,通过将异构ip核视为硬件流水线上的执行单元,可以从软件上隐藏ip核的异构性,从而提高编程效率和硬件利用率。

技术特征:

1.一种片上系统(soc),包括:

2.根据权利要求1所述的片上系统,还包括:

3.根据权利要求2所述的片上系统,其中所述存储小泡的容量大小范围从64b到512kb不等,并且小容量的存储小泡的数量多于大容量的存储小泡的数量。

4.根据权利要求2-3任一所述的片上系统,其中所述多个异构ip核中包括一个母核,所述母核独占式地管理所述系统内存与所述存储小泡之间的数据交换。

5.根据权利要求4所述的片上系统,其中所述母核还用于主控操作系统和运行时,至少负责以下任一或多项:进程管理、页面管理、异常处理和中断处理。

6.根据权利要求5所述的片上系统,其中所述母核进一步用于:

7.根据权利要求6所述的片上系统,其中采用静态预测实现所述分支和预测执行。

8.根据权利要求4-7任一所述的片上系统,还包括:

9.根据权利要求8所述的片上系统,其中所述片上互连包括多个比较器和开关构成的双调排序网络,并且当m个ip核端口需要访问n个存储小泡端口时,利用所述双调排序网络、基于目的地ip核端口的索引对相关的存储小泡端口进行排序,以构建所述m个ip核端口与n个存储小泡端口之间的数据通路。

10.根据权利要求9所述的片上系统,其中所述片上互连包括三个双调排序网络,其中两个用于读出端口,一个用于写入端口。

11.根据权利要求4-10任一所述的片上系统,其中:

12.根据权利要求11所述的片上系统,其中:

13.根据权利要求12所述的片上系统,其中:

14.根据权利要求11-13任一所述的片上系统,其中:

15.根据权利要求2-14任一所述的片上系统,其中所述系统控制器进一步用于利用对所述存储小泡的重命名机制实现以下任一或多项处理:

16.一种板卡,包括根据权利要求1-15任一所述的片上系统。

技术总结

本披露公开了一种片上系统、指令系统、编译系统及相关产品。片上系统可以包括多个异构IP核。本披露的方案通过将异构IP核作为硬件流水线中的执行单元进行管理,可以隐藏IP核的异构性,从而提高编程效率和硬件的利用率。

技术研发人员:请求不公布姓名,请求不公布姓名

受保护的技术使用者:中科寒武纪科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!