一种高精度守时系统的制作方法

1.本发明涉及时钟系统技术领域,具体为一种高精度守时系统。

背景技术:

2.目前,普通授时卡一般采用多种授时方式实现多种情况下授时的精度和稳定性,例如增加gnss、4g、内置时钟芯片等方式,为此研发出一种高精度守时系统。

3.在现有的高精度守时系统中,守时系统增加gnss、4g、内置时钟芯片,此种方式在gnss信号质量高时可以保证授时精度和稳定性,在gnss信号质量不高时,需要依赖4g来网络授时,甚至如果4g信号质量不佳,需要内置时钟芯片来保证授时稳定性。由于技术和成本限制4g信号质量以及内置时钟芯片授时误差一般在毫秒级别,严重降低了整体系统的授时精度,为此我们设计此高精度守时系统。

技术实现要素:

4.针对现有高精度守时系统的不足,本发明提供了一种高精度守时系统,具备恒温晶振通过优异的软硬件设计,提高整个系统的授时精度和稳定性的优点,解决了上述背景技术中提出的问题。

5.本发明提供如下技术方案:一种高精度守时系统,包括fpga控制器,所述fpga控制器内部系统包含有4g模块、rtc时钟、gnss模块、驯服时钟、电源和pcie接口,4g模块和rtc时钟相互连接并与fpga控制器连接,所述驯服时钟的内部分别与fpga控制器和驯服时钟连接,所述fpga控制器内部的结构包含有恒温晶振、分频器、相位比较器组成,所述fpga控制器的外部连接有pcie接口。

6.优选的,所述恒温晶振输出随温度变化比较小的时钟脉冲信号,输出到分频器,所述分频器的输出通过相位比较器反馈到恒温晶振上对输入信号进行正反馈调节。

7.优选的,fpga控制器是可编程逻辑门阵列,区别于普通的单片机嵌入式处理器,fpga控制器内部由逻辑门构成,输入信号可以迅速通过逻辑门传递处理,做出响应,而单片机嵌入式处理器。

8.优选的,所述fpga控制器采用可以对输入信号进行迅速处理。

9.优选的,所述gnss模块主要实现精确授时,gnss模块下发的时间可以保证时间精度。

10.优选的,所述rtc时钟则提供最基本的时间功能,当gnss模块和4g模块都无法工作时,可以提供兜底的时间策略。

11.优选的,计算出时间以后通过pci-e接口发送到pc端,提供至pc端。

12.与现有高精度守时系统对比,本发明具备以下有益效果:

13.该高精度守时系统,通过本方案使用恒温晶振通过优异的软硬件设计,对晶振输出频率进行驯服,保证在gnss信号质量不佳时也能稳定地提供时钟脉冲信号,从而提高整个系统的授时精度和稳定性。

附图说明

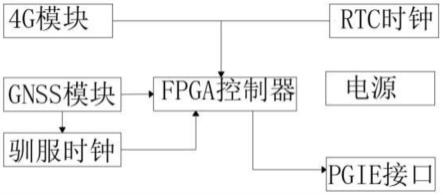

14.图1为本发明守时系统内部整体结构示意图;

15.图2为本发明驯服时钟示意图。

具体实施方式

16.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.请参阅图1和图2,一种高精度守时系统,包括fpga控制器,fpga控制器内部系统包含有4g模块、rtc时钟、gnss模块、驯服时钟、电源和pcie接口,4g模块对信号进行传导,rtc时钟对信息进行显示,方便对时间进行观察,驯服时钟对时钟进行驯服,增加信号接收时的均匀性,4g模块和rtc时钟相互连接并与fpga控制器连接,驯服时钟的内部分别与fpga控制器和驯服时钟连接,fpga控制器内部的结构包含有恒温晶振、分频器、相位比较器组成,fpga控制器的外部连接有pcie接口,通过fpga控制器与pcie接口,即可携带信号进行传输。

18.参考图2,恒温晶振输出随温度变化比较小的时钟脉冲信号,输出到分频器,分频器的输出通过相位比较器反馈到恒温晶振上对输入信号进行正反馈调节,通过恒温晶振输出随温度变化比较小的时钟脉冲信号,同时输出至分频器,同时分频器的输出利用恒温晶振,即确保信号输出时增加信号传输的稳定性。

19.参考图1,fpga控制器是可编程逻辑门阵列,区别于普通的单片机嵌入式处理器,fpga控制器内部由逻辑门构成,输入信号可以迅速通过逻辑门传递处理,做出响应,而单片机嵌入式处理器,通过信号可经过fpga快速地经过逻辑门传递信号,同时单片机的内部嵌入有处理器,即增加新高传递的精准性能。

20.参考图1,fpga控制器采用可以对输入信号进行迅速处理,通过fpga控制器采用可以对信号进行处理后,即fpga控制器可携带信号传输增加精准性。

21.参考图1,gnss模块主要实现精确授时,gnss模块下发的时间可以保证时间精度,通过采用gnss模块,在gnss模块下发的时间可确保精度,当gnss模块失效或者gnss信号质量不佳时,可以使用4g模块来进行网络授时,从而消除本地时钟的累计误差。

22.参考图1,rtc时钟则提供最基本的时间功能,当gnss模块和4g模块都无法工作时,可以提供兜底的时间策略,通过gnss模块和4g模块提供兜底的时间策略,即本方案中加入驯服时钟作为时钟源,可以在gnss模块和4g模块失效的情况下消除时钟rtc时钟的累计误差。

23.参考图2,计算出时间以后通过pci-e接口发送到pc端,提供至pc端,通过计算出时间后经过pci-e接口发送到pc端,即可经过pc端对时间信息进行观察。

24.工作原理:使用时,通过采用驯服时钟+fpga控制器的方案,实现高精度守时要求。驯服时钟内部由恒温晶振以及补偿电路组成,其会输出一个高精度时钟脉冲,连接到fpga内部,得益于fpga硬件机制,接收到高精度时钟脉冲以后,会在纳秒级时间内对信号进行处理,对信号进行累计,并计算总的脉冲个数,即可算出时间间隔,整个系统经过标准时钟源标定,可以保证脉冲精度保持毫秒级年误差。

25.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

技术特征:

1.一种高精度守时系统,包括fpga控制器,其特征在于:所述fpga控制器内部系统包含有4g模块、rtc时钟、gnss模块、驯服时钟、电源和pcie接口,4g模块和rtc时钟相互连接并与fpga控制器连接,所述驯服时钟的内部分别与fpga控制器和驯服时钟连接,所述fpga控制器内部的结构包含有恒温晶振、分频器、相位比较器组成,所述fpga控制器的外部连接有pcie接口。2.根据权利要求1所述的一种高精度守时系统,其特征在于:所述恒温晶振输出随温度变化比较小的时钟脉冲信号,输出到分频器,所述分频器的输出通过相位比较器反馈到恒温晶振上对输入信号进行正反馈调节。3.根据权利要求1所述的一种高精度守时系统,其特征在于:fpga控制器是可编程逻辑门阵列,区别于普通的单片机嵌入式处理器,fpga控制器内部由逻辑门构成,输入信号可以迅速通过逻辑门传递处理,做出响应,而单片机嵌入式处理器。4.根据权利要求1所述的一种高精度守时系统,其特征在于:所述fpga控制器采用可以对输入信号进行迅速处理。5.根据权利要求1所述的一种高精度守时系统,其特征在于:所述gnss模块主要实现精确授时,gnss模块下发的时间可以保证时间精度。6.根据权利要求1所述的一种高精度守时系统,其特征在于:所述rtc时钟则提供最基本的时间功能,当gnss模块和4g模块都无法工作时,可以提供兜底的时间策略。7.根据权利要求6所述的一种高精度守时系统,其特征在于:计算出时间以后通过pci-e接口发送到pc端,提供至pc端。

技术总结

本发明涉及时钟系统技术领域,且公开了一种高精度守时系统,包括FPGA控制器,所述FPGA控制器内部系统包含有4G模块、RTC时钟、GNSS模块、驯服时钟、电源和PCIE接口,4G模块和RTC时钟相互连接并与FPGA控制器连接,所述驯服时钟的内部分别与FPGA控制器和驯服时钟连接,所述FPGA控制器内部的结构包含有恒温晶振、分频器、相位比较器组成,所述FPGA控制器的外部连接有PCIE接口。该高精度守时系统,通过本方案使用恒温晶振通过优异的软硬件设计,对晶振输出频率进行驯服,保证在GNSS信号质量不佳时也能稳定地提供时钟脉冲信号,从而提高整个系统的授时精度和稳定性。的授时精度和稳定性。的授时精度和稳定性。

技术研发人员:武迪 刘磊

受保护的技术使用者:中安云科科技发展(山东)有限公司

技术研发日:2022.07.21

技术公布日:2022/10/4

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1