一种多核数据处理器DPU实现装置和实现方法与流程

本发明涉及ai以及芯片soc设计领域,具体涉及一种多核数据处理器dpu实现装置和实现方法。

背景技术:

1、根据冯诺依曼架构,计算机典型的架构是以一个以计算和存储为核心的架构,cpu作为处理器单元,负责完成各种算术和逻辑计算;而内存(运存)和硬盘(外部存储),负责存储数据,与cpu交互。

2、传统cpu解决方案主要会在2个大的场景中存在限制:一个是专用计算场景,另一个是海量数据i/o场景。

3、我们知道cpu的定位是进行通用计算,而在某些特定的领域计算里面不适用。例如:ai/ml领域采用gpu的并行计算,密码学安全领域和通信设备领域采用fpga的可编程空间计算。因为cpu不擅长特定领域,但专注于领域的需求又不断增长,所以近几年来dsa/dsl(领域专用架构/领域专用语言)得到了蓬勃发展。

4、再来就是我们知道cpu是计算密集型芯片,它的带宽取决于北桥总线,i/o性能是面向main memory的,而不是面向ports(网络端口)的。所以我们说cpu不是i/o密集型芯片。在这样的定位下,cpu面对数据洪流环境的时候就显得力不从心了。

5、因此主要功能为卸载、加速和隔离的dpu应运而生了,把cpu的部分工作卸载到自己身上;利用自己的算力特长,对这些工作进行加速运算;整个过程,实现了计算的隔离。

技术实现思路

1、本发明所要解决的技术问题是提供一种多核数据处理器dpu实现装置和实现方法。

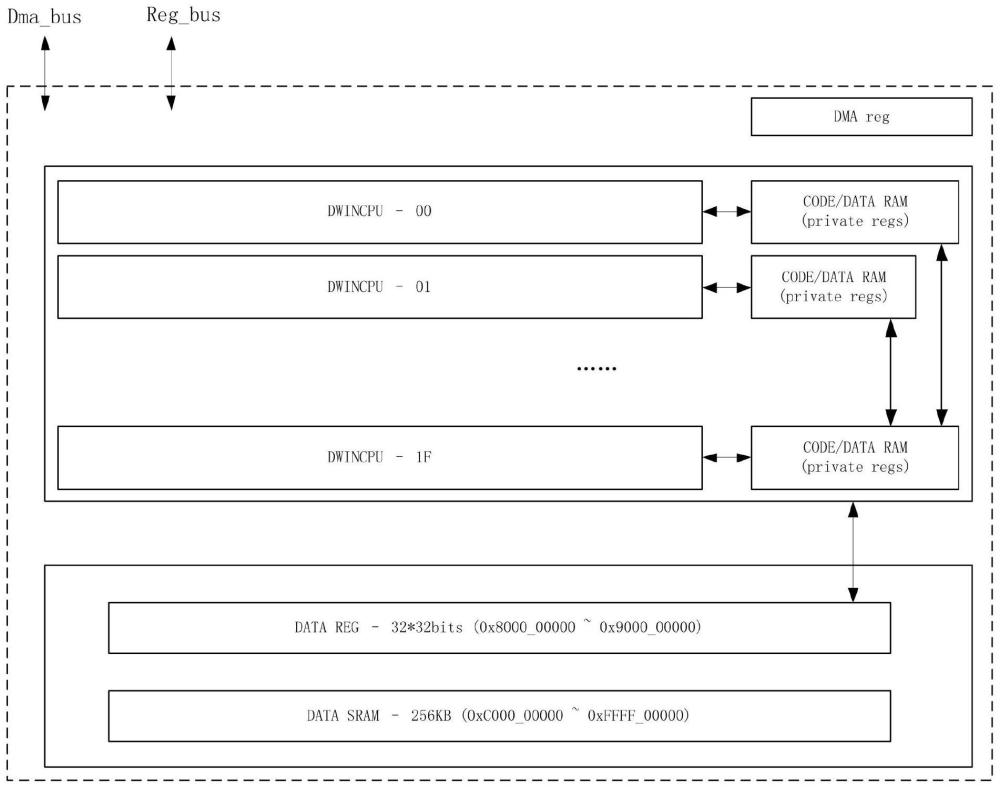

2、本发明解决上述技术问题的技术方案装置如下:一种多核数据处理器dpu实现装置包含32个处理器dwincpu-xx、共享数据ram即code/data ram(private reg)、dma寄存器dma reg、dma总线dma_bus、寄存器总线reg_bus。

3、进一步,所述dwincpu-xx是包含了32个完全相同并且独立的处理器;

4、进一步,所述dwincpu-xx是从指按照dwincpu-00、dwincpu-02等按照十六进制编码的方式来编号的,其最后一位是dwincpu-1f;

5、进一步,所述每一个dwincpu-xx均与对应的独立的code/data ram(privateregs)相连接;

6、进一步,所述dwincpu-xx的处理器代码和数据存储在code/data ram(privateregs)中;

7、进一步,所述dwincpu-xx的处理器所匹配的代码和数据code/data ram(privateregs)均可由外部处理器在初始化该dpu的时候把代码和数据通过dma_bus以及dma reg进行数据的存放;

8、进一步,所述dwincpu-xx的处理器可以根据各自的代码各自独立运行;

9、进一步,所述dwincpu-xx的处理器可以通过独立的code/data ram(privateregs)相互之间进行通信,实现多核cpu的同步。

10、进一步,所述dwincpu-xx的处理器公用共享数据ram即code/data ram(privateregs)。当这些dwincpu-xx要协同处理比较大的数据时,可以使用这些共享数据ram即code/data ram(private regs)空间为所有dwincpu-xx提供数据。

11、采用上述步骤的有益效果是:通过32个dwincpu可实现dpu的基础功能即数据运算,而且多核可以通过独立的私有寄存器实现多核连动,同步运算加快数据的处理速度。

12、进一步,所述共享数据ram即code/data ram(private regs)与对应的dwincpu-xx相连接;

13、进一步,所述共享数据ram即code/data ram(private regs)与其其他额外的code/data ram(private regs)相连接;

14、进一步,所述共享数据ram即code/data ram(private regs)是32个完全相同的;

15、进一步,所述共享数据ram即code/data ram(private regs)是既包括code/data的ram又包含了private regs私有寄存器;

16、进一步,所述共享数据ram即code/data ram(private regs)是包含了data reg-32*32bit(0x8000_00000~0x9000_00000),即32*32bit的寄存器;

17、进一步,所述共享数据ram即code/data ram(private regs)是包含了data sram-256kb(0xc000_00000~0xffff_00000),即256k的sram;

18、采用上述步骤的有益效果是:通过dma寄存器dma reg以及data sram实现了cpu的数据存储功能,并同时由于reg以及sram实现了不同cpu的通信,进而实现了多核同步运算以及交互。

19、进一步,所述dma寄存器dma reg是dpu的dma寄存器接口,外界soc可以通过dmareg进行寄存器的交互;

20、进一步,所述dma总线dma_bus是实现整个芯片与dpu的数据交互的总线;

21、进一步,所述寄存器总线reg_bus是外部soc通过reg_bus来对dpu进行配置控制逻辑;

22、采用上述步骤的有益效果是:dpu还给整个设计提供控制逻辑接口,当整个芯片设计要调用dpu时,可以通过reg_bus总线配置控制逻辑。控制逻辑则通过dma_bus实现整个芯片与dcpu的数据搬移。

23、一种多核数据处理器dpu的实现方法,包括以下步骤:

24、步骤1:soc通知dpu通过dma_bus把数据存放dwincpu-xx的code/data ram中;

25、步骤2:dwincpu-xx把数据计算完成以后,把数据存放在code/data ram中;

26、步骤3:dpu通过dma_bus把code/data ram的数据转运到soc中;

27、采取以上步骤的有益效果是:针对硬件减速要求比较高的加速模块譬如fft、卷积、矩阵乘法可以实现每一个微处理器都能进行分割同步计算实现最快速的数据处理功能。

技术特征:

1.一种多核数据处理器dpu实现装置,其特征在于,包含32个处理器dwincpu-xx、共享数据ram即code/data ram(private reg)、dma寄存器dma reg、dma总线dma_bus、寄存器总线reg_bus。

2.根据权利要求1所述的一种多核数据处理器dpu实现装置,其特征在于,dwincpu-xx是包含了32个完全相同并且独立的处理器;所述dwincpu-xx是从指按照dwincpu-00、dwincpu-02等按照十六进制编码的方式来编号的,其最后一位是dwincpu-1f;所述每一个dwincpu-xx均与对应的独立的code/data ram(private regs)相连接;所述dwincpu-xx的处理器代码和数据存储在code/data ram(private regs)中;所述dwincpu-xx的处理器所匹配的代码和数据code/data ram(private regs)均可由外部处理器在初始化该dpu的时候把代码和数据通过dma_bus以及dma reg进行数据的存放;所述dwincpu-xx的处理器可以根据各自的代码各自独立运行;所述dwincpu-xx的处理器可以通过独立的code/data ram(private regs)相互之间进行通信,实现多核cpu的同步;所述dwincpu-xx的处理器公用共享数据ram即code/data ram(private regs);当这些dwincpu-xx要协同处理比较大的数据时,可以使用这些共享数据ram即code/data ram(private regs)空间为所有dwincpu-xx提供数据。

3.根据权利要求1所述的一种多核数据处理器dpu实现装置,其特征在于,所述共享数据ram即code/data ram(private regs)与对应的dwincpu-xx相连接;所述共享数据ram即code/data ram(private regs)与其其他额外的code/data ram(private regs)相连接;所述共享数据ram即code/data ram(private regs)是32个完全相同的;所述共享数据ram即code/data ram(private regs)是既包括code/data的ram又包含了private regs私有寄存器;所述共享数据ram即code/data ram(private regs)是包含了data reg-32*32bit(0x8000_00000~0x9000_00000),即32*32bit的寄存器;所述共享数据ram即code/dataram(private regs)是包含了data sram-256kb(0xc000_00000~0xffff_00000),即256k的sram。

4.根据权利要求1所述的一种多核数据处理器dpu实现装置,其特征在于,所述dma寄存器dma reg是dpu的dma寄存器接口,外界soc可以通过dma reg进行寄存器的交互。

5.根据权利要求1所述的一种多核数据处理器dpu实现装置,其特征在于,所述dma总线dma_bus是实现整个芯片与dpu的数据交互的总线。

6.根据权利要求1所述的一种多核数据处理器dpu实现装置,其特征在于,所述寄存器总线reg_bus是外部soc通过reg_bus来对dpu进行配置控制逻辑。

7.一种多核数据处理器dpu的实现方法,其特征在于,包括以下步骤:

技术总结

本发明涉及一种多核数据处理器DPU实现装置包含32个处理器DWI NCPU‑XX、共享数据RAM即CODE/DATA RAM(pr i vate reg)、DMA寄存器DMA reg、Dma总线Dma_bus、寄存器总线Reg_bus;一种多核数据处理器DPU的实现方法,包括以下步骤:SOC通知DPU通过Dma_bus把数据存放DWI NCPU‑XX的CODE/DATARAM中;DWI NCPU‑XX把数据计算完成以后,把数据存放在CODE/DATA RAM中;DPU通过Dma_bus把CODE/DATA RAM的数据转运到SOC中;本发明针对硬件减速要求比较高的加速模块譬如FFT、卷积、矩阵乘法可以实现每一个微处理器都能进行分割同步计算实现最快速的数据处理功能。

技术研发人员:刘华平

受保护的技术使用者:湖南迪文科技有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!