硬件加密模块、芯片及加密方法与流程

本发明涉及集成电路设计领域,特别是涉及一种硬件加密模块、芯片及加密方法。

背景技术:

1、随着近年来信息安全的概念被社会各界广泛提及,芯片的加密功能作为用户保护自身产品数据安全的一种直接而有效的途径,越来越得到重视。

2、软件加密方法凭借其实现简单的特性,被广泛应用;现有的软件加密一般为在芯片存储区域固定位置增加加密标识,若加密标识有效,则烧录器要么直接不作读取动作直接返回加密数值,要么依然读取但是返回值还是加密数值;这种软件加密方式非常容易被破解,安全性极低,同时存在速度慢、占用存储资源等缺点。

3、硬件加密的实现具有加密速度快、硬件安全性好、不占用存储资源、使用方便等特点,有效的弥补了软件加密方法的不足,更好的保护了芯片内的软件知识产权,避免被抄袭的风险。但是目前硬件加密仍存在被强行解密进而泄密的风险。

4、因此,如何加强硬件加密的安全性,已成为本领域技术人员亟待解决的技术问题之一。

5、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种硬件加密模块、芯片及加密方法,用于解决现有技术中硬件加密安全性不足的问题。

2、为实现上述目的及其他相关目的,本发明提供一种硬件加密模块,所述硬件加密模块至少包括:

3、控制单元及存储单元,所述存储单元包括程序区及数据区;

4、所述控制单元连接所述存储单元,并接收外部指令,基于所述存储单元的加密位地址中的加密值判断加密状态,并基于外部擦除指令产生控制所述存储单元擦除的控制时序,基于所述加密状态及外部读写指令产生控制所述存储单元读写的控制时序;其中,在处于加密模式时,仅对所述程序区加密读出并禁止对所述加密位地址进行写入操作。

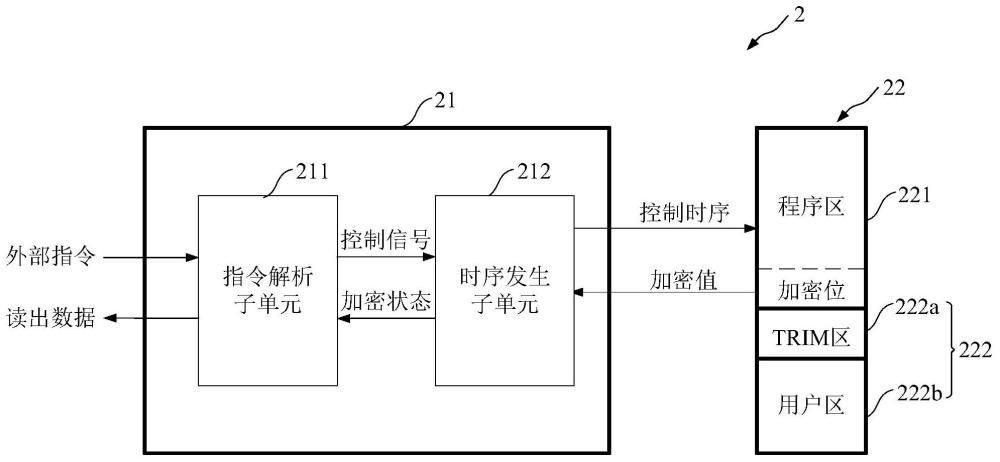

5、可选地,所述控制单元包括指令解析子单元及时序发生子单元;

6、所述指令解析子单元连接所述时序发生子单元,基于外部擦除指令产生程序区擦除控制信号或数据区擦除控制信号,并基于所述加密状态及所述外部读写指令产生读写控制信号;

7、所述时序发生子单元连接所述存储单元及所述指令解析子单元,基于所述加密位地址中的加密值判断加密状态,并基于所述指令解析子单元输出的控制信号产生所述存储单元的控制时序。

8、更可选地,所述指令解析子单元包括地址判断部及控制信号产生部;

9、所述地址判断部对所述外部读写指令中的地址进行判断;

10、所述控制信号产生部连接于所述地址判断部及所述时序发生子单元的输出端,基于外部擦除指令产生擦除控制信号,基于所述外部读写指令、所述地址判断部的判断结果及所述加密状态产生对应读写控制信号。

11、更可选地,所述时序发生子单元包括加密状态判断部及控制时序产生部;

12、所述加密状态判断部连接所述存储单元,基于所述加密位地址中的加密值与预设值的比较结果对所述加密状态进行判断;

13、所述控制时序产生部连接于所述指令解析子单元的输出端,基于所述指令解析子单元输出的控制信号产生所述存储单元的控制时序。

14、可选地,所述数据区包括trim区域及用户区域。

15、更可选地,所述加密位地址位于所述程序区内。

16、更可选地,所述加密位地址位于所述程序区底部。

17、为实现上述目的及其他相关目的,本发明还提供一种芯片,所述芯片至少包括:上述硬件加密模块。

18、为实现上述目的及其他相关目的,本发明还提供一种加密方法,所述加密方法至少包括:

19、上电后获取加密位地址中的加密值,基于所述加密位地址中的加密值判断并更新加密状态;

20、当接收到外部擦除指令时,基于所述外部擦除指令产生程序区擦除控制信号或数据区擦除控制信号,并基于所述程序区擦除控制信号对整个程序区进行擦除或基于所述数据区擦除控制信号对整个数据区进行擦除;

21、当接收到外部写入指令时,对加密状态及要执行写入操作的地址进行判断,若在加密模式下要执行写入操作的地址为加密位地址,则禁止写入;否则基于所述外部写入指令对存储单元中对应地址进行写入操作;

22、当接收到外部读出指令时,对所述加密状态及要执行读出操作的地址进行判断,若在加密模式下要执行读出操作的地址位于所述存储单元的程序区,则读出对应地址中的加密值;否则基于所述外部读出指令对所述存储单元中对应地址中的实际值进行读出操作。

23、更可选地,所述加密位地址位于所述程序区底部。

24、可选地,判断加密状态的方法包括:将所述加密位地址中的加密值与预设值进行比较,若两者匹配则处于加密模式,反之则处于解密模式。

25、如上所述,本发明的硬件加密模块、芯片及加密方法,具有以下有益效果:

26、1、本发明的硬件加密模块、芯片及加密方法在擦除模式下,设置程序区擦除和数据区擦除两种方式,在满足用户使用场景的同时,简化了操作流程;同时将加密位地址设置在程序区内,用户在擦除加密位的同时必须将程序全部擦除,防止通过单独擦除加密位导致的强制解密情况。

27、2、本发明的硬件加密模块、芯片及加密方法在写入模式下,对加密状态及地址进行判定,在加密状态下用户无法对加密位地址进行写入操作,防止通过改写加密位数据的方式进行强行解密。

28、3、本发明的硬件加密模块、芯片及加密方法在读出模式下,对加密状态及地址进行判定,数据区不受加密状态影响,在任何时候都可以读到正确数据;程序区在解密状态下可以被正确读取,否则读出对应地址中的加密值。

29、4、本发明的硬件加密模块、芯片及加密方法舍弃超级读出模式(无论是否处于加密模式,程序区和数据区均可被正确读出),有效提高芯片的安全性。

30、5、本发明的硬件加密模块、芯片及加密方法中所有烧录指令(或烧录协议)均可以公开,方便用户开发自己的烧录工装,大大提高产品的应用灵活性;同时严密的加密逻辑可以很好的保护程序区的软件,将被解密读取的可能降到最低。

技术特征:

1.一种硬件加密模块,其特征在于,所述硬件加密模块至少包括:

2.根据权利要求1所述的硬件加密模块,其特征在于:所述控制单元包括指令解析子单元及时序发生子单元;

3.根据权利要求2所述的硬件加密模块,其特征在于:所述指令解析子单元包括地址判断部及控制信号产生部;

4.根据权利要求2所述的硬件加密模块,其特征在于:所述时序发生子单元包括加密状态判断部及控制时序产生部;

5.根据权利要求1所述的硬件加密模块,其特征在于:所述数据区包括trim区域及用户区域。

6.根据权利要求1-5任意一项所述的硬件加密模块,其特征在于:所述加密位地址位于所述程序区内。

7.根据权利要求6所述的硬件加密模块,其特征在于:所述加密位地址位于所述程序区底部。

8.一种芯片,其特征在于,所述芯片至少包括:如权利要求1-7任意一项所述的硬件加密模块。

9.一种加密方法,其特征在于,所述加密方法至少包括:

10.根据权利要求9所述的加密方法,其特征在于:所述加密位地址位于所述程序区底部。

11.根据权利要求9或10所述的加密方法,其特征在于:判断加密状态的方法包括:将所述加密位地址中的加密值与预设值进行比较,若两者匹配则处于加密模式,反之则处于解密模式。

技术总结

本发明提供一种硬件加密模块、芯片及加密方法,包括:控制单元及存储单元;控制单元连接存储单元,并接收外部指令,基于存储单元的加密位地址中的加密值判断加密状态,并基于外部擦除指令产生控制存储单元擦除的控制时序,基于加密状态及外部读写指令产生控制存储单元读写的控制时序;其中,在处于加密模式时,仅对程序区加密读出并禁止对加密位地址进行写入操作。本发明所有加密行为只对所述程序区有效,对数据区无效;防止用户通过直接擦除加密位地址并重新上电进行强行解密;防止用户通过对加密位地址重新写入并上电进行强行解密;舍弃超级读取模式,有效提高芯片的安全性;产品的应用灵活性高、安全性高。

技术研发人员:孙军,陈佳俊,沈天平,郭佳敏

受保护的技术使用者:华润微集成电路(无锡)有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!