为跨多个DMA引擎调度的部分传送计算认证标签的制作方法

至少一个实施例涉及用于执行和促进保密数据传送的处理资源。例如,至少一个实施例涉及用于为跨直接存储器访问(dma)引擎调度的部分传送计算认证标签的硬件电路。

背景技术:

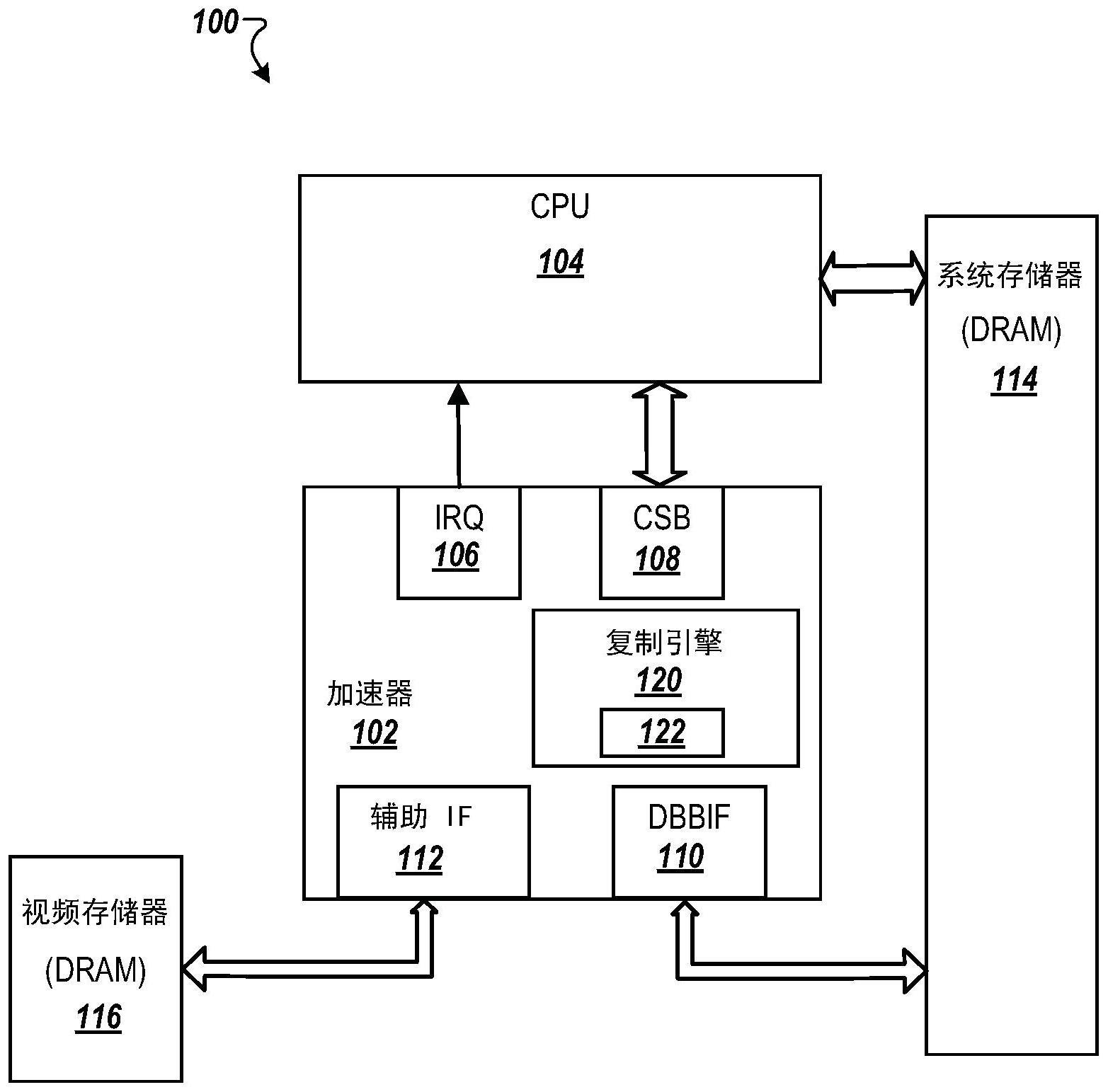

1、加速器电路包括直接存储器访问(dma)电路,以独立于中央处理单元(cpu)来访问系统存储器。dma电路还可用于存储器内或存储器之间的数据的存储器到存储器(memory-to-memory)的复制或移动。当需要保护数据时,dma电路可以实现密码电路(cryptographiccircuit)来加密和解密从安全存储器复制的数据以及复制到安全存储器的数据。多个dma引擎可用于高速互连(例如,2.4tb/s带宽、300gb/s双向带宽)以实现极高的数据传送率。大型传送可以拆分成多个数据段并调度到多个dma引擎以使存储器或链路带宽饱和。然而,当需要对传送的数据进行保密时,在多个dma引擎之间以如此高的速度生成认证标签(authentication tag)仍然是一个挑战。特别地,认证标签的生成本质上是一种顺序的乘加操作,并且多个dma引擎可以在物理上彼此远离。一些实施方案通过为加密数据流中的每个块(block)(拆分(split))创建认证标签并使用单独的初始化向量(iv)来独立认证每个拆分。然而,这增加了使用密码硬件(cryptographic hardware)的存储器占用空间,并且需要在软件驱动程序堆栈上进行额外的工作来管理和认证每个拆分。其他实施方案使用一个或多个额外的密码硬件引擎进行认证计算,但这会产生额外的面积开销。

技术实现思路

技术特征:

1.一种加速器电路,包括:

2.如权利要求1所述的加速器电路,其中所述dma电路还包括伽罗瓦域gf乘法器,其中所述dma电路用于使用所述gf乘法器至少基于所述部分传送集合的拆分大小和所述多个dma引擎的数量来计算多个乘数指数。

3.如权利要求2所述的加速器电路,其中所述逻辑dma引擎被分配用于所述第一数据传送的第一加密密钥和第一初始化向量iv,其中所述逻辑dma引擎用于将所述第一加密密钥和第一iv与所述多个dma引擎进行上下文绑定。

4.如权利要求3所述的加速器电路,其中所述dma电路用于在所述第一加密密钥和所述第一iv与所述多个dma引擎进行所述上下文绑定的延迟期间计算所述多个乘数指数。

5.如权利要求3所述的加速器电路,其中所述多个dma引擎中的每一者用于接收所述逻辑dma引擎的块计数器的值,其中所述块计数器针对调度到所述多个dma引擎中的一者的所述部分传送集合中的每一者而递增,其中所述多个dma引擎中的每一者用于至少使用所述第一加密密钥、所述第一iv、所述块计数器的值来生成用于相应的部分传送的加密数据以及用于计算针对所述相应的部分传送的长度的部分认证标签。

6.如权利要求1所述的加速器电路,其中所述编排电路用于:

7.如权利要求1所述的加速器电路,其中所述第一缓冲器是第一先进先出fifo缓冲器,并且所述第二缓冲器是第二fifo缓冲器。

8.如权利要求1所述的加速器电路,其中所述第一调整指数是乘数指数,所述乘数指数是部分传送的拆分大小和所述多个dma引擎的数量的函数。

9.如权利要求1所述的加速器电路,其中所述逻辑dma引擎使用轮询仲裁方案将所述部分传送集合调度到所述多个dma引擎。

10.如权利要求1所述的加速器电路,其中所述经认证的加密算法是高级加密标准伽罗瓦计数器模式aes-gcm。

11.如权利要求1所述的加速器电路,其中所述加速器电路是图形处理单元gpu、深度学习加速器dla电路、智能处理单元ipu、神经处理单元npu、张量处理单元tpu、神经网络处理器nnp、数据处理单元dpu、视觉处理单元vpu、专用集成电路asic或现场可编程门阵列fpga。

12.一种操作加速器电路的方法,所述方法包括:

13.如权利要求12所述的方法,进一步包括,在所述第一轮期间:

14.如权利要求13所述的方法,进一步包括,在第二轮期间:

15.如权利要求13所述的方法,进一步包括:在所述第一轮期间,使用伽罗瓦域gf乘法器,至少基于所述部分传送集合的拆分大小和所述多个dma引擎的数量来计算多个乘数指数。

16.如权利要求15所述的方法,进一步包括执行上下文绑定过程以将第一加密密钥和第一初始化向量iv递送到所述多个dma引擎,其中计算所述多个乘数指数是在所述上下文绑定期间完成的。

17.如权利要求15所述的方法,其中确定所述认证标签进一步包括使用与所述第一数据传送相关联的第一初始化向量iv对所述组合认证标签进行加密以获取用于所述第一数据传送的所述认证标签。

18.一种加速器电路,包括:

19.如权利要求16所述的加速器电路,其中所述加速器电路是图形处理单元gpu、深度学习加速器dla电路、智能处理单元ipu、神经处理单元npu、张量处理单元tpu、神经网络处理器nnp、数据处理单元dpu、视觉处理单元vpu、专用集成电路asic或现场可编程门阵列fpga。

20.如权利要求16所述的加速器电路,其中所述ce包括:

技术总结

本申请涉及为跨多个DMA引擎调度的部分传送计算认证标签。描述了用于当数据传送被调度为跨指定数量的直接存储器访问(DMA)引擎的部分传送时计算数据传送的认证标签的设备、系统和技术。在一轮或更多轮期间,编排电路存储由DMA引擎计算的部分认证标签,以及对应调整指数,其中部分传送由指定数量的DMA引擎调度和处理。在最后一轮期间,可以基于部分认证标签和编排电路在各轮期间存储的对应调整指数来计算组合认证标签。

技术研发人员:V·库尔卡尼,N·切鲁库里,R·汪,A·亨德里克森,G·特努什戈迪,W·甘地

受保护的技术使用者:辉达公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!