基于位单元架构的存内计算的制作方法

本公开整体涉及存储器阵列,诸如学习机/推理机(例如,人工神经网络(ann))中使用的存储器阵列。

背景技术:

1、已知的计算机视觉、语音识别和信号处理应用受益于诸如深度卷积神经网络(dcnn)的学习机/推理机的使用。dcnn是基于计算机的工具,其处理大量的数据,并且通过合并邻近的数据内的相关特征,对数据进行广泛的预测,以及基于可靠的结论和新的合并来改进预测,从而自适应地“学习”。dcnn被布置在多个“层”中,并且在每一层进行不同类型的预测。

2、例如,如果提供面部的多个二维图片作为dcnn的输入,则dcnn将学习面部的各种特征,诸如边缘、曲线、角度、点、颜色对比度、亮点、暗点等。这些一个或多个特征在dcnn的一个或多个第一层处被学习。然后,在一个或多个第二层中,dcnn将学习面部的各种可识别特征,诸如眼睛、眉毛、前额、头发、鼻子、嘴、脸颊等;每个特征与所有其它特征是可区分的。也就是说,dcnn学习识别并区分眼睛与眉毛或任何其它面部特征。

技术实现思路

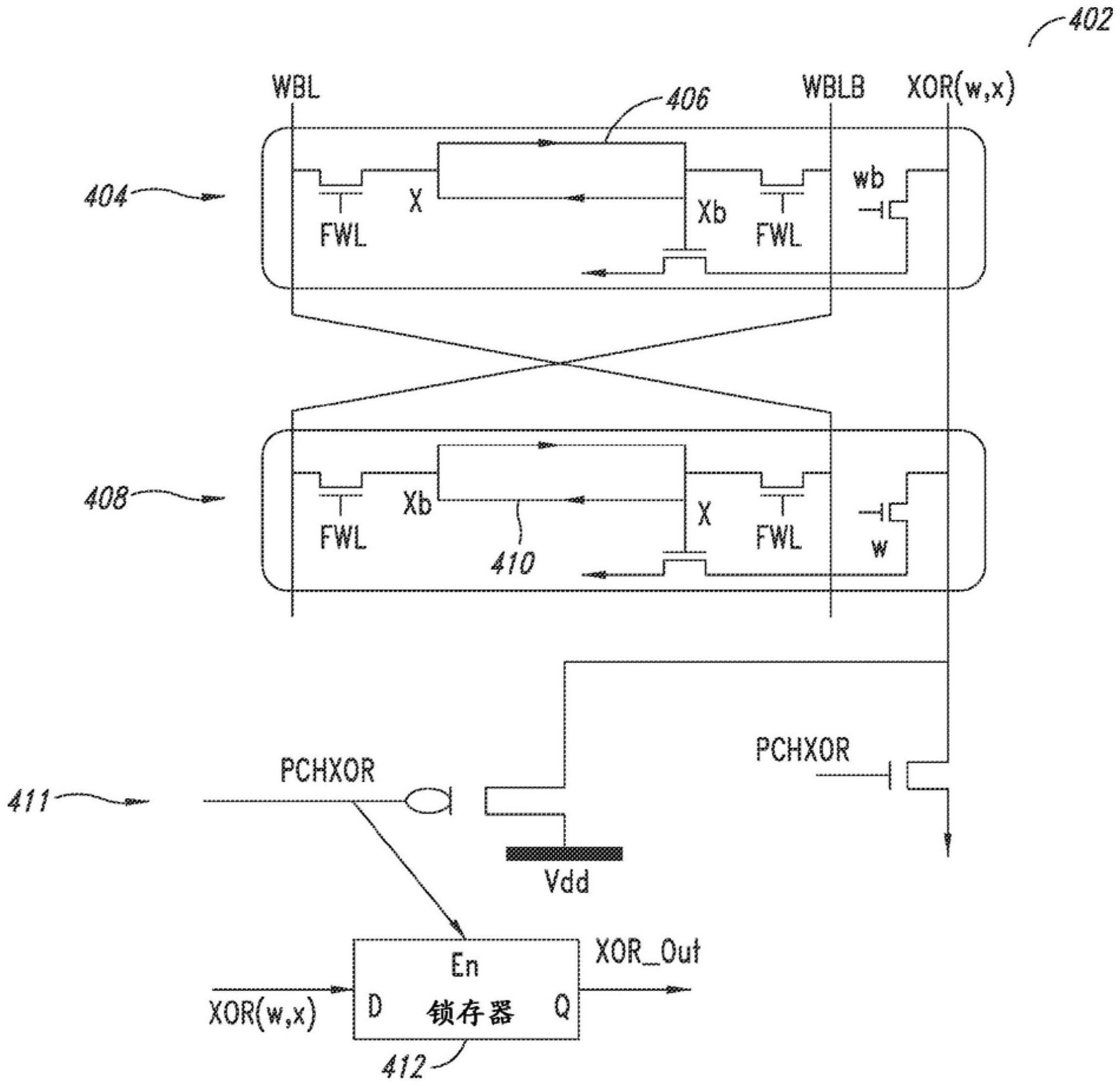

1、在一个实施例中,存内计算存储器单元包括具有锁存器、写位线和互补写位线的第一位单元,以及具有锁存器、写位线和互补写位线的第二位单元。第一位单元的写位线被耦合到第二位单元的互补写位线,并且第一位单元的互补写位线被耦合到第二位单元的写位线。在一个实施例中,第一位单元和第二位单元是代工(foundry)位单元。

2、在一个实施例中,存储器阵列包括多个位单元,多个位单元被布置为与存储器阵列的多个列相交的位单元行的集合。存储器阵列还具有多个存内计算(imc)单元,该多个imc单元被布置为与存储器阵列的多个列相交的存储器阵列的imc单元行的集合。存储器阵列的imc单元中的每个imc单元包括具有锁存器、写位线和互补写位线的第一位单元,以及具有锁存器、写位线和互补写位线的第二位单元。在每个imc单元中,第一位单元的写位线被耦合到第二位单元的互补写位线,并且第一位单元的互补写位线被耦合到第二位单元的写位线。

3、在一个实施例中,系统包括多个存内计算(imc)存储器阵列。每个imc存储器阵列包括:多个位单元,其被布置为与imc存储器阵列的多个列相交的位单元行的集合;以及imc存储器阵列的多个存内计算(imc)单元,其被布置为与imc存储器阵列的多个列相交的imc单元行的集合。imc单元具有:第一位单元,其具有锁存器、写位线和互补写位线;以及第二位单元,其具有锁存器、写位线和互补写位线。在imc单元中,第一位单元的写位线被耦合到第二位单元的互补写位线,并且第一位单元的互补写位线被耦合到第二位单元的写位线。系统具有与多个imc存储器阵列的列耦合的累加电路系统。

4、在一个实施例中,方法包括:在存内计算(imc)存储器阵列的多个行中存储权重数据,存内计算(imc)存储器阵列被布置为与多个单元列相交的多个单元行,imc存储器阵列包括位单元行的集合和imc单元行的集合。imc存储器阵列的imc单元中的每个imc单元包括具有锁存器、写位线和互补写位线的第一位单元;以及具有锁存器、写位线和互补写位线的第二位单元,其中第一位单元的写位线被耦合到第二位单元的互补写位线,并且第一位单元的互补写位线被耦合到第二位单元的写位线。特征数据被存储在imc单元行集合中的一个或多个行中。imc存储器阵列的列中的imc单元将存储在imc单元中的特征数据与存储在imc单元的列中的权重数据相乘。在一个实施例中,非暂时性计算机可读介质具有在运算中、将计算系统配置为执行方法的内容。

技术特征:

1.一种存内计算存储器单元,包括:

2.根据权利要求1所述的存内计算单元,其中所述第一位单元和所述第二位单元是代工位单元。

3.根据权利要求2所述的存内计算单元,其中所述第一位单元和所述第二位单元是八个晶体管位单元。

4.根据权利要求1所述的存内计算单元,其中所述第一位单元包括读字线和读位线,并且所述第二位单元包括读字线和读位线,并且在存内计算运算模式中,所述存内计算单元对存储在所述锁存器中的特征数据与所述读字线上提供的权重数据进行异或运算(xor)。

5.一种存储器阵列,包括:

6.根据权利要求5所述的存储器阵列,其中所述多个位单元、所述imc单元的所述第一位单元和所述imc单元的所述第二位单元是代工位单元。

7.根据权利要求6所述的存储器阵列,其中,

8.根据权利要求5所述的存储器阵列,其中所述imc单元的所述第一位单元包括读字线和读位线,并且所述imc单元的所述第二位单元包括读字线和读位线,并且在所述阵列的存内计算运算模式中,所述imc单元选择性地对存储在所述锁存器中的特征数据与所述读字线上提供的权重数据进行异或运算(xor)。

9.根据权利要求5所述的存储器阵列,其中所述阵列包括耦合到所述多个imc单元的预充电电路系统。

10.根据权利要求9所述的存储器阵列,其中所述预充电电路系统包括屏蔽电路系统,所述屏蔽电路系统在运算中选择性地屏蔽所述阵列的列的输出。

11.根据权利要求5所述的存储器阵列,其中所述位单元行的集合包括多个位单元行,并且所述imc单元行的集合包括多个imc单元行。

12.根据权利要求11所述的存储器阵列,包括耦合到所述imc单元行的集合的选择电路系统,其中所述选择电路系统在运算中选择所述多个imc单元行中的行。

13.根据权利要求11所述的存储器阵列,其中所述imc单元行的集合包括四个imc单元行。

14.根据权利要求12所述的存储器阵列,其中在运算中,所述imc单元行的集合中的单个行被配置为以imc运算模式或以位单元运算模式来运算。

15.一种系统,包括:

16.根据权利要求15所述的系统,其中所述多个imc存储器阵列的所述多个位单元、所述imc单元的所述第一位单元和所述imc单元的所述第二位单元是代工位单元。

17.根据权利要求15所述的系统,其中所述imc单元的所述第一位单元包括读字线和读位线,并且所述imc单元的所述第二位单元包括读字线和读位线,并且在所述系统的存内计算运算模式中,所述imc单元选择性地对存储在所述锁存器中的特征数据与所述读字线上提供的权重数据进行异或运算(xor)。

18.根据权利要求15所述的系统,其中所述多个imc存储器阵列包括耦合到所述多个imc单元的预充电电路系统。

19.根据权利要求18所述的系统,其中所述预充电电路系统包括屏蔽电路系统,所述屏蔽电路系统在运算中选择性地屏蔽所述阵列的列的输出。

20.根据权利要求15所述的系统,其中所述累加电路系统包括多个加法器。

21.根据权利要求15所述的系统,其中所述累加电路系统包括一个或多个电容器。

22.根据权利要求21所述的系统,包括能够选择性地耦合到所述累加电路系统的一个或多个偏置电容器。

23.根据权利要求21所述的系统,包括耦合到所述一个或多个电容器的读出电路系统。

24.根据权利要求23所述的系统,其中所述读出电路系统包括模数转换器。

25.根据权利要求23所述的系统,其中所述读出电路系统包括逐次逼近电路。

26.一种方法,包括:

27.根据权利要求26所述的方法,包括控制所述imc单元行的集合中的单个行的运算模式。

28.根据权利要求26所述的方法,其中所述相乘针对所述多个列的集合而被执行,并且所述方法包括累加所述列的集合的相乘运算结果。

29.根据权利要求28所述的方法,包括累加多个imc存储器阵列的相乘运算结果。

30.根据权利要求29所述的方法,包括对所累加的所述相乘运算结果施加偏置。

31.根据权利要求29所述的方法,包括基于所述多个imc存储器阵列的所累加的所述相乘运算结果,生成神经网络的分类信号。

32.一种具有内容的非暂时性计算机可读介质,所述内容在运算中,将计算系统配置为执行方法,所述方法包括:

33.根据权利要求32所述的非暂时性计算机可读介质,其中所述内容包括由所述计算系统执行的指令。

技术总结

本公开的实施例涉及基于位单元的架构的存内计算。存储器阵列包括多个位单元,多个位单元被布置为与多个列相交的位单元行的集合。存储器阵列还包括多个存内计算(IMC)单元,多个存内计算(IMC)单元被布置为与存储器阵列的多个列相交的IMC单元行的集合。存储器阵列的IMC单元中的每个IMC单元包括具有锁存器、写位线和互补写位线的第一位单元,和具有锁存器、写位线和互补写位线的第二位单元,其中第一位单元的写位线被耦合到第二位单元的互补写位线,并且第一位单元的互补写位线被耦合到第二位单元的写位线。

技术研发人员:H·拉瓦特,D·K·加纳丹,P·库玛,N·乔拉,M·阿尤蒂亚瓦斯

受保护的技术使用者:意法半导体国际有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!