具有每扇区高速缓存驻留控件的高速缓存存储器的制作方法

各种实施例总体上涉及计算存储器架构,并且更具体地,涉及具有每扇区高速缓存驻留控件的高速缓存存储器。

背景技术:

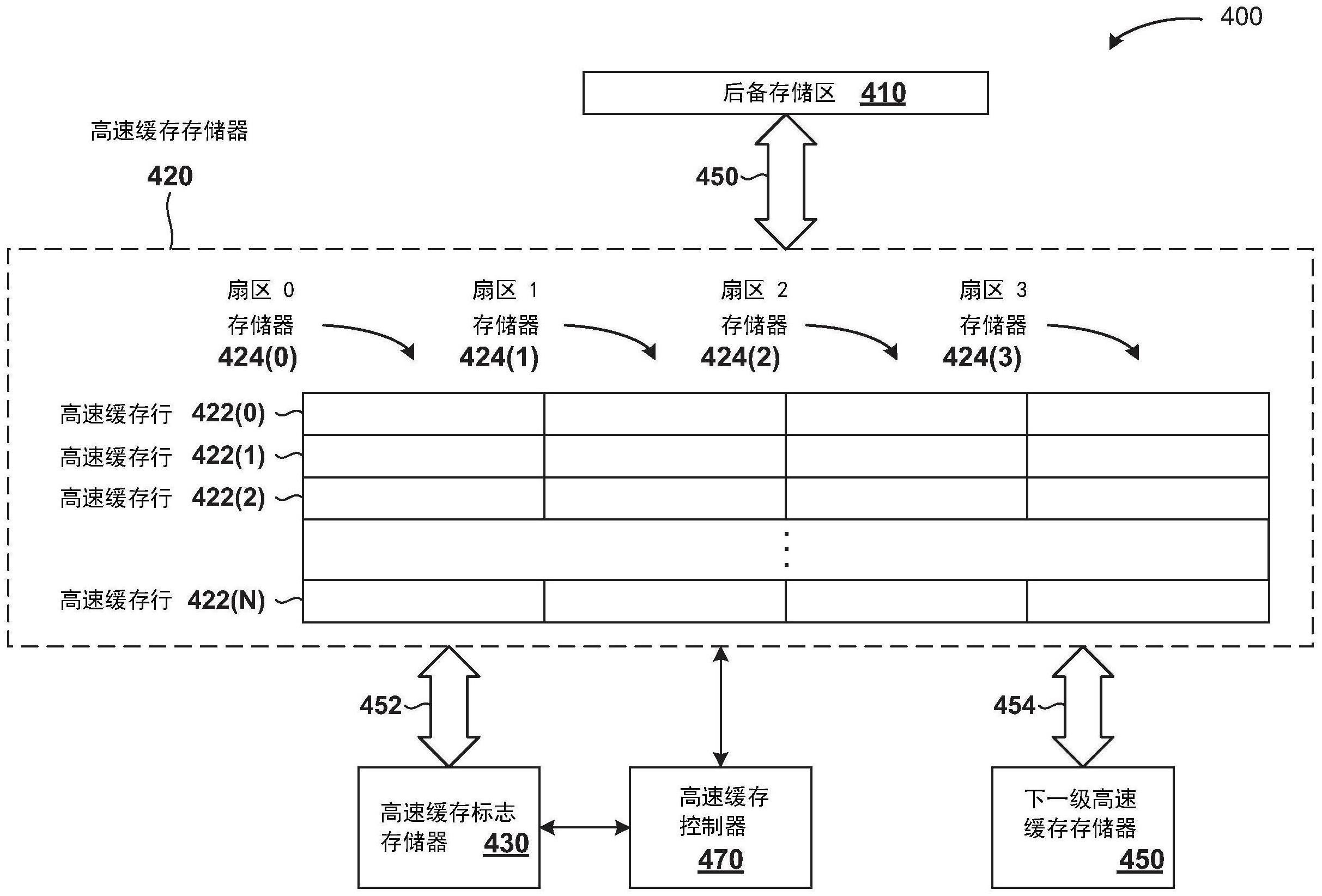

1、除其他外,计算系统通常包括一个或更多个处理单元,例如中央处理单元(cpu)和/或图形处理单元(gpu),以及一个或更多个存储器系统。处理单元执行用户模式软件应用程序,该应用程序提交和启动计算任务,执行包括在处理单元中的一个或更多个计算引擎。处理单元包括一个多层存储器系统,以在从存储器加载数据和将数据存储到存储器时提高性能。

2、多层存储器系统包括相对较大且性能相对较低的系统存储器,用于存储用户模式软件应用程序中包括的大量程序指令以及用户模式软件应用程序在执行期间随时间访问的数据。此外,多层存储器系统包括相对较小且性能相对较高的高速缓存存储器,用于存储用户模式软件应用当前或即将可访问的那些程序指令和数据。高速缓存控制器在使用时或就在使用之前将来自系统存储器的指令和数据加载到高速缓存存储器中。结果,处理单元能够比从较低性能的系统存储器更频繁地从用于指令和数据的高性能高速缓存存储器加载指令和数据。处理单元由此相对于仅具有系统存储器的非分层存储器系统实现了改进的存储器性能。

3、处理单元还可以将数据存储到高速缓存存储器。例如,可以将高速缓存存储器组织为一组高速缓存行,其中每个高速缓存行包括数十或数百字节的数据。当高速缓存控制器最初用系统存储器中的数据加载高速缓存行时,该高速缓存行被认为是干净的,因为高速缓存行中的数据与系统存储器的相应部分中的数据相同。如果处理单元将一个或更多个新的或更新的数据字节存储到高速缓存行中,则高速缓存行中的数据不再与系统存储器的相应部分中的数据相同。这样的高速缓存行被标记为脏。高速缓存控制器最终将脏高速缓存行写入系统存储器并将高速缓存行标记为干净。

4、通常,系统存储器和高速缓存存储器之间的可用存储器传输带宽是有限的。因此,可以通过减少系统存储器和高速缓存存储器之间的数据传输流量来提高高速缓存存储器性能。减少这种数据传输流量的一种技术是防止某些脏高速缓存行从高速缓存存储器回写到系统存储器。如果软件应用程序知道该软件应用程序不再需要某个范围的存储器地址,则该软件应用程序可以使包含该存储器地址范围内的数据的任何高速缓存行无效。高速缓存控制器被禁止将无效的高速缓存行写回存储器,即使对于包括脏数据的无效高速缓存行也是如此,这会导致系统存储器和高速缓存存储器之间的传输流量减少。此外,这种使高速缓存行无效的方法可能导致语义不连贯(例如可能永久丢失的脏数据)。即便如此,不再需要有效高速缓存行中的数据的软件应用程序可以明确地允许高速缓存行无效的这种方法。

5、这种用于减少传输流量的技术的一个问题是,被软件应用程序无效的存储器地址的范围可能与对应的高速缓存行的地址不对齐。例如,高速缓存行可以具有落入被无效的存储器地址范围内的第一部分和落入该范围之外的第二部分。如果高速缓存行的第二部分包含任何脏数据,则高速缓存行需要在失效之前写回存储器。在扇区高速缓存中,每个高速缓存行被划分为一组扇区,只有脏扇区需要在失效之前写回存储器。在任何一种情况下,在失效之前要求回写都可能首先破坏失效的目的。或者,软件应用程序可以生成跟踪每个高速缓存行的跟踪数据结构,识别每个高速缓存行的哪些部分是有效的以及哪些部分是无效的。然而,这种跟踪数据结构本身存储在高速缓存存储器中,从而消耗了系统存储器和高速缓存存储器之间的存储器传输带宽,这与降低存储器传输带宽的目标相悖。

6、如前所述,本领域需要用于管理计算系统中的高速缓存存储器的更有效的技术。

技术实现思路

1、本公开的各种实施例阐述了一种用于管理计算系统中的高速缓存存储器的计算机实现的方法。该方法包括检测使高速缓存存储器的第一高速缓存行中的第一扇区无效的指令。该方法还包括确定第一扇区在高速缓存存储器中的位置。该方法还包括基于位置识别与第一扇区相关联的第一状态指示符。该方法进一步包括修改第一状态指示符同时维持第一高速缓存行中的第二扇区的状态指示符,其中修改后的第一状态指示符使第一扇区无效。

2、其他实施例包括但不限于实现所公开技术的一个或更多个方面的系统,以及包括用于执行所公开技术的一个或更多个方面的指令的一个或更多个计算机可读介质,以及用于执行所公开技术的一个或更多个方面的方法。

3、所公开的技术相对于现有技术的至少一个技术优势在于,利用所公开的技术,高速缓存存储器可以在比整个高速缓存行更精细的分辨率下使高速缓存存储器无效。结果,相对于只能使整个高速缓存行无效的先前方法,脏高速缓存行的回写减少了,从而提高了高速缓存存储器性能以及更快地执行软件应用程序。这些优点代表了对现有技术方法的一项或更多项技术改进。

技术特征:

1.一种用于管理计算系统中的高速缓存存储器的计算机实现的方法,所述方法包括:

2.根据权利要求1所述的计算机实现的方法,其中所述指令包括要被无效的存储器地址范围,并且所述方法还包括:

3.根据权利要求1所述的计算机实现的方法,其中所述指令包括第一存储器地址和要被无效的若干扇区,并且所述方法还包括:

4.根据权利要求1所述的计算机实现的方法,其中所述指令包括要被无效的存储器地址范围,并且所述方法还包括:

5.根据权利要求1所述的计算机实现的方法,其中所述指令包括第一存储器地址和要被无效的若干扇区,并且所述方法还包括:

6.根据权利要求1所述的计算机实现的方法,其中修改所述第一状态指示符包括修改与所述第一扇区相关联的指示符以指示所述第一扇区包含无效数据。

7.根据权利要求1所述的计算机实现的方法,其中修改所述第一状态指示符包括修改与所述第一扇区相关联的指示符以指示所述第一扇区不包含要存储在后备存储区中的数据。

8.根据权利要求1所述的计算机实现的方法,其中所述第一高速缓存行包括128字节,并且包括在所述第一高速缓存行中的每个扇区包括32字节。

9.根据权利要求1所述的计算机实现的方法,其中所述高速缓存存储器包括一级l1高速缓存、1.5级l1.5高速缓存或二级l2高速缓存。

10.根据权利要求1所述的计算机实现的方法,其中所述指令包括原子操作,所述原子操作将数据从所述第一扇区原子地加载到一个或更多个寄存器,同时修改与所述第一扇区相关联的所述第一状态指示符。

11.根据权利要求1所述的计算机实现的方法,其中所述指令由软件应用程序发出。

12.一种系统,包括:

13.根据权利要求12所述的系统,其中所述指令包括要被无效的存储器地址范围,并且其中所述高速缓存控制器还被配置为:

14.根据权利要求12所述的系统,其中所述指令包括第一存储器地址和要被无效的若干扇区,并且其中所述高速缓存控制器还被配置为:

15.根据权利要求12所述的系统,其中所述指令包括要被无效的存储器地址范围,并且其中所述高速缓存控制器还被配置为:

16.根据权利要求12所述的系统,其中所述指令包括第一存储器地址和要被无效的若干扇区,并且其中所述高速缓存控制器还被配置为:

17.根据权利要求12所述的系统,其中为了修改所述第一状态指示符,所述高速缓存控制器被配置为修改与所述第一扇区相关联的指示符以指示所述第一扇区包含无效数据。

18.根据权利要求12所述的系统,其中为了修改所述第一状态指示符,所述高速缓存控制器被配置为修改与所述第一扇区相关联的指示符以指示所述第一扇区不包含要存储在后备存储区中的数据。

19.根据权利要求12所述的系统,其中所述第一高速缓存行包括128字节,并且包括在所述第一高速缓存行中的每个扇区包括32字节。

20.根据权利要求12所述的系统,其中所述指令包括原子操作,所述原子操作将数据从所述第一扇区原子地加载到一个或更多个寄存器,同时修改与所述第一扇区相关联的所述第一状态指示符。

技术总结

本公开涉及具有每扇区高速缓存驻留控件的高速缓存存储器。各种实施例包括用于管理计算系统中的高速缓存存储器的技术。计算系统包括扇区化的高速缓存存储器,为软件应用程序提供逐扇区地直接使存储在高速缓存存储器中的数据项无效的机制,其中扇区小于高速缓存行。当高速缓存行中的所有扇区都已被无效时,高速缓存行隐式无效,释放高速缓存行以重分配用于其他目的。在待无效数据项可与扇区边界对齐的情况下,公开的技术有效使用高速缓存标志存储器中的状态指示符跟踪哪些扇区和相应数据项已被软件应用程序无效。因此,公开的技术由此实现用于使小于高速缓存行的各个数据项无效的低开销解决方案,无需额外跟踪数据结构或消耗额外存储器传输带宽。

技术研发人员:M·费特曼,S·加德雷,S·J·海因里希,M·斯蒂克,尹亮

受保护的技术使用者:辉达公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!