芯片设计的布局规划方法及相关设备与流程

本申请涉及芯片,尤其涉及一种芯片设计的布局规划方法及相关设备。

背景技术:

1、电子设计自动化(electronic design automation,简称eda),是指利用计算机辅助设计(cad)软件,来完成超大规模集成电路(vlsi)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

2、在数字芯片物理设计布局规划(floorplan)阶段,可以使用混合摆放(mixed-place)的方法来解决布局规划问题。该方法将硬核(hard macros)和标准单元(standardcells)同时摆放,减少了工程师的工作量和布局规划设计时间。

3、但是,本申请的发明人发现,相关技术中,在混合摆放后的硬核排列不整齐,这会导致多种问题。

技术实现思路

1、鉴于此,本申请提出一种芯片设计的布局规划方法及相关设备,以解决或部分解决上述问题。

2、本申请第一方面,提供了一种芯片设计的布局规划方法,包括:

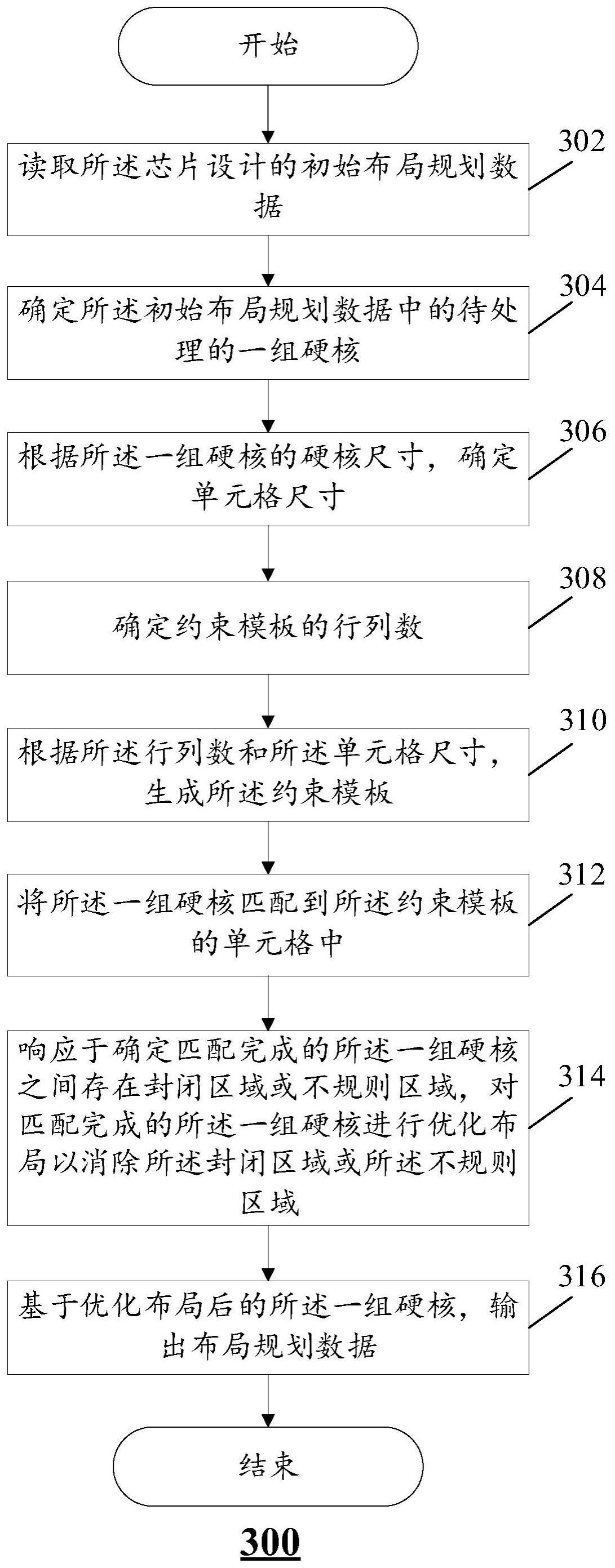

3、读取所述芯片设计的初始布局规划数据;

4、确定所述初始布局规划数据中的待处理的一组硬核;

5、根据所述一组硬核的硬核尺寸,确定单元格尺寸;

6、确定约束模板的行列数;

7、根据所述行列数和所述单元格尺寸,生成所述约束模板;

8、基于线性规划算法或者混合整数线性规划方法,将所述一组硬核匹配到所述约束模板的单元格中;

9、响应于确定匹配完成的所述一组硬核之间存在封闭区域或不规则区域,对匹配完成的所述一组硬核进行优化布局以消除所述封闭区域或所述不规则区域;

10、基于优化布局后的所述一组硬核,输出布局规划数据。

11、本申请第二方面,提供了一种计算机设备,包括一个或者多个处理器、存储器;和一个或多个程序,其中所述一个或多个程序被存储在所述存储器中,并且被所述一个或多个处理器执行,所述程序包括用于执行根据第一方面所述的方法的指令。

12、本申请第三方面,提供了一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行第一方面所述的方法。

13、本申请第四方面,提供了一种计算机程序产品,包括计算机程序指令,当所述计算机程序指令在计算机上运行时,使得计算机执行第一方面所述的方法。

14、本申请提供的芯片设计的布局规划方法及相关设备,通过划分单元格的方式来创建约束模板,然后将需要规整对齐的一组硬核匹配到约束模板中,再对封闭区域或不规则区域进行消除,得到规整对齐的一组硬核,从而可以自动规整对齐具有混合高度的一组硬核。

技术特征:

1.一种芯片设计的布局规划方法,包括:

2.如权利要求1所述的方法,其中,根据所述一组硬核的硬核尺寸,确定单元格尺寸,包括:

3.如权利要求1所述的方法,其中,根据所述一组硬核的硬核尺寸,确定单元格尺寸,包括:

4.如权利要求1所述的方法,其中,确定约束模板的行列数,包括:

5.如权利要求1所述的方法,其中,将所述一组硬核匹配到所述约束模板的单元格中,包括:

6.如权利要求1所述的方法,其中,将所述一组硬核匹配到所述约束模板的单元格中,包括:

7.如权利要求1所述的方法,其中,对匹配完成的所述一组硬核进行优化布局以消除所述封闭区域或所述不规则区域,包括:

8.如权利要求1所述的方法,其中,将所述一组硬核匹配到所述约束模板的单元格中,包括:

9.如权利要求1所述的方法,其中,基于优化布局后的所述一组硬核,输出布局规划数据,进一步包括:

10.如权利要求9所述的方法,其中,对优化布局后的所述一组硬核的间距进行调整以压缩在所述一组硬核的总面积,包括:

11.一种计算机设备,包括一个或者多个处理器、存储器;和一个或多个程序,其中所述一个或多个程序被存储在所述存储器中,并且被所述一个或多个处理器执行,所述程序包括用于执行根据权利要求1-10任意一项所述的方法的指令。

12.一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行权利要求1-10中任一项所述的方法。

13.一种计算机程序产品,包括计算机程序指令,当所述计算机程序指令在计算机上运行时,使得计算机执行如权利要求1-10中任一项所述的方法。

技术总结

本申请提供一种芯片设计的布局规划方法及相关设备。该方法,包括:读取所述芯片设计的初始布局规划数据;确定所述初始布局规划数据中的待处理的一组硬核;根据所述一组硬核的硬核尺寸,确定单元格尺寸;确定约束模板的行列数;根据所述行列数和所述单元格尺寸,生成所述约束模板;将所述一组硬核匹配到所述约束模板的单元格中;响应于确定匹配完成的所述一组硬核之间存在封闭区域或不规则区域,对匹配完成的所述一组硬核进行优化布局以消除所述封闭区域或所述不规则区域;基于优化布局后的所述一组硬核,输出布局规划数据。

技术研发人员:张新城,沈波

受保护的技术使用者:芯行纪科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!