算术编码数据处理电路、设备及方法与流程

本公开涉及数据处理,尤其涉及算术编码数据处理电路、设备及方法。

背景技术:

1、算术编码是一种无损数据压缩方法,是一种熵编码。下面以一种常见的设计过程中的场景进行说明,算术编码模块的输出是8bit的随机长度数据,而最终以128bit的固定长度存储至内存中,例如,内存可以是双倍速率同步动态随机存储器(ddr)。

2、这种场景下,需要进行数据的处理,按照常规的移位寄存器进行处理,数据是非流水的,模块的处理效率不高。

技术实现思路

1、本公开实施例提供一种算术编码数据处理电路、设备及方法,能够解决数据处理是非流水的,模块处理效率不高的问题。所述技术方案如下:

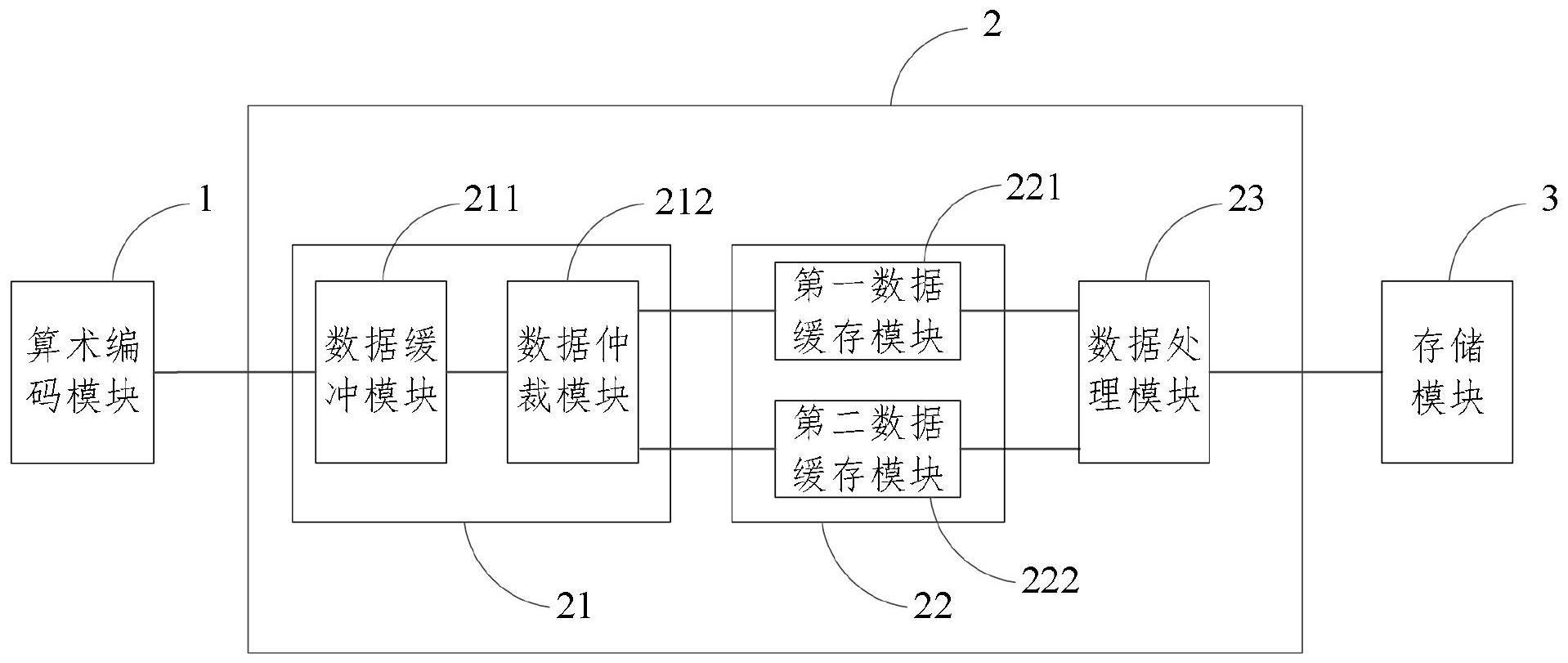

2、根据本公开实施例的第一方面,提供一种算术编码数据处理电路,包括:依次连接的数据分流模块、总数据缓存模块和数据处理模块;所述总数据缓存模块包括:并联的第一数据缓存模块和第二数据缓存模块;

3、所述数据分流模块用于接收当前数据,并将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据;

4、所述第一数据缓存模块和所述第二数据缓存模块用于分别交替输出所述两路数据至所述数据处理模块;

5、所述数据处理模块用于根据所述两路数据,得到目标数据。

6、可选的,所述数据分流模块包括:数据仲裁模块;所述数据仲裁模块用于将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据。

7、可选的,所述数据仲裁模块具体用于:

8、将所述当前数据分成第一路数据、第二路数据、第三路数据和第四路数据;

9、所述第一路数据和所述第二路数据通过第一数据选择器,得到第一缓存数据;所述第一数据选择器的输出端与所述第一数据缓存模块的输入端连接;

10、所述第三路数据和所述第四路数据通过第二数据选择器,得到第二缓存数据;所述第二数据选择器的输出端与所述第二数据缓存模块的输入端连接。

11、可选的,所述数据仲裁模块还包括仲裁器;所述仲裁器用于确定所述当前数据长度,以及确定向所述第一数据缓存模块和所述第二数据缓存模块发送数据的情况。

12、可选的,所述数据分流模块还包括:数据缓冲模块;所述数据缓冲模块的输出端与所述数据仲裁模块的输入端连接;所述数据缓冲模块用于接收并缓存所述当前数据,并向所述数据仲裁模块发送缓存的所述当前数据。

13、可选的,所述数据处理模块具体用于:

14、拼接所述第一数据缓存模块和所述第二数据缓存模块发送的当前数据,得到拼接数据;

15、将所述拼接数据扩大到预设长度,得到目标数据。

16、根据本公开实施例的第二方面,提供一种算术编码数据处理设备,包括如上述第一方面所述的算术编码数据处理电路。

17、根据本公开实施例的第三方面,提供一种算术编码数据处理方法,所述方法应用于算术编码数据处理电路,所述算术编码数据处理电路包括:依次连接的数据分流模块、总数据缓存模块和数据处理模块;所述总数据缓存模块包括:并联的第一数据缓存模块和第二数据缓存模块;所述方法包括:

18、所述数据分流模块接收当前数据,并将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据;

19、所述第一数据缓存模块和所述第二数据缓存模块分别交替输出所述两路数据至所述数据处理模块;

20、所述数据处理模块根据所述两路数据,得到目标数据。

21、可选的,所述数据分流模块包括:数据仲裁模块和数据缓冲模块,所述数据缓冲模块的输出端与所述数据仲裁模块的输入端连接;所述数据分流模块接收当前数据,并将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据,包括:

22、所述数据缓冲模块接收并缓存当前数据,并向所述数据仲裁模块发送缓存的所述当前数据;

23、所述数据仲裁模块将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据。

24、可选的,所述数据仲裁模块将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据,包括:

25、将所述当前数据分成第一路数据、第二路数据、第三路数据和第四路数据;

26、所述第一路数据和所述第二路数据通过第一数据选择器,得到第一缓存数据,并向所述第一数据缓存模块发送所述第一缓存数据;

27、所述第三路数据和所述第四路数据通过第二数据选择器,得到第二缓存数据,并向所述第二数据缓存模块发送所述第二缓存数据。

28、本实施例提供的算术编码数据处理电路、设备及方法,通过数据分流模块接收当前数据,并将当前数据分成两路数据,分别交替向第一数据缓存模块和第二数据缓存模块发送该两路数据,以使第一数据缓存模块和第二数据缓存模块能够交替将数据发送给数据处理模块,实现了数据的乒乓管线传输,从而完成从算术编码模块输出到存储模块的数据调度和处理,数据传输不间断,时序较好,处理效率较高。

29、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种算术编码数据处理电路,其特征在于,包括:依次连接的数据分流模块、总数据缓存模块和数据处理模块;所述总数据缓存模块包括:并联的第一数据缓存模块和第二数据缓存模块;

2.根据权利要求1所述的算术编码数据处理电路,其特征在于,所述数据分流模块包括:数据仲裁模块;所述数据仲裁模块用于将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据。

3.根据权利要求2所述的算术编码数据处理电路,其特征在于,所述数据仲裁模块具体用于:

4.根据权利要求2所述的算术编码数据处理电路,其特征在于,所述数据仲裁模块还包括仲裁器;所述仲裁器用于确定所述当前数据长度,以及确定向所述第一数据缓存模块和所述第二数据缓存模块发送数据的情况。

5.根据权利要求2所述的算术编码数据处理电路,其特征在于,所述数据分流模块还包括:数据缓冲模块;所述数据缓冲模块的输出端与所述数据仲裁模块的输入端连接;所述数据缓冲模块用于接收并缓存所述当前数据,并向所述数据仲裁模块发送缓存的所述当前数据。

6.根据权利要求2所述的算术编码数据处理电路,其特征在于,所述数据处理模块具体用于:

7.一种算术编码数据处理设备,其特征在于,包括如权利要求1至6任一项所述的算术编码数据处理电路。

8.一种算术编码数据处理方法,其特征在于,所述方法应用于算术编码数据处理电路,所述算术编码数据处理电路包括:依次连接的数据分流模块、总数据缓存模块和数据处理模块;所述总数据缓存模块包括:并联的第一数据缓存模块和第二数据缓存模块;所述方法包括:

9.根据权利要求8所述的方法,其特征在于,所述数据分流模块包括:数据仲裁模块和数据缓冲模块,所述数据缓冲模块的输出端与所述数据仲裁模块的输入端连接;所述数据分流模块接收当前数据,并将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据,包括:

10.根据权利要求9所述的方法,其特征在于,所述数据仲裁模块将所述当前数据分成两路数据,分别交替向所述第一数据缓存模块和所述第二数据缓存模块发送所述两路数据,包括:

技术总结

本公开提供一种算术编码数据处理电路、设备及方法,通过数据分流模块接收当前数据,并将当前数据分成两路数据,分别交替向第一数据缓存模块和第二数据缓存模块发送该两路数据,以使第一数据缓存模块和第二数据缓存模块能够交替将数据发送给数据处理模块,实现了数据的乒乓管线传输,从而完成从算术编码模块输出到存储模块的数据调度和处理,数据传输不间断,时序较好,处理效率较高。

技术研发人员:吴鹏远

受保护的技术使用者:重庆京像微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!