使用可编程逻辑器件的多个电压域的功率分配的制作方法

本公开总体上涉及具有可编程逻辑的集成电路器件,例如可编程逻辑器件。更具体地,本公开涉及可编程逻辑器件的电功率消耗管理。

背景技术:

1、该部分旨在向读者介绍可能与在下面描述和/或要求保护的本公开的各个方面有关的领域中的各个方面。该论述被认为有助于为读者提供背景技术信息,以促进对本公开的各个方面的更好理解。因此,可以理解,这些陈述应鉴于此进行解读,而不应被认为是现有技术。

2、集成电路器件存在于许多电子器件中。一种类型的集成电路器件是可编程逻辑器件(pld),其可以使用可编程逻辑电路来实现多种可能的系统逻辑设计。可编程逻辑器件可以使用各种实现的逻辑设计来执行各种可能的操作。操作可编程逻辑器件消耗功率。可能希望减少由整个可编程逻辑器件所消耗的功率量。然而,即使降低可编程逻辑器件的电压可能允许逻辑设计的一部分在较低的功率下有效地操作,这样做可能使逻辑设计的另一部分不可操作或不合适。

技术实现思路

1、根据本公开的一个实施例,提供了一种用于在不同电压电平下操作可编程逻辑电路的多个区域的集成电路系统,所述集成电路系统包括:可编程逻辑电路,所述可编程逻辑电路包括能够被配置为在不同电压电平下操作的多个区域;以及多个电平移位器,所述多个电平移位器能够被配置为促进在第一电压下操作的一个区域与在第二电压下操作的第二区域之间的通信。

2、根据本公开的一个实施例,提供了一种用于在不同电压下操作可编程逻辑器件的系统,所述系统包括:可编程逻辑器件,所述可编程逻辑电路能够被配置为在第一电压下操作第一区域并且在第二电压下操作第二区域;存储指令的存储器和实施所述指令的处理器,其中,所述指令使得所述处理器执行以下操作:接收所述可编程逻辑器件的系统设计;使用电压感知布局和布线(voltage-aware placement and routing)来生成比特流以用于对所述可编程逻辑器件进行编程;以及向所述可编程逻辑器件提供所述比特流以对所述第一区域和所述第二区域进行编程。

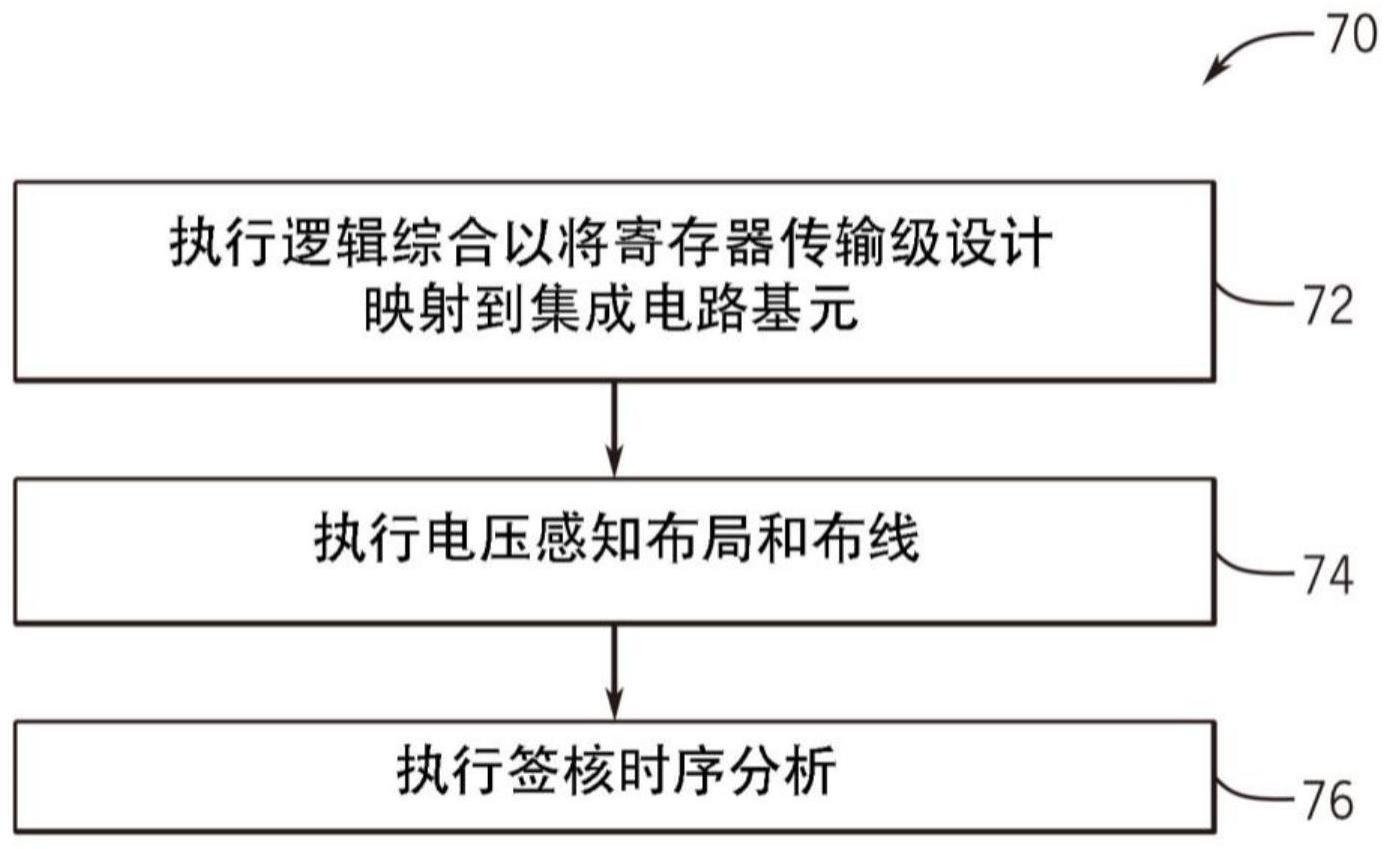

3、根据本公开的一个实施例,提供了一种用于生成具有能够在不同电压电平下操作的可编程逻辑区域的集成电路系统设计的方法,所述方法包括:经由处理器来接收包括用户定义的时序约束的寄存器传输级设计;经由所述处理器基于所述时序约束来确定电压感知布局和布线;以及基于电压感知布局和布线的确定,向可编程逻辑电路的多个区域中的第一区域分配比第二区域低的电压。

技术特征:

1.一种用于在不同电压电平下操作可编程逻辑电路的多个区域的集成电路系统,所述集成电路系统包括:

2.根据权利要求1所述的集成电路系统,其中,所述多个区域中的每一个区域包括电压调节器,所述电压调节器用于控制所述多个区域中的每一个区域的电压量。

3.根据权利要求1所述的集成电路系统,其中,所述多个区域中的每一个区域接收来自独立电源的功率。

4.根据权利要求1所述的集成电路系统,其中,所述多个区域中的每一个区域包括局部区域控制器,所述局部区域控制器将配置数据编程到所述区域中。

5.根据权利要求1所述的集成电路系统,其中,所述多个区域中的多于一个区域被配置为接收控制信号以关闭所述多于一个区域的电压。

6.根据权利要求1至5中任一项所述的集成电路系统,其中,所述多个电平移位器位于跨所述多个区域延伸的结构线上。

7.根据权利要求1至5中任一项所述的集成电路系统,其中,所述多个区域中的每一个区域能够被配置为在所述可编程逻辑电路正在工作时动态地更新电压。

8.根据权利要求1至5中任一项所述的集成电路系统,其中,所述多个区域中的每一个区域具有相同尺寸。

9.一种用于在不同电压下操作可编程逻辑器件的系统,所述系统包括:

10.根据权利要求9所述的系统,其中,所述电压感知布局和布线包括:根据所述第一电压和所述第二电压来确定所述系统设计的时序约束。

11.根据权利要求10所述的系统,其中,所述比特流包括用于基于所述系统设计的时序约束将所述第一区域的电压分配为所述第一电压的指令。

12.根据权利要求9至11中任一项所述的系统,其中,所述系统设计包括用户定义的约束,所述用户定义的约束包括受电压影响的时序约束、受电压影响的功率约束、或上述两者。

13.根据权利要求9至11中任一项所述的系统,其中,所述比特流包括与所述可编程逻辑器件的多个区域中的一个或多个区域的电压值相对应的指令。

14.一种用于生成具有能够在不同电压电平下操作的可编程逻辑区域的集成电路系统设计的方法,所述方法包括:

15.根据权利要求14所述的方法,其中,确定所述电压感知布局和布线包括:基于根据向所述可编程逻辑电路的多个区域中的不同区域分配不同电压电平的优化标准,来演进所述寄存器传输级设计的关键路径。

16.根据权利要求15所述的方法,其中,所述优化标准包括根据所述不同电压电平的时序、拥塞、布线使用情况、以及利用率。

17.根据权利要求14至16中任一项所述的方法,其中,所述电压感知布局和布线包括:确定要分配给所述可编程逻辑电路的多个区域的电压电平。

18.根据权利要求14至16中任一项所述的方法,其中,所述第二区域包括所述寄存器传输级设计的至少一个关键路径,并且所述第一区域不包括所述寄存器传输级设计的一个关键路径。

19.根据权利要求14至16中任一项所述的方法,其中,所述方法包括:发送控制信号,所述控制信号在比特流中限定基于所述电压感知布局和布线的一个或多个配置比特。

20.根据权利要求19所述的方法,其中,发送所述控制信号包括:将包括所述一个或多个配置比特的所述比特流发送到所述可编程逻辑电路的多个区域中的配置随机存取存储器(cram),以基于所述电压感知布局和布线来限定所述可编程逻辑电路的多个区域中的一个或多个区域的电压电平。

技术总结

本公开涉及使用可编程逻辑器件的多个电压域的功率分配。一种集成电路器件,其包括可编程逻辑电路,所述可编程逻辑电路包括各自被配置为在不同电压电平下操作的多个区域。这些区域可以由电平移位器分隔开,电平移位器使得能够在不同电压电平区域之间进行通信。集成电路还可以包括为用户寄存器传输级设计执行电压感知布局和布线的软件,并且可以根据为区域限定的电压将逻辑引导到区域。

技术研发人员:马赫什·K·库马什卡尔,安克雷迪·纳拉马尔普,穆迪·阿尔塔夫·侯赛因,阿图尔·马赫什瓦里,李越,马赫什·A·艾耶

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!