一种基于FPGA的任意波形发生装置的制作方法

本发明涉及自动测试,具体涉及一种基于fpga的任意波形发生装置。

背景技术:

1、在嵌入式及自动测试领域,尤其是t/r组件测试系统,其测试项目指标要求高、涉及仪器仪表多、用于测试的t/r组件复杂波形、用于仪表切换的开关通道路数多。而传统的波形发生装置产生波形,会存在以下问题:

2、对于控制位数较多、控制信号较为复杂的t/r组件,所需要产生的波形波形控制板无法实时产生,往往需要二次开发,增加了不必要的开发成本,可移植性差。

3、对于所需要多脉冲触发的仪器仪表,传统波形发生装置只能在一定周期中固定地设置脉冲信号的数量和间隔,无法满足多种类接口、多脉宽、多周期的信号要求,可适用性差。

4、对于负责开关链路的开关矩阵,传统波形发生装置需要根据具体触发开关动作自行设计ttl控制信号,无法满足多项目,多矩阵的测试项目要求,可行性差。

技术实现思路

1、本发明的目的在于提供一种基于fpga的任意波形发生装置,以解决传统的波形发生装置在产生波形时的缺陷。

2、本发明的目的可以通过以下技术方案实现:

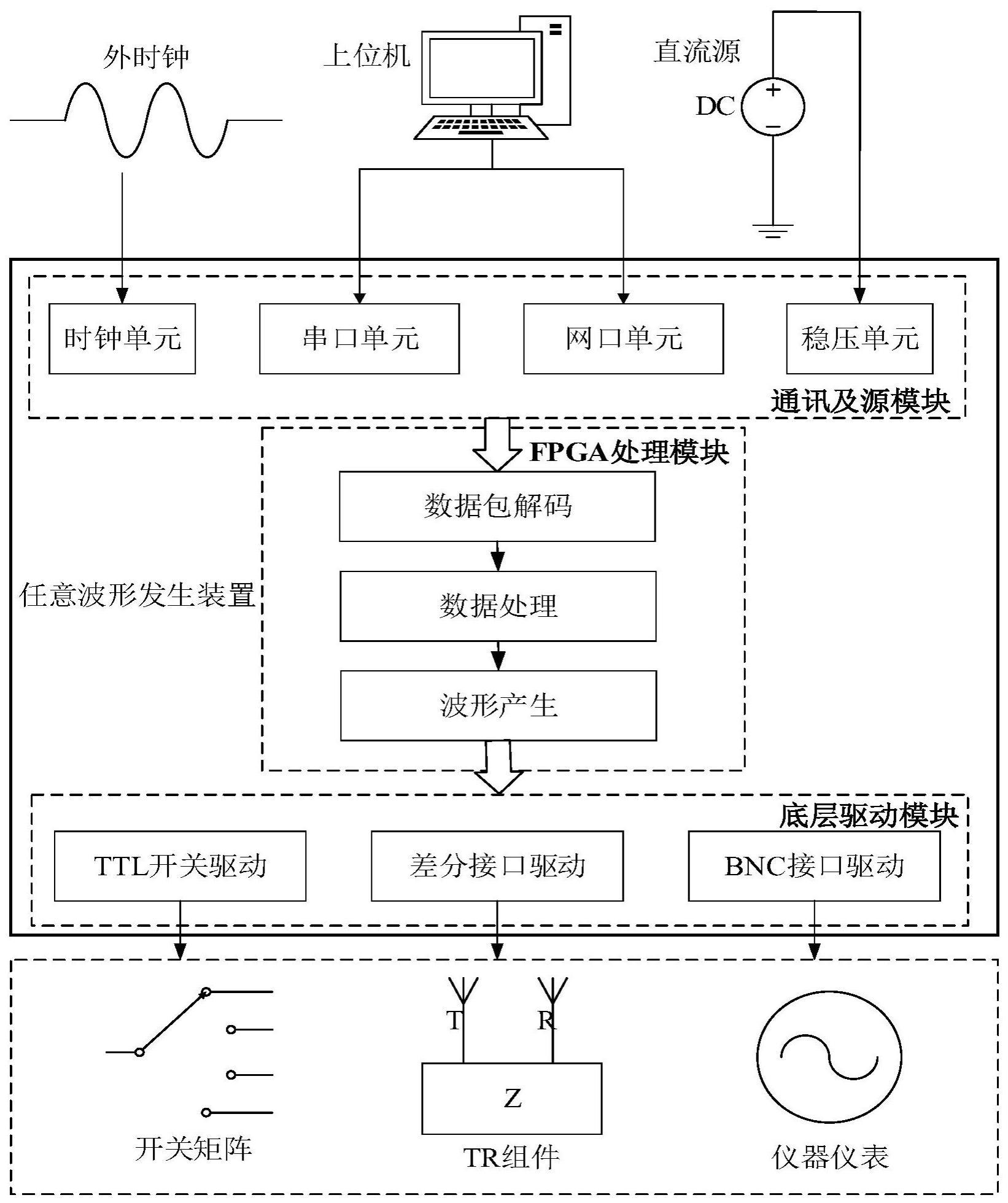

3、一种基于fpga的任意波形发生装置,包括通讯及源模块、fpga数据处理模块和底层驱动模块。

4、通讯及源模块用于接收上位机传输的数据及配置信息;

5、fpga数据处理模块用于对通讯及源模块接收的数据及配置信息进行数据包解码,解码后再进行数据处理,根据处理后的数据参数产生波形;

6、底层驱动模块用于接收数据参数以及产生的波形,并根据接收的数据参数和波形驱动相应接口输出。

7、作为本发明进一步的方案:所述通讯及源模块包括时钟单元、稳压单元、串口单元和网口单元。

8、时钟单元包括外时钟和内时钟;外时钟用于设备之间相位同步;内时钟用于产生主时钟;

9、稳压单元用于对提供的电压进行稳压;

10、串口单元用于接收波形配置信号,并以字节形式传输;

11、网口单元用于接收上位机传输的波形数据信号,并以字节形式传输。

12、作为本发明进一步的方案:所述fpga数据处理模块包括数据包解码单元、数据处理单元和波形产生单元。

13、数据包解码单元用于将网口单元发送的波形配置信号或串口单元发送的波形数据信号转为字节格式,以便后续波形产生;

14、数据处理单元用于按照指定有效字节个数进行数据处理,将有用信号筛选出来,并存储,提供给一个波形产生单元;

15、波形产生单元用于根据有效位数、相应时间分频、周期性和端口号的配置参数,输出所需要的波形。

16、作为本发明进一步的方案:所述数据包解码包括波形配置信息解码和数据参数信息解码;波形配置信息解码后的数据信息包括有效数据长度信息、周期分频信息和周期性使能信息;数据参数信息解码后的数据信息是在有效长度范围内,每一单位时钟内数字信息的具体参数值。

17、作为本发明进一步的方案:所述数据处理包括波形数据预处理、波形数据校验、波形数据生成。

18、作为本发明进一步的方案:所述底层驱动模块包括ttl开关驱动、差分接口驱动和bnc接口驱动。

19、ttl开关驱动用于控制相应开关矩阵,切换仪表的通道及相应的状态;

20、差分接口驱动用于向t/r组件提供sp i控制波形;

21、bnc接口驱动用于与测试仪表连接,确保测试的时钟同步。

22、本发明的有益效果:

23、本发明通过多模块逻辑组合,实时数据解析、多路并行数据处理、复杂波形产生等技术手段,实时产生各种多路可自定义的数字波形信号,可作为各种电子信息设备的通讯控制核心组成,解决了常规硬件编程耗时长、并行数据相位不一致的问题,提高测试设备开发效率;采取多种单元模块组合技术,利用fpga并行处理数据能力,解决控制设备反复编程的繁琐步骤,大大缩短设备开发人员的调试时间,提升开发效率。

技术特征:

1.一种基于fpga的任意波形发生装置,其特征在于,包括:

2.根据权利要求1所述的一种基于fpga的任意波形发生装置,其特征在于,所述通讯及源模块包括:

3.根据权利要求2所述的一种基于fpga的任意波形发生装置,其特征在于,所述fpga数据处理模块包括:

4.根据权利要求3所述的一种基于fpga的任意波形发生装置,其特征在于,所述数据包解码包括波形配置信息解码和数据参数信息解码;波形配置信息解码后的数据信息包括有效数据长度信息、周期分频信息和周期性使能信息;数据参数信息解码后的数据信息是在有效长度范围内,每一单位时钟内数字信息的具体参数值。

5.根据权利要求1所述的一种基于fpga的任意波形发生装置,其特征在于,所述数据处理包括波形数据预处理、波形数据校验、波形数据生成。

6.根据权利要求1所述的一种基于fpga的任意波形发生装置,其特征在于,所述底层驱动模块包括:

技术总结

本发明公开了一种基于FPGA的任意波形发生装置,包括通讯及源模块、FPGA数据处理模块和底层驱动模块。通讯及源模块用于接收上位机传输的数据及配置信息;FPGA数据处理模块用于对通讯及源模块接收的数据及配置信息进行数据包解码,解码后再进行数据处理,根据处理后的数据参数产生波形;底层驱动模块用于接收数据参数以及产生的波形,并根据接收的数据参数和波形驱动相应接口输出。本发明采取多种单元模块组合技术,利用FPGA并行处理数据能力,解决控制设备反复编程的繁琐步骤,大大缩短设备开发人员的调试时间,提升开发效率。

技术研发人员:王晨,金瑾,蔡宁霞,胡勇,余保华,唐琨,冉亮,周艳,吴文燕

受保护的技术使用者:四创电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!