一种数字逻辑电路的路径信息存储方法、系统及存储介质与流程

本申请涉及数字逻辑电路,尤其是涉及一种数字逻辑电路的路径信息存储方法、系统及存储介质。

背景技术:

1、随着数字逻辑电路的不断发展,数字逻辑电路的规模也在不断扩大,用户在设计数字逻辑电路的过程中,可以通过软硬件结合的方式编译得到大规模的数字逻辑电路。

2、随着电子科学技术的不断发展,芯片制造等集成电路技术也在不断发展。其中,就出现了采用rtl(regi ster transfer level,寄存器传输级)逻辑代码进行寄存器的逻辑设计。rtl是用于描述数字电路操作的抽象级。在rtl级,集成电路是由一组寄存器以及寄存器之间的逻辑操作构成。之所以如此,是因为绝大多数的电路可以被看成由寄存器来存储二进制数据、由寄存器之间的逻辑操作来完成数据的处理,数据处理的流程由时序状态机来控制,这些处理和控制可以用硬件描述语言来描述。基于此,在芯片设计中包括前端设计和后端设计。在前端设计中,逻辑综合负责将rtl代码映射至半导体制造厂商工艺技术库中的门级电路,进而形成门级网表。获取到完整的门级网表后,依据门级网表可以进行芯片后端设计,可见逻辑综合在芯片设计中发挥着承上启下作用。

3、相关技术中,一般采用展平式策略对rtl逻辑代码文件进行逻辑综合操作。也就是说,在对逻辑代码进行逻辑综合的过程中将芯片视为一个整体进行逻辑综合。但是,芯片中的数字逻辑电路元器件较多,对数字逻辑电路关键路径的选取过程中占用的存储空间较大,存在改进之处。

技术实现思路

1、为了减少数字逻辑电路关键路径的选取过程中占用的存储空间,本申请提供一种数字逻辑电路的路径信息存储方法、系统及存储介质。

2、第一方面,本申请提供的一种数字逻辑电路的路径信息存储方法,采用如下的技术方案:

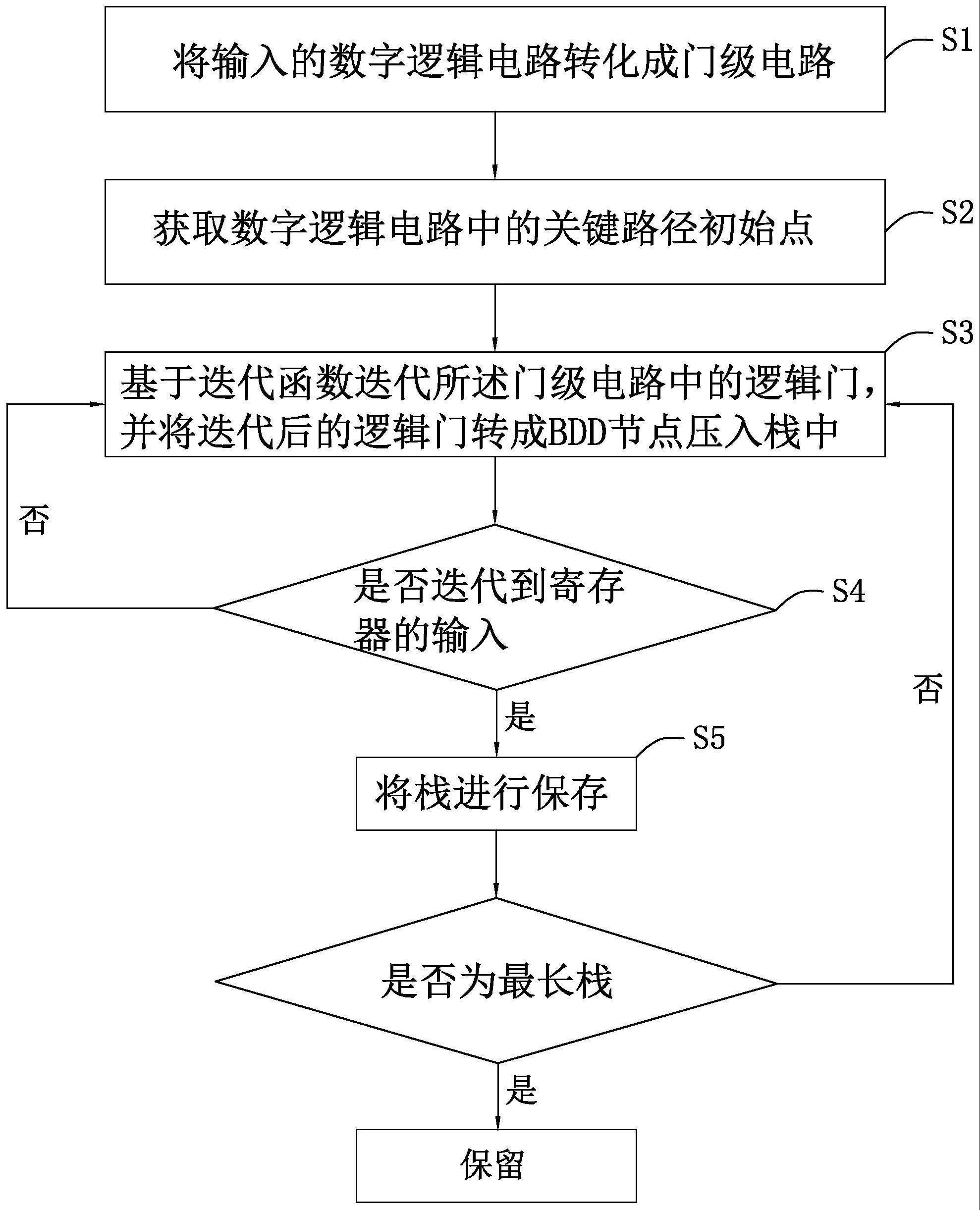

3、一种数字逻辑电路的路径信息存储方法,包括以下步骤:

4、将输入的数字逻辑电路转化成门级电路;

5、获取数字逻辑电路中的关键路径初始点;

6、基于迭代函数迭代所述门级电路中的逻辑门,并将迭代后的逻辑门转成bdd节点压入栈中;

7、判断是否迭代到寄存器的输入,若是,则将栈进行保存,若否则继续迭代;

8、判断保存的栈是否为最长栈,若是最长栈则保留,若不是最长栈则删除继续迭代,其中最长栈即为关键路径。

9、通过采用上述的技术方案,将数字逻辑电路的关键路径和重要信息通过栈的方式存储,提高了信息存储的效率,且由于通过门级电路表达电路逻辑,降低了单一逻辑门的存储占用率,只用布尔值表示节点信息,大大减少了存储电路逻辑占用的内存。

10、优选的,所述将输入的数字逻辑电路转化成门级电路的步骤,具体包括:

11、基于递归算法遍历输入的数字逻辑电路;

12、基于api算法将rtl级电路转换成门级电路,其中,所述门级电路即为只含有逻辑门的电路。

13、优选的,所述的获取数字逻辑电路中的关键路径初始点的步骤,具体包括:

14、获取数字逻辑电路中的寄存器;

15、将寄存器的输出作为起点创建关键路径的初始点。

16、优选的,所述的基于迭代函数迭代所述门级电路中的逻辑门,并将迭代后的逻辑门转成bdd节点压入栈中的步骤,具体包括:

17、将门级电路输出进入迭代函数中,从寄存器的输出开始迭代逻辑门;

18、通过逻辑门的输出迭代下一个相邻逻辑门;

19、将迭代过的逻辑门转化成与非门节点;

20、基于bdd算法将与非门节点压入栈中。

21、优选的,所述的判断保存的栈是否为最长栈的步骤,具体包括:

22、将保存后的栈与已有参考栈的长度进行对比,若保存后的栈长度大于已有的参考栈,替换已有的参考栈;

23、判断是否迭代完成起始寄存器的所有输出,若是则结束,若否则重复迭代直至完成起始寄存器的所有输出。

24、优选的,所述最长栈配置为栈中元素最多,所述最长栈标记为关键路径。

25、第二方面,本申请提供的一种数字逻辑电路的路径信息存储系统,采用如下的技术方案:

26、一种数字逻辑电路的路径信息存储系统,包括:

27、转化模块,配置为用于将输入的数字逻辑电路转化成门级电路;

28、关键路径初始点确定模块,配置为用于获取数字逻辑电路中的关键路径初始点;

29、迭代模块,配置为基于迭代函数迭代所述门级电路中的逻辑门,并将迭代后的逻辑门转成bdd节点压入栈中;

30、判断模块,配置为判断是否迭代到寄存器的输入,若是,则将栈进行保存,若否则继续迭代;

31、判断保存的栈是否为最长栈,若是最长栈则保留,若不是最长栈则删除继续迭代,其中最长栈即为关键路径。

32、第三方面,本申请提供一种计算机可读存储介质,采用如下的技术方案:

33、一种计算机可读存储介质,所述存储介质存储有至少一条指令、至少一段程序、代码集或指令集,所述至少一条指令、所述至少一段程序、所述代码集或指令集由所述处理器加载并执行以实现如上述的一种数字逻辑电路的路径信息存储方法。

34、综上所述,本申请包括以下至少一种有益技术效果:

35、1.将数字逻辑电路的关键路径和重要信息通过栈的方式存储,提高了信息存储的效率,且由于通过门级电路表达电路逻辑,降低了单一逻辑门的存储占用率,只用布尔值表示节点信息,大大减少了存储电路逻辑占用的内存。

技术特征:

1.一种数字逻辑电路的路径信息存储方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种数字逻辑电路的路径信息存储方法,其特征在于:所述将输入的数字逻辑电路转化成门级电路的步骤,具体包括:

3.根据权利要求1所述的一种数字逻辑电路的路径信息存储方法,其特征在于:所述的获取数字逻辑电路中的关键路径初始点的步骤,具体包括:

4.根据权利要求1所述的一种数字逻辑电路的路径信息存储方法,其特征在于:所述的基于迭代函数迭代所述门级电路中的逻辑门,并将迭代后的逻辑门转成bdd节点压入栈中的步骤,具体包括:

5.根据权利要求1所述的一种数字逻辑电路的路径信息存储方法,其特征在于:所述的判断保存的栈是否为最长栈的步骤,具体包括:

6.根据权利要求1所述的一种数字逻辑电路的路径信息存储方法,其特征在于:所述最长栈中的元素最多,所述最长栈标记为关键路径。

7.一种数字逻辑电路的路径信息存储系统,其特征在于,包括:

8.一种计算机可读存储介质,其特征在于:所述存储介质存储有至少一条指令、至少一段程序、代码集或指令集,所述至少一条指令、所述至少一段程序、所述代码集或指令集由所述处理器加载并执行以实现如权利要求1至6任一项所述的一种数字逻辑电路的路径信息存储方法。

技术总结

本申请公开了一种数字逻辑电路的路径信息存储方法、系统及存储介质,涉及数字逻辑电路技术领域,其包括将输入的数字逻辑电路转化成门级电路;获取数字逻辑电路中的关键路径初始点;基于迭代函数迭代所述门级电路中的逻辑门,并将迭代后的逻辑门转成BDD节点压入栈中;判断是否迭代到寄存器的输入,若是,则将栈进行保存,若否则继续迭代;判断保存的栈是否为最长栈,若是最长栈则保留,若不是最长栈则删除继续迭代,其中最长栈即为关键路径。本申请具有减少数字逻辑电路关键路径选取过程中存储的占用空间效果。

技术研发人员:赵然

受保护的技术使用者:赵然

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!