一种基于FPGA的CPCI总线多备份读写方法及EMMC卡与流程

本申请技术方案设计通讯控制领域,尤其涉及一种基于fpga的cpci总线多备份读写方法。本申请还涉及一种基于fpga的cpci总线多备份emmc卡。

背景技术:

1、pci(peripheralcomponentinterconnect)是由英特尔(intel)公司推出的用于定义局部总线的标准,带宽可达264mb/s(在32bit/66mhz下),是cpu系统总线中的一级总线,具有即插即用、中断共享易扩展等优点,在计算机体系中占据重要地位。

2、目前,在军用计算机体系中仍有大部分系统采用了cpci总线的扩展方式。emmc(embeddedmultimediacard)是mmc协会订立、主要针对手机或平板电脑等产品的内嵌式存储器标准规格。emmc内部集成了控制器,具有尺寸小、成本低、速度高和嵌入式非易失等特点。

3、现有技术中有采用pcie总线接口实现emc的扩展,及直接并口连接到arm芯片的应用方式,但在军用计算机体系中,cpci总线扩展形式的大型计算机体系仍在多数使用,在这些早起计算机体平台体系中很多没有多余的pcie总线,导致emmc卡无法满足cpci总线多设备扩展要求。

技术实现思路

1、为了解决上述背景技术中提出的一个或者多个问题,本申请提出一种基于fpga的cpci总线多备份读写方法。本申请还涉及一种基于fpga的cpci总线多备份emmc卡。

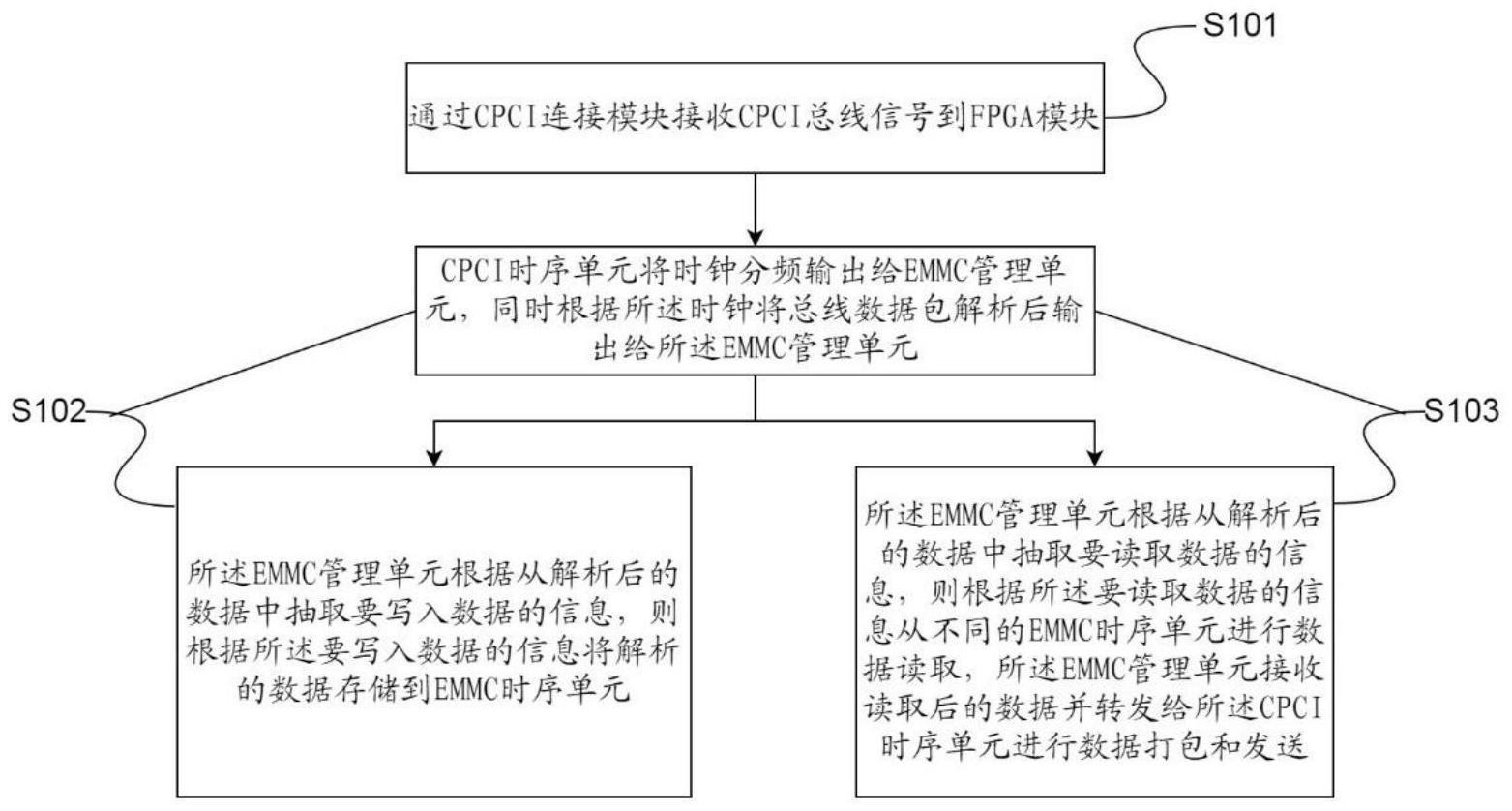

2、本申请提供一种基于fpga的cpci总线多备份读写方法,其特征在于,包括:通过cpci连接模块接收cpci总线信号到fpga模块;

3、在所述fpga模块中,根据所述总线信号执行如下步骤:

4、cpci时序单元将时钟分频输出给emmc管理单元,同时根据所述时钟将总线数据包解析后输出给所述emmc管理单元;

5、所述emmc管理单元根据从解析后的数据中抽取要写入数据的信息,则根据所述要写入数据的信息将解析的数据存储到emmc模块;

6、所述emmc管理单元根据从解析后的数据中抽取要读取数据的信息,则根据所述要读取数据的信息从不同的emmc模块进行数据读取,所述emmc管理单元接收读取后的数据并转发给所述cpci时序单元进行数据打包和发送。

7、可选的,所述cpci连接模块还接收电源信号;

8、根据所述电源信号,所述电源模块为emmc卡各个模块提高电能。

9、可选的,所述不同的emmc时序单元包括一个主emmc时序单元和多个从emmc时序单元。

10、可选的,所述从emmc时序单元至少包括两个。

11、可选的,至少一个所述从emmc时序单元接收备份数据。

12、本申请还提供一种基于fpga的cpci总线多备份emmc卡,包括:cpci连接模块、fpga模块和emmc模块;所述cpci连接模块连接fpga模块,所述fpga模块连接emmc模块;

13、所述cpci连接模块接收cpci总线信号转发到fpga模块;所述fpga模块包括:pll锁相环单元、cpci时序单元、emmc管理单元和emmc时序单元;所述cpci时序单元将时钟分频输出给emmc管理单元,同时根据所述时钟将总线数据包解析后输出给所述emmc管理单元;所述emmc管理单元根据从解析后的数据中抽取要写入数据的信息,则根据所述要写入数据的信息将解析的数据存储到emmc时序单元对应的emmc模块;所述emmc管理单元根据从解析后的数据中抽取要读取数据的信息,则根据所述要读取数据的信息从不同的emmc模块进行数据读取,所述emmc管理单元接收读取后的数据并转发给所述cpci时序单元进行数据打包和发送。

14、可选的,所述cpci连接模块还接收电源信号;

15、根据所述电源信号,所述电源模块为emmc卡各个模块提高电能。

16、可选的,所述不同的emmc时序单元包括一个主emmc时序单元和多个从emmc时序单元。

17、可选的,所述从emmc时序单元至少包括两个。

18、可选的,至少一个所述从emmc时序单元接收备份数据。

19、本申请相较于现有技术的优点是:

20、本申请提供一种基于fpga的cpci总线多备份读写方法,包括:通过cpci连接模块接收cpci总线信号到fpga模块;在所述fpga模块中,根据所述总线信号执行如下步骤:cpci时序单元将时钟分频输出给emmc管理单元,同时根据所述时钟将总线数据包解析后输出给所述emmc管理单元;所述emmc管理单元根据从解析后的数据中抽取要写入数据的信息,则根据所述要写入数据的信息将解析的数据存储到emmc模块;所述emmc管理单元根据从解析后的数据中抽取要读取数据的信息,则根据所述要读取数据的信息从不同的emmc模块进行数据读取,所述emmc管理单元接收读取后的数据并转发给所述cpci时序单元进行数据打包和发送。本申请通过在计算机体系中可实现cpci总线的多emmc扩展、主副控制及备份管理,满足cpci总线多设备扩展要求的同时,硬件电路简洁,实用性强。

技术特征:

1.一种基于fpga的cpci总线多备份读写方法,其特征在于,包括:通过cpci连接模块接收cpci总线信号到fpga模块;

2.根据权利要求1所述基于fpga的cpci总线多备份读写方法,其特征在于,所述cpci连接模块还接收电源信号;

3.根据权利要求1所述基于fpga的cpci总线多备份读写方法,其特征在于,所述不同的emmc时序单元包括一个主emmc时序单元和多个从emmc时序单元。

4.根据权利要求3所述基于fpga的cpci总线多备份读写方法,其特征在于,所述从emmc时序单元至少包括两个。

5.根据权利要求4所述基于fpga的cpci总线多备份读写方法,其特征在于,至少一个所述从emmc时序单元接收备份数据。

6.一种基于fpga的cpci总线多备份emmc卡,其特征在于,包括:cpci连接模块、fpga模块和emmc模块;所述cpci连接模块连接fpga模块,所述fpga模块连接emmc模块;

7.根据权利要求6所述基于fpga的cpci总线多备份emmc卡,其特征在于,所述cpci连接模块还接收电源信号;

8.根据权利要求6所述基于fpga的cpci总线多备份emmc卡,其特征在于,所述不同的emmc时序单元包括一个主emmc时序单元和多个从emmc时序单元。

9.根据权利要求8所述基于fpga的cpci总线多备份emmc卡,其特征在于,所述从emmc时序单元至少包括两个。

10.根据权利要求9所述基于fpga的cpci总线多备份emmc卡,其特征在于,至少一个所述从emmc时序单元接收备份数据。

技术总结

本申请提供的基于FPGA的CPCI总线多备份读写方法,包括:通过CPCI连接模块接收CPCI总线信号到FPGA模块;在所述FPGA模块中,CPCI时序单元将时钟分频输出给EMMC管理单元,根据所述时钟将总线数据包解析后输出给所述EMMC管理单元;所述EMMC管理单元从解析后的数据中抽取要写入数据的信息,则根据所述要写入数据的信息将解析的数据存储到EMMC模块;所述EMMC管理单元从解析后的数据中抽取要读取数据的信息,则根据所述要读取数据的信息从不同的EMMC模块进行数据读取,所述EMMC管理单元接收读取后的数据并转发给所述CPCI时序单元进行数据打包和发送。本申请通过在计算机体系中可实现CPCI总线的多EMMC扩展、主副控制及备份管理,满足CPCI总线多设备扩展要求的同时,硬件电路简洁,实用性强。

技术研发人员:周苗苗,刘怀怀,迟骋

受保护的技术使用者:天津市英贝特航天科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!