一种神经网络加速系统的制作方法

本公开属于专用算法硬件电路设计,具体而言涉及一种神经网络加速系统。

背景技术:

1、在人工智能领域,今年来卷积神经网络得到广泛应用。其基本结构如图结构示意图如图8所示,由输入层、隐藏层和输出层组成,前一层的输出特征数据作为后一层的输入特征,不断相后传递,直至得到网络的最终输出。位于输入层和输出层之间的隐藏层,根据应用场景的不同可以进一步细分为卷积层、池化层和全连接层等线性层,和relu、sigmoid等非线性层(亦称激活层)。

2、早期的硬件实现方法难以支持较大尺寸的池化窗口,通常需要进行多轮的较小尺寸的池化操作来实现较大尺寸的池化算子,这种实现方式会导致片外存储设备与池化加速单元之间的数据交互量超出原始数据量的若干倍,造成通信带宽紧张。当无法通过小尺寸池化完成时,就需要算法开发人员在保证算法精度的同时修改池化算子参数,给算法人员带来一定压力。

技术实现思路

1、本公开正是基于现有技术的上述需求而提出的,本公开要解决的技术问题是提供一种神经网络加速系统以缩短池化运算的耗时。

2、为了解决上述问题,本公开提供的技术方案包括:

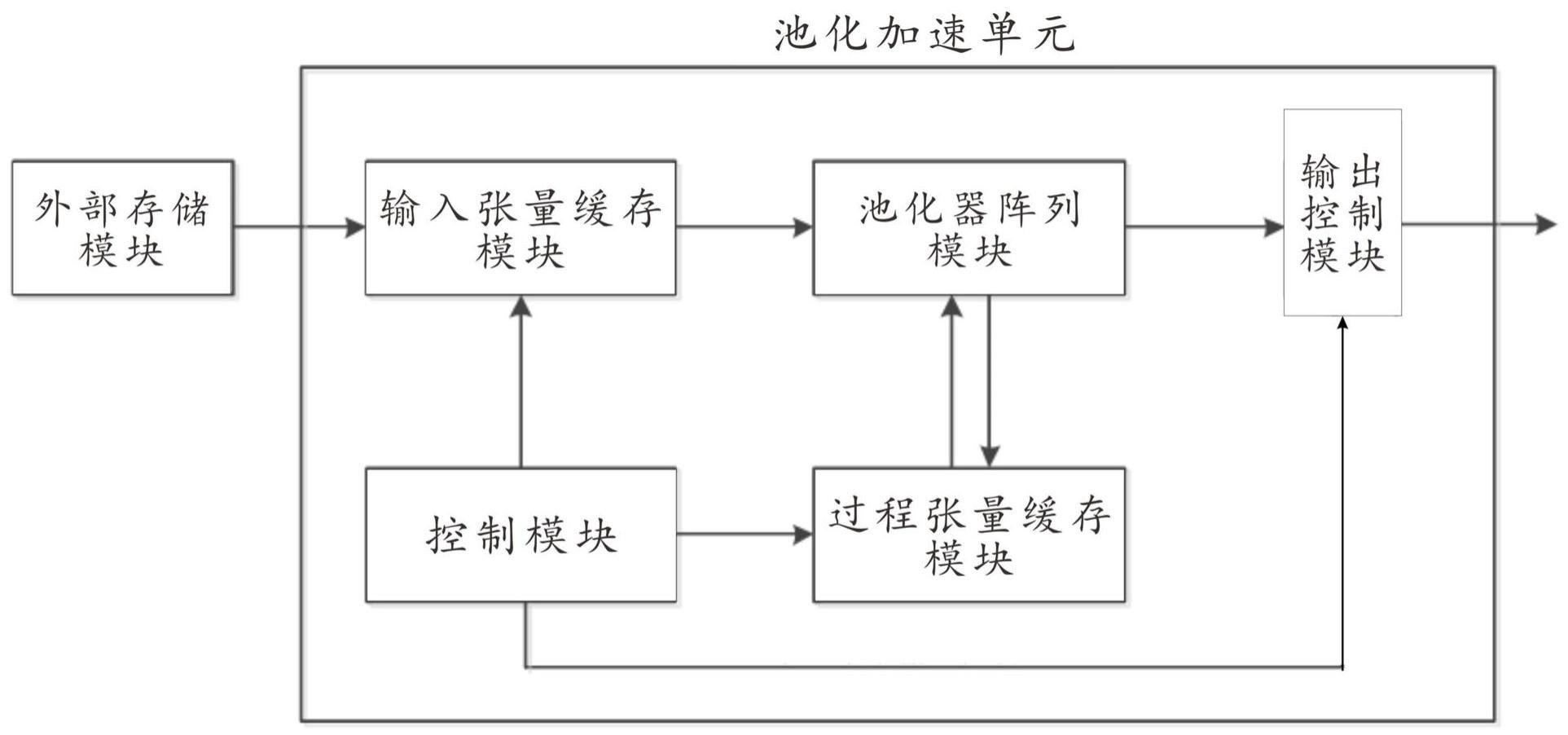

3、提供了一种神经网络加速系统,包括:信息配置模块,由外部设置信息配置模块的参数信息;外部存储模块;和池化加速单元,分别与信息配置模块和外部存储模块相连,所述池化加速单元包括:控制模块,所述控制模块根据所述信息配置模块的参数信息得到张量块的信息以及地址信息,所述张量块包括输入张量块和输出张量块;输入张量缓存模块,与所述控制模块相连,根据由控制模块得到的输入张量块地址信息缓存从外部存储模块的输入张量块;过程张量缓存模块,与所述控制模块相连,根据由控制模块得到的输出张量块地址信息缓存沿宽度方向池化的输出张量块,并提供沿高度方向池化的输入数据;池化器阵列模块,分别与输入张量缓存模块和过程张量缓存模块相连,进行宽度方向的池化和高度方向的池化,并沿通道方向进行并行计算。

4、优选的,所述参数信息包括池化层基本信息、输入张量块和输出张量块的相关信息;所述池化层基本信息包括:池化类型、池化窗口高度、池化窗口宽度、池化高度方向步长、池化宽度方向步长、输入数据高度方向边界补零信息和输入数据宽度方向边界补零信息;输入张量块相关信息包括:输入块位置序号、输入张量块高度、输入张量块宽度和输入通道数;输出张量块相关信息包括:输出张量块高度和输出张量块宽度。

5、优选的,所述外部存储模块的存储方式包括:将沿通道方向拆分成两个维度,分别为低维度的pdi和高维度的t;数据沿通道方向进行存储;当通道方向的数据存储达到pdi边界时,沿宽度方向进行存储;当宽度方向的数据存储达到宽度边界时,沿高度方向进行存储;当高度方向的数据存储达到高度边界时,沿通道方向向高纬度t进行存储。

6、优选的,所述控制模块根据所述信息配置模块的参数信息得到张量块的信息包括,基于所述参数信息和输出张量块元素的信息得到输入张量块元素的高度索引,所述输出张量块元素的信息包括由输出张量块进行四个维度的遍历得到的输出张量块元素的位置信息,所述输入张量块元素的高度索引表示为:其中,ntih为输入张量块元素的高度索引,ntoh为输出张量块元素的高度索引,sh为池化高度方向步长,kh为池化窗口高度,ph为输入数据高度方向边界补零信息,maxtih为输入张量块元素的高度索引的最大值。

7、优选的,所述控制模块根据所述信息配置模块的参数信息得到张量块的信息还包括,基于所述参数信息和输出张量块元素的信息得到输入张量块元素的宽度索引,所述输出张量块元素的信息包括由输出张量块进行四个维度的遍历得到的输出张量块元素的位置信息,所述输入张量块元素的宽度索引表示为:其中,ntiw为输入张量块元素的宽度索引,ntow为输出张量块元素的宽度索引,sw为池化宽度方向步长,kw为池化窗口宽度,pw为输入数据宽度方向边界补零信息,maxtiw输入张量块元素的宽度索引的最大值。

8、优选的,计算的输入特征元素的地址ai通过以下表达式得出:ai=nif×nih×niw+nih×niw+niw其中,nif为通道索引,nih和niw为特征元素在特征图中的坐标,nih为输入特征图的高度,niw为输入特征图的宽度。

9、优选的,所述池化加速单元从所述外部存储模块中每次获取pdi个张量块;所述池化器阵列模块包括pdi个池化器,所述pdi个池化器并行池化。

10、优选的,所述池化器阵列模块的处理包括:所述池化器阵列模块从输入张量缓存模块中获取输入特征数据,并进行宽度方向的池化,同时将过程数据存入到过程张量缓存模块中;所述池化器阵列模块从过程张量缓存模块中获取数据,并进行高度方向的池化;输出池化结果。

11、优选的,所述神经网络加速系统还包括输出控制模块,所述输出控制模块分别与池化器阵列模块和控制模块相连,根据所述控制模提供的信息将池化器阵列模块输出的池化结果输出至外部存储模块或通用互联接口。

12、优选的,所述输出控制模块输出的经池化后的输出特征矩阵表示为:

13、y(nof,noh,now)=func(x(nif,nih:nih+kh,niw:niw+kw))

14、其中,y()为输出控制模块输出的输出特征矩阵,y矩阵左上角元素在特征图内的位置是(noh,now)通道索引是nof,对于最大池化,func()代表max(),对于平均池化,func()代表average(),x()为为池化窗口内输入特征矩阵,x矩阵左上角元素在特征图内的位置是(nih,niw)通道索引是nif,kh为池化窗口内输入特征矩阵的高度,kw为池化窗口内输入特征矩阵的宽度。

15、与现有技术相比,本公开针对cnn中池化运算的特点,提出一种针对卷积神经网络池化操作硬件加速电路设计方法。以尽可能小的fpga资源消耗量,实现池化操作支持任意池化滑动步长、池化核尺寸与边界补零个数。其实现方式降低了输入数据从外部存储模块读取的次数,降低了数据通讯量与数据存取开销,因此缩短了池化运算的耗时,从而降低了池化操作的运算成本并提升其效率。

技术特征:

1.一种神经网络加速系统,其特征在于,包括:

2.根据权利要求1所述的一种神经网络加速系统,其特征在于,

3.根据权利要求1所述的一种神经网络加速系统,其特征在于,

4.根据权利要求3所述的一种神经网络加速系统,其特征在于,

5.根据权利要求4所述的一种神经网络加速系统,其特征在于,

6.根据权利要求5所述的一种神经网络加速系统,其特征在于,

7.根据权利要求1所述的一种神经网络加速系统,其特征在于,

8.根据权利要求1所述的一种神经网络加速系统,其特征在于,

9.根据权利要求1所述的一种神经网络加速系统,其特征在于,

10.根据权利要求9所述的一种神经网络加速系统,其特征在于,

技术总结

本公开属于专用算法硬件电路设计技术领域,具体而言涉及一种神经网络加速系统包括:信息配置模块;和池化加速单元包括:控制模块,控制模块根据信息配置模块的参数信息得到张量块的信息以及地址信息;输入张量缓存模块,与控制模块相连,根据由控制模块得到的输入张量块地址信息缓存从外部存储模块的输入张量块;过程张量缓存模块,与控制模块相连,根据由控制模块得到的输出张量块地址信息缓存沿宽度方向池化的输出张量块,并提供沿高度方向池化的输入数据;池化器阵列模块,分别与输入张量缓存模块和过程张量缓存模块相连,进行宽度方向的池化和高度方向的池化,并沿通道方向进行并行计算,以缩短池化耗时。

技术研发人员:周辉,王晓峰,谢宇嘉,李悦,赵雄波,吴松龄,盖一帆,路坤峰,李晓敏,张隽,弭寒光,董文杰,靳蕊溪,吴敏,赵冠杰,阳徽,费亚男,李洋,赵伟

受保护的技术使用者:北京航天自动控制研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!