一种基于FPGA的低速源同步数据位对齐校正方法与流程

本发明涉及数据传输领域。更具体地,涉及一种基于fpga的低速源同步数据位对齐校正方法。

背景技术:

1、源同步传输是一种发送端同时发送数据信号与时钟信号,接收端根据约定的时序在特定时钟变化沿对数据窗口进行采样的数据传输方式。由于信号传输路径不一致,数据信号线与采样时钟线的到达接收端的时间不能保持一致,导致接收端采样时会发生位置偏移,不能准确在数据窗口的中心位置进行采样,可能产生错误的采样数据,因此需要根据实际情况对接收数据进行相位调整。

技术实现思路

1、本发明的目的在于提供一种基于fpga的低速源同步数据位对齐校正方法,以解决相关技术存在的问题中的至少一个。

2、为达到上述目的,本发明采用下述技术方案:

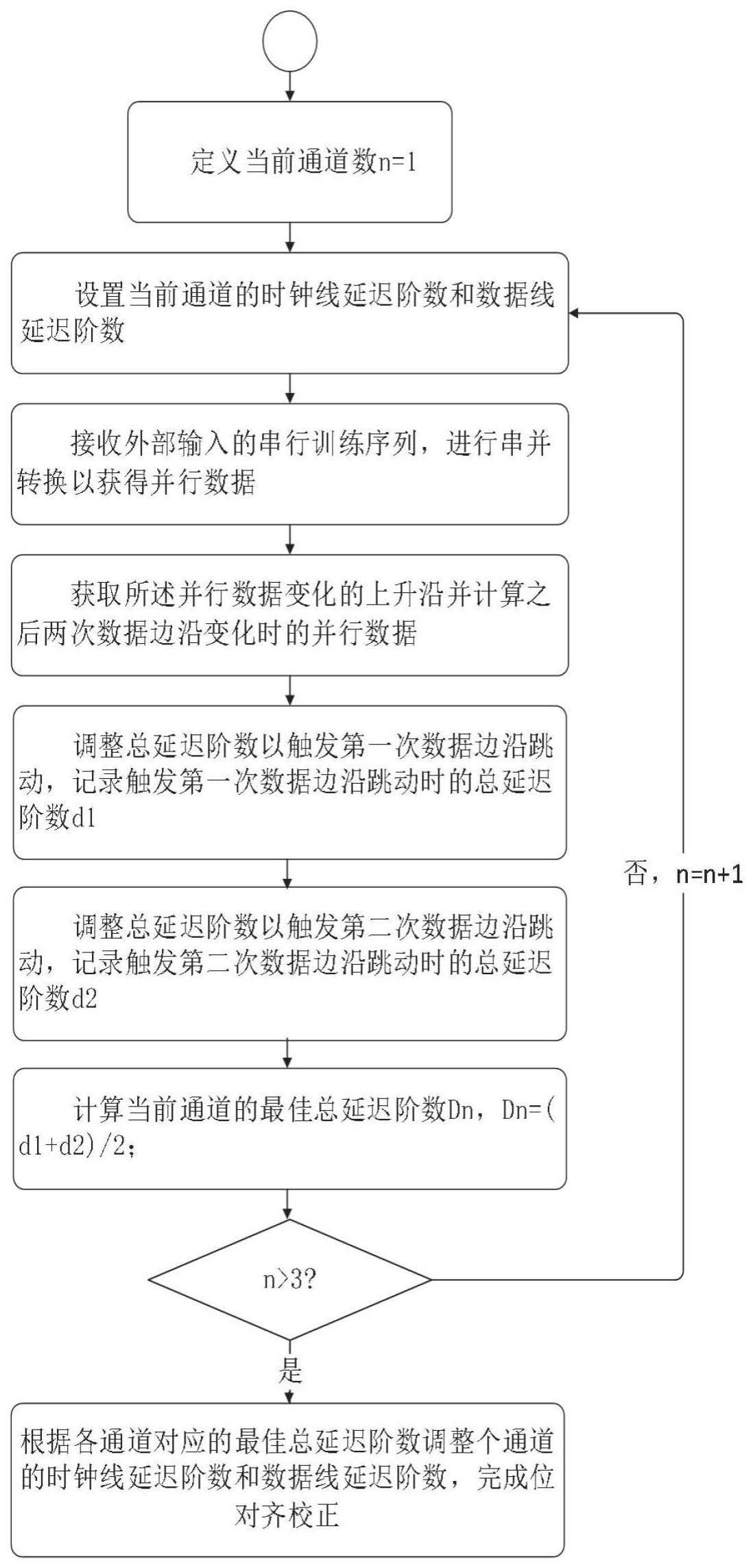

3、本发明第一方面提供了一种基于fpga的低速源同步数据位对齐校正方法,所述方法包括:

4、s10:设置第一通道的时钟线延迟阶数和数据线延迟阶数;

5、s20:接收外部输入的串行训练序列,进行串并转换以获得并行数据;

6、s30:获取所述并行数据变化的上升沿并计算之后两次数据边沿变化时的并行数据;

7、s40:调整总延迟阶数以触发第一次数据边沿跳动,记录触发第一次数据边沿跳动时的总延迟阶数d1;

8、调整总延迟阶数以触发第二次数据边沿跳动,记录触发第二次数据边沿跳动时的总延迟阶数d2;

9、计算当前通道的最佳总延迟阶数d1,d1=(d1+d2)/2;

10、s50:按照步骤s10-s40完成第二通道、第三通道和第四通道的对齐校正并获取对应的最佳总延迟阶数d2、d3和d4;

11、s60:根据各通道对应的最佳总延迟阶数调整各通道的始终现延迟阶数和数据线延迟阶数,完成位对齐校正。

12、可选地,所述根据各通道对应的最佳总延迟阶数调整各通道的始终现延迟阶数和数据线延迟阶数包括:

13、获取各通道对应最佳总延迟阶数的最小值dmin,判断dmin是否大于31,若大于,则设置各通道的时钟线延迟阶数为0,数据线延迟阶数为其对应最佳延迟阶数与最小值dmin的差值;若小于,则设置各通道的时钟线延迟阶数为62-dmin,数据线延迟阶数为其对应最佳延迟阶数与最小值dmin的差值。

14、可选地,对总延迟阶数进行调整包括:判断当前总延迟阶数加1后的大小是否大于31,若大于31,则将数据线延迟阶数加1,完成一次延迟阶数调整;若小于等于31,则将时钟线延迟阶数减1,完成一次延迟阶数调整。

15、可选地,步骤s10进一步包括:设置第一通道的时钟线延迟阶数为31;设置第一通道的数据线延迟阶数为0。

16、可选地,步骤s20进一步包括:接收外部发送的8bit串行训练序列0000_1111;

17、将接收到的8bit串行训练序列进行串并转换得到并行数据。

18、可选地,步骤s30进一步包括:将并行数据两两异或,若存在异或后值为1的结果则找到并行数据上升沿,记录当前含有上升沿的并行数据dat0;

19、将当前含有上升沿的并行数据dat0最低位作为之后第一次数据边沿变化时的并行数据结果dat1的最高位,将所述当前含有上升沿的并行数据dat0的所有比特右移1位作为之后第一次数据边沿变化时的并行数据结果dat1的剩余位;

20、将所述之后第一次数据边沿变化时的并行数据结果dat1的最低位作为之后第二次数据边沿变化时的并行数据结果dat2的最高位将所述之后第一次数据边沿变化时的并行数据结果dat1的所有比特右移1位作为之后第二次数据边沿变化时的并行数据结果dat2的剩余位。

21、可选地,步骤s40进一步包括:

22、s401:调整总延迟阶数,直至得到的串并转换结果与dat1相同,则视为触发了第一次边沿跳动,记录当前总延迟阶数d1;

23、s402:调整总延迟阶数,直至得到的串并转换结果与dat2相同,则视为触发了第二次边沿跳动,记录当前总延迟阶数d2。

24、本发明的有益效果如下:

25、本实施例提供的所述基于fpga的低速源同步数据位对齐校正方法无需得知源同步数据速率,在源同步数据速率未知的情况下能够自动计算最佳延迟值,进行动态相位调整;在含有多种数据速率的源同步传输应用场景下也无需进行内部参数修改,增强了系统通用性。

技术特征:

1.一种基于fpga的低速源同步数据位对齐校正方法,其特征在于,包括:

2.根据权利要求1所述的位对齐校正方法,其特征在于,

3.根据权利要求1所述的位对齐校正方法,其特征在于,

4.根据权利要求1所述的位对齐校正方法,其特征在于,

5.根据权利要求1所述的位对齐校正方法,其特征在于,

6.根据权利要求1所述的位对齐校正方法,其特征在于,

7.根据权利要求6所述的位对齐校正方法,其特征在于,

技术总结

本发明实施例公开一种基于FPGA的低速源同步数据位对齐校正方法,所述方法包括设置第一通道的时钟线延迟阶数和数据线延迟阶数;接收外部输入的串行训练序列,进行串并转换以获得并行数据;获取所述并行数据变化的上升沿并计算之后两次数据边沿变化时的并行数据;调整总延迟阶数以触发第一次数据边沿跳动,记录触发第一次数据边沿跳动时的总延迟阶数d1;调整总延迟阶数以触发第二次数据边沿跳动,记录触发第二次数据边沿跳动时的总延迟阶数d2;计算当前通道的最佳总延迟阶数D<subgt;1</subgt;,D<subgt;1</subgt;=(d1+d2)/2;重复上述步骤完成其他三个通道的对齐校正并获取对应的最佳总延迟阶数;根据各通道对应的最佳总延迟阶数调整各通道的时钟线延迟阶数和数据线延迟阶数。

技术研发人员:刘彰兴,韩斐

受保护的技术使用者:北京无线电测量研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!