一种基于结构描述方式HDL的数字逻辑电路仿真系统及装置

本发明涉及数字电路领域,具体而言,涉及一种基于结构描述方式hdl的数字逻辑电路仿真系统及装置。

背景技术:

1、随着智能化科技的不断发展,人们的生活、工作、学习之中越来越多地用到了智能化设备,使用智能化科技手段,提高了人们生活的质量,增加了人们学习和工作的效率。

2、现有的主流硬件描述语言(hdl)是ver i log和vhdl,根据这些语言规范产生各种仿真系统,时至今日,集成电路自动化设计工具eda早已是微电子技术中的核心技术,是现代集成系统设计的重要方法。其中商用级eda以三巨头cadence、synopsys、mentor为主,中国eda发展与国外差距巨大,同时市场也被国外所垄断。本发明的目的在于提供一整套开源免费的从硬件描述语言及其编译仿真的实现程序到配套的开发和管理平台,以满足数字电路教学及一般的个人开发需求。

3、针对上述的问题,目前尚未提出有效的解决方案。

技术实现思路

1、本发明实施例提供了一种基于结构描述方式hdl的数字逻辑电路仿真系统及装置,以至少解决现有的主流硬件描述语言(hdl)是ver i log和vhdl,根据这些语言规范产生各种仿真系统,但hdl语言及相关技术的运算量大,运算效率很低,无法支撑较大的运算项目和目标的技术问题。

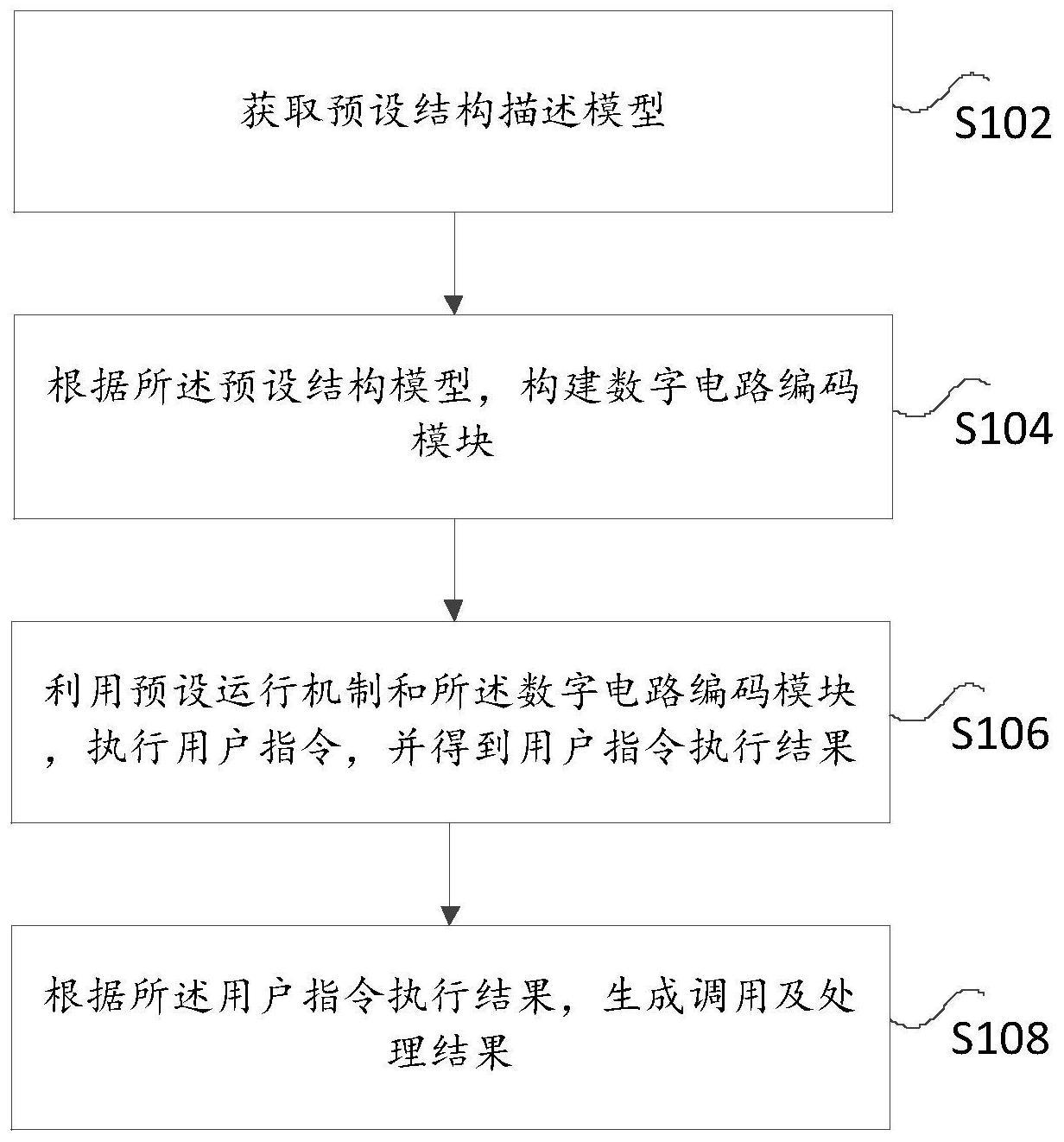

2、根据本发明实施例的一个方面,提供了一种基于结构描述方式hdl的数字逻辑电路仿真系统,包括:获取预设结构描述模型;根据所述预设结构模型,构建数字电路编码模块;利用预设运行机制和所述数字电路编码模块,执行用户指令,并得到用户指令执行结果;根据所述用户指令执行结果,生成调用及处理结果。

3、可选的,所述预设结构描述模型包括:操作台数据、图形化编程数据。

4、可选的,所述利用预设运行机制和所述数字电路编码模块,执行用户指令包括:根据所述预设结构模型,获取用户发出的所述用户指令;将所述用户指令在所述预设运行机制之上进行运行,得到所述用户指令执行结果。

5、可选的,所述预设运行机制包括:同时机制。

6、根据本发明实施例的另一方面,还提供了一种基于结构描述方式hdl的数字逻辑电路仿真装置,包括:获取模块,用于获取预设结构描述模型;构建模块,用于根据所述预设结构模型,构建数字电路编码模块;执行模块,用于利用预设运行机制和所述数字电路编码模块,执行用户指令,并得到用户指令执行结果;生成模块,用于根据所述用户指令执行结果,生成调用及处理结果。

7、可选的,所述预设结构描述模型包括:操作台数据、图形化编程数据。

8、可选的,所述执行模块包括:获取单元,用于根据所述预设结构模型,获取用户发出的所述用户指令;运行单元,用于将所述用户指令在所述预设运行机制之上进行运行,得到所述用户指令执行结果。

9、可选的,所述预设运行机制包括:同时机制。

10、根据本发明实施例的另一方面,还提供了一种非易失性存储介质,所述非易失性存储介质包括存储的程序,其中,所述程序运行时控制非易失性存储介质所在的设备执行一种基于结构描述方式hdl的数字逻辑电路仿真系统。

11、根据本发明实施例的另一方面,还提供了一种电子装置,包含处理器和存储器;所述存储器中存储有计算机可读指令,所述处理器用于运行所述计算机可读指令,其中,所述计算机可读指令运行时执行一种基于结构描述方式hdl的数字逻辑电路仿真系统。

12、在本发明实施例中,采用获取预设结构描述模型;根据所述预设结构模型,构建数字电路编码模块;利用预设运行机制和所述数字电路编码模块,执行用户指令,并得到用户指令执行结果;根据所述用户指令执行结果,生成调用及处理结果的方式,解决了现有的主流硬件描述语言(hdl)是ver i log和vhdl,根据这些语言规范产生各种仿真系统,但hdl语言及相关技术的运算量大,运算效率很低,无法支撑较大的运算项目和目标的技术问题。

技术特征:

1.一种基于结构描述方式hdl的数字逻辑电路仿真系统,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述预设结构描述模型包括:操作台数据、图形化编程数据。

3.根据权利要求1所述的方法,其特征在于,所述利用预设运行机制和所述数字电路编码模块,执行用户指令包括:

4.根据权利要求3所述的方法,其特征在于,所述预设运行机制包括:同时机制。

5.一种基于结构描述方式hdl的数字逻辑电路仿真装置,其特征在于,包括:

6.根据权利要求5所述的装置,其特征在于,所述预设结构描述模型包括:操作台数据、图形化编程数据。

7.根据权利要求5所述的装置,其特征在于,所述执行模块包括:

8.根据权利要求7所述的装置,其特征在于,所述预设运行机制包括:同时机制。

9.一种非易失性存储介质,其特征在于,所述非易失性存储介质包括存储的程序,其中,所述程序运行时控制非易失性存储介质所在的设备执行权利要求1至4中任意一项所述的系统。

10.一种电子装置,其特征在于,包含处理器和存储器;所述存储器中存储有计算机可读指令,所述处理器用于运行所述计算机可读指令,其中,所述计算机可读指令运行时执行权利要求1至4中任意一项所述的系统。

技术总结

本发明公开了一种基于结构描述方式HDL的数字逻辑电路仿真系统及装置。其中,该方法包括:获取预设结构描述模型;根据所述预设结构模型,构建数字电路编码模块;利用预设运行机制和所述数字电路编码模块,执行用户指令,并得到用户指令执行结果;根据所述用户指令执行结果,生成调用及处理结果。本发明解决了现有的主流硬件描述语言(HDL)是Verilog和VHDL,根据这些语言规范产生各种仿真系统,但HDL语言及相关技术的运算量大,运算效率很低,无法支撑较大的运算项目和目标的技术问题。

技术研发人员:姜顺清,黄牌牌,吕杰,严勇,党霞,刘德才

受保护的技术使用者:宁夏理工学院

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!