一种DDR5内存条上下电方法、装置、设备及介质与流程

本申请涉及计算机存储,特别是涉及一种ddr5内存条上下电方法、装置、设备及介质。

背景技术:

1、ddr5是一种计算机内存规格。与ddr4内存相比,ddr5标准性能更强,功耗更低。其电压从1.2v降低到1.1v,同时每通道32/40位(能实现错误检查和纠正,即errorcorrecting code,ecc)、总线效率提高、增加预取的bank group数量以改善性能等。与ddr4相比,改进的ddr5功能将使实际带宽提高36%,即使在3200mt/s(此声明必须进行测试)和4800mt/s速度开始,与ddr4-3200相比,实际带宽将高出87%。与此同时,ddr5最重要的特性之一是超过16gb的单片芯片密度。

2、ddr5双列直插式存储模块(dual-inline-memory-modules,dimm)的电源稳定性影响着ddr5 dimm的稳定性。而ddr5 dimm的稳定性又影响着整个服务器系统的稳定性。对于ddr5稳定性的常用测试方式是对ddr5dimm进行上下电操作,但这种上下电操作是基于服务器主板的上下电,服务器主板亦存在电源保护电路,上下电时会起到缓冲作用,未必会对ddr5dimm形成有效冲击,因此具有一定局限性。

3、鉴于上述问题,如何实现服务器系统中ddr5内存条的直接上下电,是该领域技术人员亟待解决的问题。

技术实现思路

1、本申请的目的是提供一种ddr5内存条上下电方法、装置、设备及介质,以实现服务器系统中ddr5内存条的直接上下电。

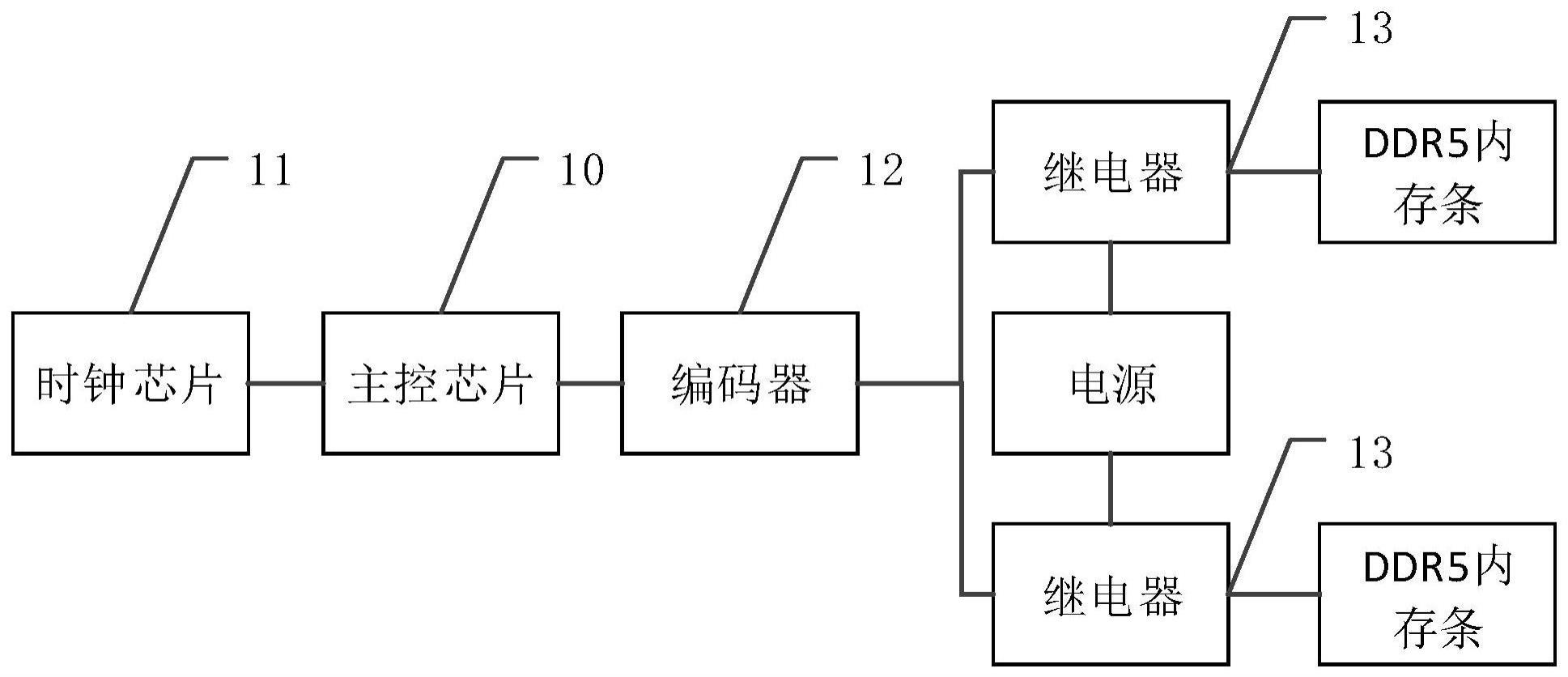

2、为解决上述技术问题,本申请提供一种ddr5内存条上下电方法,应用于ddr5内存条上下电系统;所述ddr5内存条上下电系统包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器;其中,所述继电器的数量与ddr5内存条的数量相同且一一对应;所述时钟芯片连接所述主控芯片;所述编码器连接所述主控芯片和各所述继电器;各所述继电器分别设置于对应的所述ddr5内存条与电源之间;所述方法包括:

3、获取各所述ddr5内存条的预设上下电信息,并接收所述时钟芯片传输的时间信息;

4、根据各所述预设上下电信息和所述时间信息传输控制信号至所述编码器,以用于所述编码器根据所述控制信号分别控制各所述继电器的导通情况,以分别控制各所述ddr5内存条上电或下电。

5、优选地,所述ddr5内存条上下电系统还包括上位机;

6、所述上位机连接所述主控芯片,用于设置所述预设上下电信息,并记录各所述ddr5内存条的上下电次数和上下电方式。

7、优选地,所述ddr5内存条上下电系统还包括按键装置;

8、所述按键装置连接所述主控芯片,用于设置所述预设上下电信息。

9、优选地,所述获取各所述ddr5内存条的预设上下电信息包括:

10、获取所述上位机传输的各所述ddr5内存条的所述预设上下电信息。

11、优选地,所述获取各所述ddr5内存条的预设上下电信息包括:

12、获取由所述按键装置设置的各所述ddr5内存条的所述预设上下电信息。

13、优选地,所述ddr5内存条上下电系统还包括显示装置;

14、所述显示装置连接所述主控芯片,用于显示各所述ddr5内存条的上下电状态。

15、优选地,所述继电器为电磁继电器。

16、为解决上述技术问题,本申请还提供一种ddr5内存条上下电装置,应用于ddr5内存条上下电系统;所述ddr5内存条上下电系统包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器;其中,所述继电器的数量与ddr5内存条的数量相同且一一对应;所述时钟芯片连接所述主控芯片;所述编码器连接所述主控芯片和各所述继电器;各所述继电器分别设置于对应的所述ddr5内存条与电源之间;所述装置包括:

17、获取接收模块,用于获取各所述ddr5内存条的预设上下电信息,并接收所述时钟芯片传输的时间信息;

18、控制信号传输模块,用于根据各所述预设上下电信息和所述时间信息传输控制信号至所述编码器,以用于所述编码器根据所述控制信号分别控制各所述继电器的导通情况,以分别控制各所述ddr5内存条上电或下电。

19、为解决上述技术问题,本申请还提供一种ddr5内存条上下电设备,包括:

20、存储器,用于存储计算机程序;

21、处理器,用于执行所述计算机程序时实现上述的ddr5内存条上下电方法的步骤。

22、为解决上述技术问题,本申请还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现上述的ddr5内存条上下电方法的步骤。

23、本申请所提供的ddr5内存条上下电方法,应用于ddr5内存条上下电系统;ddr5内存条上下电系统包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器;其中,继电器的数量与ddr5内存条的数量相同且一一对应;时钟芯片连接主控芯片;编码器连接主控芯片和各继电器;各继电器分别设置于对应的ddr5内存条与电源之间;方法具体通过获取各ddr5内存条的预设上下电信息,并接收时钟芯片传输的时间信息;根据各预设上下电信息和时间信息传输控制信号至编码器,以用于编码器根据控制信号分别控制各继电器的导通情况,以分别控制各ddr5内存条上电或下电。由此可知,上述方案无需进行内存条的插拔便实现了ddr5内存条直接的上下电,并能够根据预设上下电信息实现ddr5内存条多种方式的上电或下电,实现了在稳定性测试阶段对ddr5内存的更直接的冲击。

24、此外,本申请实施例还提供了一种ddr5内存条上下电装置、设备及介质,效果同上。

技术特征:

1.一种ddr5内存条上下电方法,其特征在于,应用于ddr5内存条上下电系统;所述ddr5内存条上下电系统包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器;其中,所述继电器的数量与ddr5内存条的数量相同且一一对应;所述时钟芯片连接所述主控芯片;所述编码器连接所述主控芯片和各所述继电器;各所述继电器分别设置于对应的所述ddr5内存条与电源之间;所述方法包括:

2.根据权利要求1所述的ddr5内存条上下电方法,其特征在于,所述ddr5内存条上下电系统还包括上位机;

3.根据权利要求1所述的ddr5内存条上下电方法,其特征在于,所述ddr5内存条上下电系统还包括按键装置;

4.根据权利要求2所述的ddr5内存条上下电方法,其特征在于,所述获取各所述ddr5内存条的预设上下电信息包括:

5.根据权利要求3所述的ddr5内存条上下电方法,其特征在于,所述获取各所述ddr5内存条的预设上下电信息包括:

6.根据权利要求1所述的ddr5内存条上下电方法,其特征在于,所述ddr5内存条上下电系统还包括显示装置;

7.根据权利要求1至6任意一项所述的ddr5内存条上下电方法,其特征在于,所述继电器为电磁继电器。

8.一种ddr5内存条上下电装置,其特征在于,应用于ddr5内存条上下电系统;所述ddr5内存条上下电系统包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器;其中,所述继电器的数量与ddr5内存条的数量相同且一一对应;所述时钟芯片连接所述主控芯片;所述编码器连接所述主控芯片和各所述继电器;各所述继电器分别设置于对应的所述ddr5内存条与电源之间;所述装置包括:

9.一种ddr5内存条上下电设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求1至7任一项所述的ddr5内存条上下电方法的步骤。

技术总结

本申请公开了一种DDR5内存条上下电方法、装置、设备及介质,涉及计算机存储技术领域。方法应用于包括设置有晶振的主控芯片、时钟芯片、编码器和多个继电器的DDR5内存条上下电系统。通过获取各DDR5内存条的预设上下电信息,并接收时钟芯片传输的时间信息;根据各预设上下电信息和时间信息传输控制信号至编码器,以用于编码器根据控制信号分别控制各继电器的导通情况,以分别控制各DDR5内存条上电或下电。由此可知,上述方案无需进行内存条的插拔便实现了DDR5内存条直接的上下电,并能够根据预设上下电信息实现DDR5内存条多种方式的上电或下电,实现了在稳定性测试阶段对DDR5内存的更直接的冲击。

技术研发人员:金霞,刘波,王兵,姚藩益

受保护的技术使用者:苏州浪潮智能科技有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!