一种基于软硬件协同的FPGA通用测试验证平台及方法与流程

本发明涉及集成电路,具体地,涉及一种基于软硬件协同的fpga通用测试验证平台及方法。

背景技术:

1、专用集成电路的设计与制造流程大体上可分为逻辑设计、逻辑模拟、版图生成、版图验证、制版、流片、封装等多个步骤。为了减少集成电路仿真所带来的不足,加速集成电路的研发过程,提高集成电路的正确率,通常将集成电路主体功能在fpga上实现,称作芯片原型,即待验证原型,并对其测试。

2、但随着集成电路应用场景越来越多,集成电路功能越来越复杂,集成电路的测试环境也变得非常复杂与庞大,所以如何提高测试环境的兼容性是本领域人员需要解决的问题。

技术实现思路

1、针对现有技术中存在的问题,本发明提供了一种基于软硬件协同的fpga通用测试验证平台及方法,可以提供复杂的测试验证环境以适应大规模复杂集成电路。

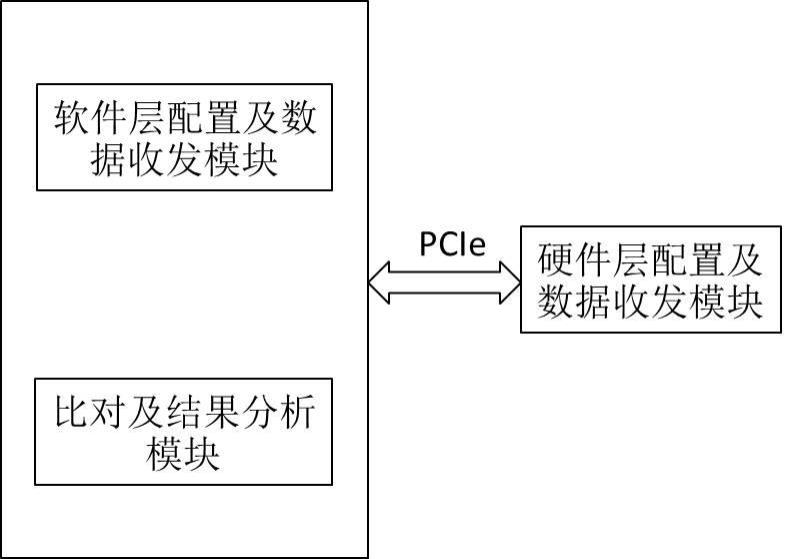

2、为实现上述技术目的,本发明采用如下技术方案:一种基于软硬件协同的fpga通用测试验证平台,包括:软件层配置及数据收发模块、硬件层配置及数据收发模块、比对及结果分析模块,所述软件层配置及数据收发模块与硬件层配置及数据收发模块连接,所述硬件层配置及数据收发模块与比对及结果分析模块连接;

3、所述软件层配置及数据收发模块用于根据用户选择下发对应的配置,使集成电路配置到相应的工作模式并运行;根据用户选择与配置要求、以及待验证fpga原型,下发对应的待测数据,并用于接收处理后的数据;

4、所述硬件层配置以及数据收发模块用于接收软件层配置及数据收发模块的数据与配置,完成后将待测数据进行存储,并将存储的待测数据读出发送给集成电路,接收集成电路处理后的数据,完成后将测试结果进行存储,并将存储的测试数据读出并发送给比对及结果分析模块;

5、所述比对及结果分析模块用于将接收的数据与标准数据进行对比,给出比对结果。

6、进一步地,所述软件层配置及数据收发模块与硬件层配置及数据收发模块通过pcie高速串行总线接口连接。

7、进一步地,所述硬件层配置及数据收发模块与比对及结果分析模块通过pcie高速串行总线接口连接。

8、进一步地,所述硬件层配置及数据收发模块包括:xdma模块、smart_connnect、配置缓存模块、第一数据缓存与协议转换模块、第二数据缓存与协议转换模块、ddr1存储器、ddr2存储器、待验证fpga原型,所述xdma模块通过axi-lite接口与smart_connnect连接,所述smart_connnect与配置缓存模块连接,所述配置缓存模块与待验证fpga原型通过配置接口连接;所述xdma模块通过axi-full接口与smart_connnect连接,所述smart_connnect与ddr1存储器连接,所述ddr1存储器与第一数据缓存与协议转换模块连接,所述第一数据缓存与协议转换模块与待验证fpga原型通过数据接口连接,所述待验证fpga原型与第二数据缓存与协议转换模块通过数据接口连接,所述第二数据缓存与协议转换模块与smart_connnect连接,所述smart_connnect与ddr2存储器连接。

9、进一步地,所述xdma模块与软件层配置及数据收发模块通过pcie高速串行总线接口连接。

10、进一步地,所述xdma模块与结果分析模块通过pcie高速串行总线接口连接。

11、进一步地,本发明还提供了基于软硬件协同的fpga通用测试验证平台的测试验证方法,具体包括如下步骤:

12、(1)通过自动生成或者手动输入的方式在软件层配置及数据收发模块输入待验证fpga原型的配置信息后,将配置信息通过pcie高速串行总线接口发送至xdma模块,转化为axi-lite协议,通过smart_connnect分配至配置缓存模块中缓存,缓存后将配置信息转化为适合待验证fpga原型配置接口的协议发送给待验证fpga原型以对待验证fpga原型进行配置;

13、(2)配置完成后,将待测数据通过pcie高速串行总线接口发送至xdma模块转化为axi-full协议,并通过smart_connnect分配存储至ddr1存储器中,存满后读出分配至第一数据缓存与协议转换模块中,将数据转化为适合待验证fpga原型数据接口的协议并输入待测数据,等待验证fpga原型将待测试数据处理完成后,将测试结果发送至第二数据缓存与协议转换模块,转化为axi-full通过smart_connect分配至ddr2 存储器中暂存,存满后读出再通过smart_connect分配至xdma转化为pcie发送至比对及结果分析模块;

14、(3)比对及结果分析模块接收到结果数据后,将结果数据与标准数据比对,并将比对结果显示。

15、与现有技术相比,本发明具有如下有益效果:本发明基于软硬件协同的fpga通用测试验证平台在软件层配置及数据收发模块与硬件层配置及数据收发模块通过pcie高速串行总线接口连接,提供了软件层通信接口,提出了对于不同芯片原型的硬件层数据流向;本发明基于软硬协同的fpga通用测试验证平台将待测试原型的工作状态信息通过配置接口可返回至配置缓存模块,再通过axi-lite接口与smart-connect、xdma模块、pcie接口返回至软件层配置及数据收发模块,该软件层配置及数据收发模块可根据待测试原型的工作状态判断下一步应配置的信息与应发送的待测数据,使得软件层配置及数据收发模块可以实时监控待测试原型的工作反馈状态并对此进行调控以达到适应多种复杂环境的效果。

技术特征:

1.一种基于软硬件协同的fpga通用测试验证平台,其特征在于,包括:软件层配置及数据收发模块、硬件层配置及数据收发模块、比对及结果分析模块,所述软件层配置及数据收发模块与硬件层配置及数据收发模块连接,所述硬件层配置及数据收发模块与比对及结果分析模块连接;

2.根据权利要求1所述基于软硬件协同的fpga通用测试验证平台,其特征在于,所述软件层配置及数据收发模块与硬件层配置及数据收发模块通过pcie高速串行总线接口连接。

3.根据权利要求1所述基于软硬件协同的fpga通用测试验证平台,其特征在于,所述硬件层配置及数据收发模块与比对及结果分析模块通过pcie高速串行总线接口连接。

4.根据权利要求1所述基于软硬件协同的fpga通用测试验证平台,其特征在于,所述硬件层配置及数据收发模块包括:xdma模块、smart_connnect、配置缓存模块、第一数据缓存与协议转换模块、第二数据缓存与协议转换模块、ddr1存储器、ddr2存储器、待验证fpga原型,所述xdma模块通过axi-lite接口与smart_connnect连接,所述smart_connnect与配置缓存模块连接,所述配置缓存模块与待验证fpga原型通过配置接口连接;所述xdma模块通过axi-full接口与smart_connnect连接,所述smart_connnect与ddr1存储器连接,所述ddr1存储器与第一数据缓存与协议转换模块连接,所述第一数据缓存与协议转换模块与待验证fpga原型通过数据接口连接,所述待验证fpga原型与第二数据缓存与协议转换模块通过数据接口连接,所述第二数据缓存与协议转换模块与smart_connnect连接,所述smart_connnect与ddr2存储器连接。

5.根据权利要求4所述基于软硬件协同的fpga通用测试验证平台,其特征在于,所述xdma模块与软件层配置及数据收发模块通过pcie高速串行总线接口连接。

6.根据权利要求4所述基于软硬件协同的fpga通用测试验证平台,其特征在于,所述xdma模块与结果分析模块通过pcie高速串行总线接口连接。

7.一种权利要求1-6任一项所述基于软硬件协同的fpga通用测试验证平台的测试验证方法,其特征在于,具体包括如下步骤:

技术总结

本发明公开了一种基于软硬件协同的FPGA通用测试验证平台及方法,涉及集成电路技术领域。该FPGA通用测试验证平台包括:软件层配置及数据收发模块、硬件层配置及数据收发模块、结果分析模块,所述软件层配置及数据收发模块与硬件层配置及数据收发模块连接,所述硬件层配置及数据收发模块与结果分析模块连接。本发明的FPGA通用测试验证平台可以提供复杂的测试验证环境以适应大规模复杂集成电路。

技术研发人员:郭杰,侯天祥,邢锴,曲天翔,段仲琦

受保护的技术使用者:南京炻燃光电科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!