一种APS切换方法、装置、电子设备及计算机可读存储介质与流程

本申请涉及通讯,具体而言,涉及一种aps切换方法、装置、电子设备及计算机可读存储介质。

背景技术:

1、现有技术中,针对批量自动保护切换(automatic protection switching,简称:aps)组的切换,需要cpu占用大量的i/o资源,针对每个aps组进行逐个修改,进而完成工作路径与保护路径的切换,导致切换效率较低。

技术实现思路

1、本申请的目的在于提供一种aps切换方法、装置、电子设备及计算机可读存储介质,用于提高aps组路径切换的效率。

2、为了实现上述目的,本申请实施例采用的技术方案如下:

3、第一方面,本申请实施例提供一种aps切换方法,所述方法应用于cpu,所述cpu与dma控制器通讯连接,所述方法包括:

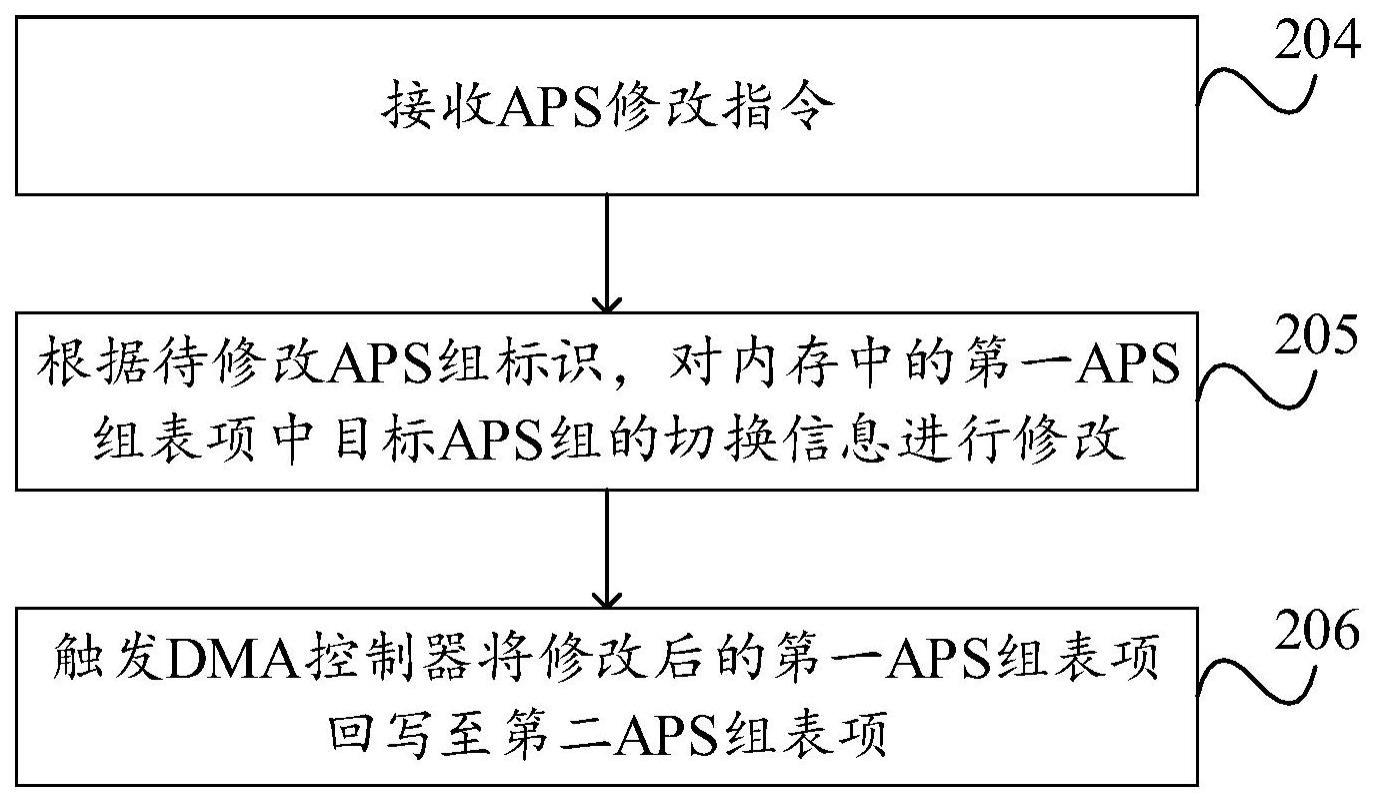

4、接收aps修改指令,所述aps修改指令用于指示待修改aps组标识;所述待修改aps组标识表征对应的目标aps组是否进行切换;

5、根据所述待修改aps组标识,对内存中的第一aps组表项中所述目标aps组的切换信息进行修改;其中,所述第一aps组表项包含全部aps组对应的切换信息;所述第一aps组表项存储于所述内存中连续物理地址上;所述第一aps组表项与所述交换芯片包含的第二aps组表项一对一映射;所述第二aps组表项存储于所述交换芯片中连续物理地址上;

6、触发所述dma控制器将修改后的第一aps组表项回写至所述第二aps组表项。

7、结合第一方面,在第一种可能的实现方式中,在所述接收aps修改指令的步骤之前,还包括:

8、触发所述dma控制器读取所述第二aps组表项;

9、根据所述第二aps组表项生成所述第一aps组表项。

10、结合第一方面,在第二种可能的实现方式中,在所述接收aps修改指令的步骤之前,还包括:

11、根据所述第一aps组表项中每个aps组的切换信息,生成比特数组;所述比特数组中的每一位与一个所述切换信息对应;

12、所述接收aps修改指令的步骤,包括:

13、根据sdk接口层输出所述比特数组;

14、接收基于所述比特数组确定的所述aps修改指令。

15、结合第一方面的第二种可能的实现方式,在第三种可能的实现方式中,还包括:

16、将所述比特数组存储与所述内存中。

17、第二方面,本申请实施例提供一种aps切换装置,包含cpu、dma控制器及交换芯片;其中,所述cpu与dma控制器通讯连接;

18、所述cpu,用于接收aps修改指令,所述aps修改指令用于指示待修改aps组标识;所述待修改aps组标识表征对应的目标aps组是否进行切换;根据所述待修改aps组标识,对内存中的第一aps组表项中所述目标aps组的切换信息进行修改;其中,所述第一aps组表项包含全部aps组对应的切换信息;所述第一aps组表项存储于所述内存中连续物理地址上;所述第一aps组表项与所述交换芯片包含的第二aps组表项一对一映射;所述第二aps组表项存储于所述交换芯片中连续物理地址上;触发所述dma控制器将修改后的第一aps组表项回写至所述第二aps组表项。

19、结合第二方面,在第一种可能的实现方式中,所述cpu,还用于在所述接收aps修改指令的之前,触发所述dma控制器读取所述第二aps组表项;

20、根据所述第二aps组表项生成所述第一aps组表项。

21、结合第二方面,在第二种可能的实现方式中,所述cpu,还用于在所述接收aps修改指令之前,根据所述第一aps组表项中每个aps组的切换信息,生成比特数组;所述比特数组中的每一位与一个所述切换信息对应;根据sdk接口层输出所述比特数组;接收基于所述比特数组确定的所述aps修改指令。

22、结合第二方面的第二种可能的实现方式,在第三种可能的实现方式中,所述cpu,还用于将所述比特数组存储与所述内存中。

23、第三方面,本申请实施例提供一种电子设备,包括:

24、存储器,用于存储一个或多个程序;

25、处理器;

26、当所述一个或多个程序被所述处理器执行时,实现如第一方面及任意一种可能的实现方式中所述的方法。

27、第四方面,本申请实施例提供一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该计算机程序被处理器执行时实现如第一方面及任意一种可能的实现方式中所述的方法。

28、相对于现有技术,本申请实施例所提供的一种aps切换方法、装置、电子设备及计算机可读存储介质,由于由cpu修改内存中的第一aps组表项,对于10k的aps组表项修改,常规cpu的性能上可以确保这个操作耗时在10m以内。进而对于交换芯片的第二aps组表项读写,均由dma控制器完成,dma无需cpu i/o操作,耗时很短。进而10k的aps倒换可以控制在10ms左右。同时,该方案可以针对一个aps组、多个不连续的aps组或连续的aps组等不同场景,从而提高了场景的适配性。

29、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种aps切换方法,其特征在于,所述方法应用于cpu,所述cpu与dma控制器通讯连接,所述方法包括:

2.如权利要求1所述的方法,其特征在于,在所述接收aps修改指令的步骤之前,还包括:

3.如权利要求1所述的方法,其特征在于,在所述接收aps修改指令的步骤之前,还包括:

4.如权利要求3所述的方法,其特征在于,还包括:

5.一种aps切换装置,其特征在于,包含cpu、dma控制器及交换芯片;其中,所述cpu与dma控制器通讯连接;

6.如权利要求5所述的装置,其特征在于,所述cpu,还用于在所述接收aps修改指令的之前,触发所述dma控制器读取所述第二aps组表项;

7.如权利要求5所述的装置,其特征在于,所述cpu,还用于在所述接收aps修改指令之前,根据所述第一aps组表项中每个aps组的切换信息,生成比特数组;所述比特数组中的每一位与一个所述切换信息对应;根据sdk接口层输出所述比特数组;接收基于所述比特数组确定的所述aps修改指令。

8.如权利要求7所述的装置,其特征在于,所述cpu,还用于将所述比特数组存储与所述内存中。

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该计算机程序被处理器执行时实现如权利要求1-5中任一项所述的方法。

技术总结

本申请提出一种APS切换方法、装置、电子设备及计算机可读存储介质,由于由CPU修改内存中的第一APS组表项,对于10K的APS组表项修改,常规CPU的性能上可以确保这个操作耗时在10m以内。进而对于交换芯片的第二APS组表项读写,均由DMA控制器完成,DMA无需CPU I/O操作,耗时很短。进而10K的APS倒换可以控制在10ms左右。同时,该方案可以针对一个APS组、多个不连续的APS组或连续的APS组等不同场景,从而提高了场景的适配性。

技术研发人员:胥平春,张思渊,孟忠伟

受保护的技术使用者:苏州盛科科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!