芯片时钟的测试方法、装置、存储介质及电子设备与流程

本申请涉及电子设备,具体涉及一种芯片时钟的测试方法、装置、存储介质及电子设备。

背景技术:

1、电子设备如智能手机、平板电脑等,其芯片在切换到不同的用户场景运行时,相关的时钟(clock)的频率会发生相应变化。其中,时钟寄存器是这种变化的控制开关。为了适应多种场景的使用需求,手机芯片的时钟寄存器的数量可以多达数千个,每个时钟寄存器的功能场景通常有十几种。

2、在芯片投片生产之前,在芯片测试(chip verification,cv)环节,需要确认这些时钟寄存器的功能是否符合预期。由于时钟寄存器的数量和功能场景的数量都非常大,常规的测试方案是,cv工程师根据经验选择少部分的时钟进行人工测试,不仅测试效率低,而且这种测试方式只能覆盖少部分的时钟,导致芯片的时钟不能得到充分验证,使得芯片流片埋下隐患。

技术实现思路

1、本申请实施例提供一种芯片时钟的测试方法、装置、存储介质及电子设备,能够提高电子设备的芯片时钟的测试效率和测试覆盖度。

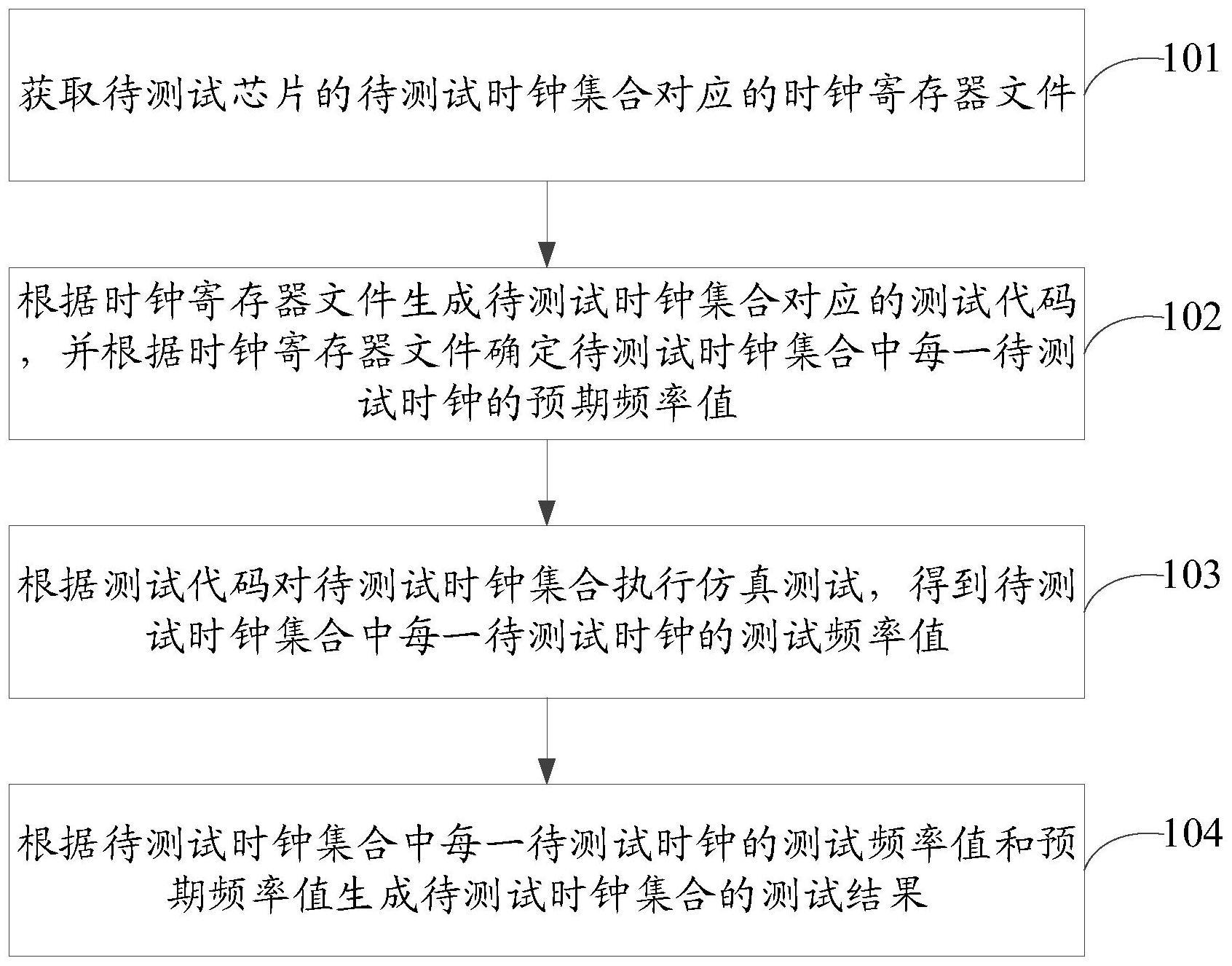

2、第一方面,本申请实施例提供一种芯片时钟的测试方法,包括:

3、获取待测试芯片的待测试时钟集合对应的时钟寄存器文件;

4、根据所述时钟寄存器文件生成所述待测试时钟集合对应的测试代码,并根据所述时钟寄存器文件确定所述待测试时钟集合中每一待测试时钟的预期频率值;

5、根据所述测试代码对所述待测试时钟集合执行仿真测试,得到所述待测试时钟集合中每一待测试时钟的测试频率值;

6、根据所述待测试时钟集合中每一待测试时钟的所述测试频率值和所述预期频率值生成所述待测试时钟集合的测试结果。

7、第二方面,本申请实施例还提供一种芯片时钟的测试装置,包括:

8、获取模块,用于获取待测试芯片的待测试时钟集合对应的时钟寄存器文件;

9、第一生成模块,用于根据所述时钟寄存器文件生成所述待测试时钟集合对应的测试代码,并根据所述时钟寄存器文件确定所述待测试时钟集合中每一待测试时钟的预期频率值;

10、测试模块,用于根据所述测试代码对所述待测试时钟集合执行仿真测试,得到所述待测试时钟集合中每一待测试时钟的测试频率值;

11、第二生成模块,用于根据所述待测试时钟集合中每一待测试时钟的所述测试频率值和所述预期频率值生成所述待测试时钟集合的测试结果。

12、第三方面,本申请实施例还提供一种计算机可读存储介质,其上存储有计算机程序,当所述计算机程序在计算机上运行时,使得所述计算机执行如本申请任一实施例提供的芯片时钟的测试方法。

13、第四方面,本申请实施例还提供一种电子设备,包括处理器和存储器,所述存储器有计算机程序,所述处理器通过调用所述计算机程序,用于执行如本申请任一实施例提供的芯片时钟的测试方法。

14、本申请实施例提供的技术方案,在对待测试芯片的时钟进行测试时,获取待测试芯片的待测试时钟集合对应的时钟寄存器文件,根据该时钟寄存器文件生成该待时钟集合的测试代码,并确定待测试时钟集合中每一待测试时钟的预期频率值,然后根据该测试代码对待测试时钟集合进行仿真测试,得到待测试时钟集合中每一待测试时钟的测试频率值,根据待测试时钟集合中每一待测试时钟的测试频率值和预期频率值生成待测试时钟集合的测试结果。通过该方案实现了芯片的时钟的自动化测试,提高了测试效率和测试覆盖度。

技术特征:

1.一种芯片时钟的测试方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,所述获取待测试芯片的待测试时钟集合对应的时钟寄存器文件,包括:

3.如权利要求1所述的方法,其特征在于,所述时钟寄存器文件包括待测试时钟集合中的每一待测试时钟的寄存器描述信息;

4.如权利要求1所述的方法,其特征在于,所述根据所述测试代码对所述待测试时钟集合执行仿真测试,得到所述待测试时钟集合中每一待测试时钟的测试频率值,包括:

5.如权利要求4所述的方法,其特征在于,所述调用所述仿真设备,根据所述测试执行文件对所述待测试时钟集合执行仿真测试,得到所述待测试时钟集合中每一待测试时钟的测试频率值,包括:

6.如权利要求4所述的方法,其特征在于,所述时钟寄存器文件包括待测试时钟集合中的每一待测试时钟的寄存器描述信息;

7.如权利要求4所述的方法,其特征在于,所述根据所述待测试时钟集合中每一待测试时钟的所述测试频率值和所述预期频率值生成所述待测试时钟集合的测试结果,包括:

8.一种芯片时钟的测试装置,其特征在于,包括:

9.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,当所述计算机程序在计算机上运行时,使得所述计算机执行如权利要求1至7任一项所述的芯片时钟的测试方法。

10.一种电子设备,包括处理器和存储器,所述存储器存储有计算机程序,其特征在于,所述处理器通过调用所述计算机程序,用于执行如权利要求1至7任一项所述的芯片时钟的测试方法。

技术总结

本申请实施例公开了一种芯片时钟的测试方法、装置、存储介质及电子设备,其中,本申请实施例获取待测试芯片的待测试时钟集合对应的时钟寄存器文件,根据该时钟寄存器文件生成该待时钟集合的测试代码,并确定待测试时钟集合中每一待测试时钟的预期频率值,然后根据该测试代码对待测试时钟集合进行仿真测试,得到待测试时钟集合中每一待测试时钟的测试频率值,根据待测试时钟集合中每一待测试时钟的测试频率值和预期频率值生成待测试时钟集合的测试结果。通过该方案实现了芯片的时钟的自动化测试,提高了测试效率和测试覆盖度。

技术研发人员:徐辉辉,王大宇

受保护的技术使用者:哲库科技(上海)有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!