一种支持三路输入的电源选择电路的制作方法

本技术为电源选择电路,在电源管理系统中起着至关重要的作用,属于模拟电路设计领域。

背景技术:

1、现在的芯片根据子系统的功耗和精度等要求不一样,一般都内置多个ldo(低压差线性稳压器),因此会出现多个内部电源,从而产生一些电路电源需要在不同模式下从不同的ldo供电的需求,这些电源电路的功率管的栅极控制信号以及衬底连接需要保证是最高电平,才能防止各种异常短路和漏电的发生,因此设计能在多个电源电压之间产生最高电平电源的电路是很有必要的。

2、以前的电源选择电路主要集中在vbat和vcc的选择,通常都是两个电源之间的选择电路,如果进行三路输入电源的选择可以将原先的两路电源选择级联使用,但是会造成选择开关串联使用,跟本发明的三路输入的电源选择电路相比,相同的开关尺寸和负载电流情况下,两路电源选择级联使用在开关管上的损耗是本发明的两倍;同时出于噪声和可靠性的考虑,电源选择比较一般具有迟滞窗口,迟滞窗口覆盖噪声的幅度,其造成的后果是选择出来的最高电平可能不是最高电平,比实际的最高电平低,在相同的噪声考虑情况下,两路电源选择级联使用时将迟滞电压叠加了两倍,因此其选择出来的最高电平比实际最高电平低的电压值是本专利的两倍。

3、本发明所涉及的三路输入的电源选择电路直接对三路电源输入进行比较判决并控制开关管,可以降低开关管的尺寸要求,并保证选择出来的最高电平值误差小。

技术实现思路

1、(1)发明目的

2、传统电源选择电路一般只给出两路电源选择结构,对于多路电源一般只给开关管的连接方式和选择目标,并未给出多路电源的高电平如何进行选择,对于三路输入电源虽然可以采用传统的两个电源选择电路,先在两路电源之间进行选择,将选择的结果与第三路电源再进行一次选择,由于最终的输出是两级开关管串联,因此电源开关损耗大,如果要减小损耗则需要加大电源开关的宽长比,增加面积,同时,由于叠加了两次比较结果,造成比较迟滞窗口增大了一倍,造成选择出来的最高电平误差大。本人发明了一种支持三路输入的电源选择电路,可以减小开关的损耗和选择误差。

3、(2)技术方案

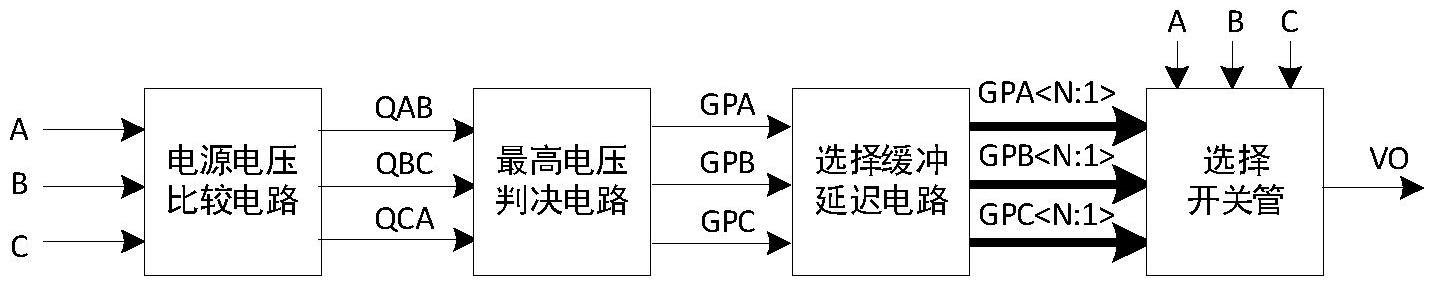

4、三个输入电源a/b/c输入到电源电压比较电路,实现对三个输入电源的大小进行比较,电源电压比较电路内置三个比较器模块,cmp1、cmp2和cmp3,其中,cmp1的正端和负端分别连接电源a和电源b,cmp2的正端和负端分别连接电源b和电源c,cmp3的正端和负端分别连接电源c和电源a;cmp1的输出qab表征a和b的比较结果,qab=1代表a比b高,qab=0代表a比b低,cmp2的输出qbc表征b和c的比较结果,qbc=1代表b比c高,qbc=0代表b比c低,cmp3的输出qca表征c和a的比较结果,qca=1代表c比a高,qca=0代表c比a低,并将比较的结果输出给下一级最高电压判决电路。其中,内置的比较器模块由迟滞比较器、掉电上拉支路以及整形反相器组成,其中掉电上拉支路为在迟滞比较器的输出和电源电压之间连接2个栅极连接输入信号的pmos管串连组成,用于在该比较器的两个输入都掉电情况下,将迟滞比较器的输出拉为高电平,避免其输出高阻态,保证整形级不会漏电和输出状态不可控

5、最高电压判决电路通过对电源电压比较电路的结果进行逻辑判断得到最高电压值,通过对qab、qbc、qca的输出结果状态共8种可能性进行逻辑判断,当a为最高电平时,qab=1,qca=0,当b为最高电平时,qbc=1,qab=0,当c为最高电平时,qca=1,qbc=0,当a、b、c一样时,qab、qbc、qca会同时为0或者1,因此最高电压判决电路通过对qab和qca反进行与非得到ga0、通过对qbc和qab反进行与非得到gb0,通过对qca和qbc反进行与非得到gc0;ga0、gb0和gc0与非后的信号和ga0经过与门后得到gpa,gb0和‘1’经过与门后得到gpb,gc0和‘1’经过与门后得到gpc,gpa、gpb、gpc为控制a、b、c三路电源的pmos开关管的栅极控制电压原始信号,该判决电路保证任意情况下,只有最高电平的电源对应的栅极电压是低电平,另外两个栅极电压都是高电平,并将结果输出到下一级选择缓冲延迟电路。

6、选择缓冲延迟电路将最高电压判决电路给出的开关选择pmos管的栅极控制电压原始信号gpa、gpb、gpc,经过级联的延迟单元得到gpa、gpb和gpc分别延迟一个td,2个td以至n个td的延迟信号gpa<n:1>,gpb<n:1>,gpc<n:1>输出到下一级开关选择管。

7、开关选择管开主要分为连接电源a、b和c的3套开关管,其中,连接电源a的开关管由2个栅极连接b和c的pmos管串联,和n个栅极连接gpa<n:1>的pmos管并联,连接电源b的开关管由2个栅极连接c和a的pmos管串联,和n个栅极连接gpb<n:1>的pmos管并联,连接电源c的开关管由2个栅极连接a和b的pmos管串联,和n个栅极连接gpc<n:1>的pmos管并联;3套开关管的漏极连接在一起为选择出来的电源vo,并且所有pmos的衬底都连接vo。其中每一路电源上的串联pmos管是为了在上电的时候自动选择出一路最高电压,但是由于pmos管的阈值原因,该最高电平可能会有一个阈值损失,剩余的多个并联的开关管受到延迟电路提供的多级延迟控制,从而达到总开关管缓慢开启,减小切换过冲的目的。

技术特征:

1.一种支持三路输入的电源选择电路,其特征在于,所述电源选择电路由电源电压比较电路、最高电压判决电路、选择缓冲延迟电路和选择开关管组成,其中:

2.根据权利要求1所述的电源选择电路,其特征在于,所述的电源电压比较电路内置三个比较器模块,cmp1、cmp2和cmp3,其中,cmp1的正端连接输入电源a,cmp1的负端连接输入电源b,cmp2的正端连接输入电源b,cmp2的负端连接输入电源c,cmp3的正端连接输入电源c,cmp3的负端连接输入电源a;cmp1的输出qab表征a和b的比较结果,qab=1代表a比b高,qab=0代表a比b低,cmp2的输出qbc表征b和c的比较结果,qbc=1代表b比c高,qbc=0代表b比c低,cmp3的输出qca表征c和a的比较结果,qca=1代表c比a高,qca=0代表c比a低。

3.根据权利要求1所述的电源选择电路,其特征在于,所述的最高电压判决电路通过对qab和qca反进行与非得到ga0、通过对qbc和qab反进行与非得到gb0,通过对qca和qbc反进行与非得到gc0;ga0、gb0和gc0与非后的信号和ga0经过与门后得到gpa,gb0和‘1’经过与门后得到gpb,gc0和‘1’经过与门后得到gpc;gpa代表连接a电源的pmos开关管的栅极原始控制电压,gpb代表连接b电源的pmos开关管的栅极原始控制电压,gpc代表连接c电源的pmos开关管的栅极原始控制电压。

4.根据权利要求1所述的电源选择电路,其特征在于,所述选择缓冲延迟电路通过将gpa、gpb和gpb分别经过级联的延迟单元得到gpa、gpb和gpc分别延迟一个td,2个td以至n个td的延迟信号gpa<n:1>,gpb<n:1>,gpc<n:1>,后级的开关选择管主要分为连接电源a、b和c的3套开关管,其中,连接电源a的开关管由2个栅极连接b和c的pmos管串联,和n个栅极连接gpa<n:1>的pmos管并联,连接电源b的开关管由2个栅极连接c和a的pmos管串联,和n个栅极连接gpb<n:1>的pmos管并联,连接电源c的开关管由2个栅极连接a和b的pmos管串联,和n个栅极连接gpc<n:1>的pmos管并联;3套开关管的漏极连接在一起为选择出来的电源vo,并且所有pmos的衬底都连接vo。

5.根据权利要求2所述的电源选择电路,其特征在于,所述的电源电压比较电路,其内置的比较器模块由迟滞比较器、掉电上拉支路以及整形反相器组成,其中掉电上拉支路为在迟滞比较器的输出和电源电压之间连接2个栅极连接输入信号的pmos管串连组成,用于在该比较器的两个输入都掉电情况下,将迟滞比较器的输出拉为高电平,避免其输出高阻态,保证整形级不会漏电和输出状态不可控。

技术总结

本技术涉及一种应用于多电源芯片中的支持三路输入的电源选择电路结构。对于多电源的芯片内置的电源选择电路来说,其电源电压通常需要从系统中多路电源进行选择,选择原则一般是选择存在且电压最高的电源作为输出,可以用作后级电源模块的控制逻辑电源和功率管的衬底。本发明提出的电源选择电路可以支持三路输入电源,其直接对三路电源输入进行比较判决并控制相应开关管,可以降低对开关管的尺寸要求,保证选择出来的最高电平值误差小,并在其中任意两路电源掉电后仍然能产生可靠的输出电源。

技术研发人员:王小曼

受保护的技术使用者:北京中电华大电子设计有限责任公司

技术研发日:20221024

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!