一种配合XMDA使用的RDMA高速数据传输系统的制作方法

本技术属于数字信号处理领域,涉及一种配合xmda使用的rdma高速数据传输系统。

背景技术:

1、在5g信息量急速增大的环境下,高速数据传输一直是重点关注的。在数据传输系统中,数据传输总线协议一开始遵循isa(工业标准体系结构)总线,由于它只能支持16位i/o(输入/输出)设备,最大的传输速度也只有16mb/s,已经跟不上高速发展的数据传输领域而被淘汰。第二代传输协议是pci(外设部件互连标准)总线,采用并行传输,通用性和开发性更强,但最高速度只有133mb/s。而使用pcie的xdma通信能够增大数据传输的速度。现被广泛用于大型服务器,或者嵌入式系统。

2、虽然使用xdma传输数据的方式虽然可以增大数据传输的速度,但却不能减少cpu的负担。因而,在数据传输过程中如何减少cpu负荷来提高整个数据传输的速度和效率。

技术实现思路

1、有鉴于此,本实用新型的目的在于提供一种配合xmda使用的rdma高速数据传输系统,使在进行xdma高速数据传输时cpu能够空闲出来进行其它线程的运行,从而提高整个系统的运行效率。

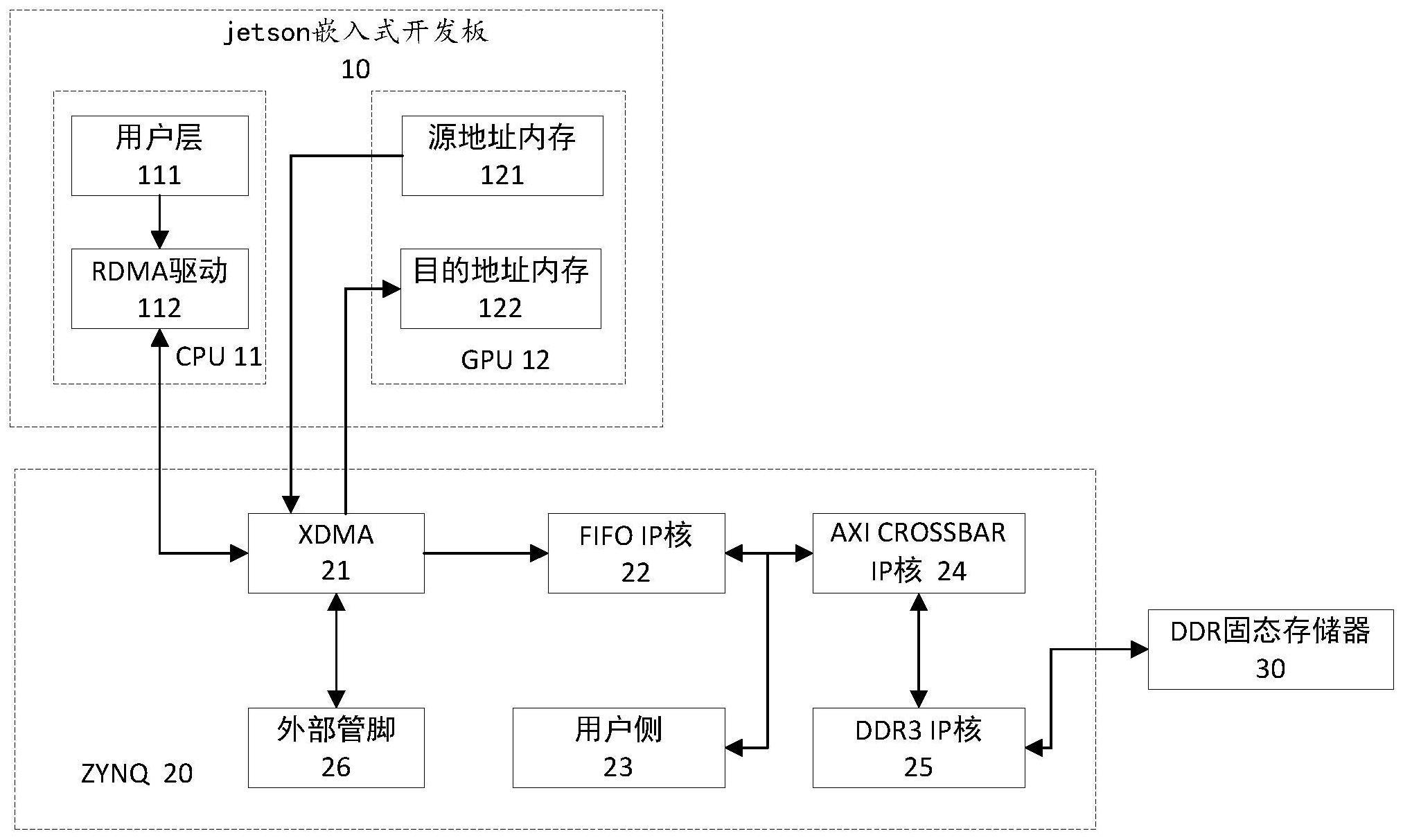

2、为达到上述目的,本实用新型提供一种配合xmda使用的rdma高速数据传输系统,其中,该数据传输系统包括zynq、与所述zynq通过pcie接口连接的jetson嵌入式开发板和与所述zynq通过ddr3接口连接的ddr3固态存储器,所述jetson嵌入式开发板包括cpu和gpu,所述cpu包括用户层和与所述用户层数据交互的rdma内核驱动;其中,所述zynq包括xdma、fifo ip核、用户侧、axi crossbar ip核、ddr3 ip核和外部管脚;所述xdma与所述外部管脚连接;所述fifo ip核与所述xdma通过axi接口连接;所述axi crossbar ip核通过axi接口分别与所述fifo ip核和所述用户侧连接;所述ddr3 ip核与所述axi crossbar ip核通过axi接口连接;所述rdma驱动通过pcie接口直接访问ddr3固态存储器;所述cpu通过pcie总线与所述xdma连接。

3、优选地,所述gpu包括源地址内存区和目的地址内存区,用户层用于控制rdma驱动通过pcie接口直接访问ddr3固态存储器的数据;所述xdma控制所述源地址内存区向ddr3固态存储器写入数据,所述xdma控制所述目的地址内存区从ddr3固态存储器读取数据。

4、优选地,所述fifo ip核为双时钟的fifo ip核,所述fifo ip核的输入端为xdma的时钟和数据位宽,其输出端为ddr3固态存储器的写入时钟和写入数据位宽。

5、本实用新型的有益效果在于:本实用新型所述的技术方案将rdma与xdma技术相结合,能够避免在进行数据传输时cpu的占用,得以让cpu处理其它的线程,使得整体系统性能得以提升。

技术特征:

1.一种配合xmda使用的rdma高速数据传输系统,其特征在于,该数据传输系统包括zynq、与所述zynq通过pcie接口连接的jetson嵌入式开发板和与所述zynq通过ddr3接口连接的ddr3固态存储器,所述jetson嵌入式开发板包括cpu和gpu,所述cpu包括用户层和与所述用户层数据交互的rdma内核驱动;其中,所述zynq包括xdma、fifo ip核、用户侧、axicrossbar ip核、ddr3 ip核和外部管脚;所述xdma与所述外部管脚连接;所述fifo ip核与所述xdma 通过axi接口连接;所述axi crossbar ip核通过axi接口分别与所述fifo ip核和所述用户侧连接;所述ddr3 ip核与所述axi crossbar ip核通过axi接口连接;所述rdma驱动通过pcie接口直接访问ddr3固态存储器;所述cpu通过pcie总线与所述xdma连接。

2.根据权利要求1所述的配合xmda使用的rdma高速数据传输系统,其特征在于,所述gpu包括源地址内存区和目的地址内存区,用户层用于控制rdma驱动通过pcie接口直接访问ddr3固态存储器的数据;所述xdma ip核控制所述源地址内存区向ddr3固态存储器写入数据,所述xdma ip核控制所述目的地址内存区从ddr3固态存储器读取数据。

3.根据权利要求1所述的配合xmda使用的rdma高速数据传输系统,其特征在于,所述fifo ip核为双时钟的fifo ip核,所述fifo ip核的输入端为xdma的时钟和数据位宽,其输出端为ddr3固态存储器的写入时钟和写入数据位宽。

技术总结

本技术涉及一种配合XMDA使用的RDMA高速数据传输系统,该数据传输系统包括ZYNQ、与ZYNQ通过PCIE接口连接的Jetson嵌入式开发板和与ZYNQ通过DDR3接口连接的DDR3固态存储器,Jetson嵌入式开发板包括CPU和GPU,CPU包括用户层和与用户层数据交互的RDMA内核驱动;其中,ZYNQ包括XDMA、FIFO IP核、用户侧、AXI CROSSBAR IP核、DDR3IP核和外部管脚;XDMA与外部管脚连接;FIFO IP核与XDMA通过AXI接口连接;AXI CROSSBAR IP核通过AXI接口分别与FIFO IP核和用户侧连接。

技术研发人员:尤喜成,张邦强,杜念通

受保护的技术使用者:成都橙峰科技有限公司

技术研发日:20221212

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!