具有相关记忆体阵列的神经网路引擎的制作方法

本发明涉及资料处理电路领域,且更具体地涉及乘法器电路。本发明说明了具有记忆体巨集、突触驱动器、突触阵列、记忆体阵列及累加器阵列以有效地计算神经网路操作的神经网络引擎。

背景技术:

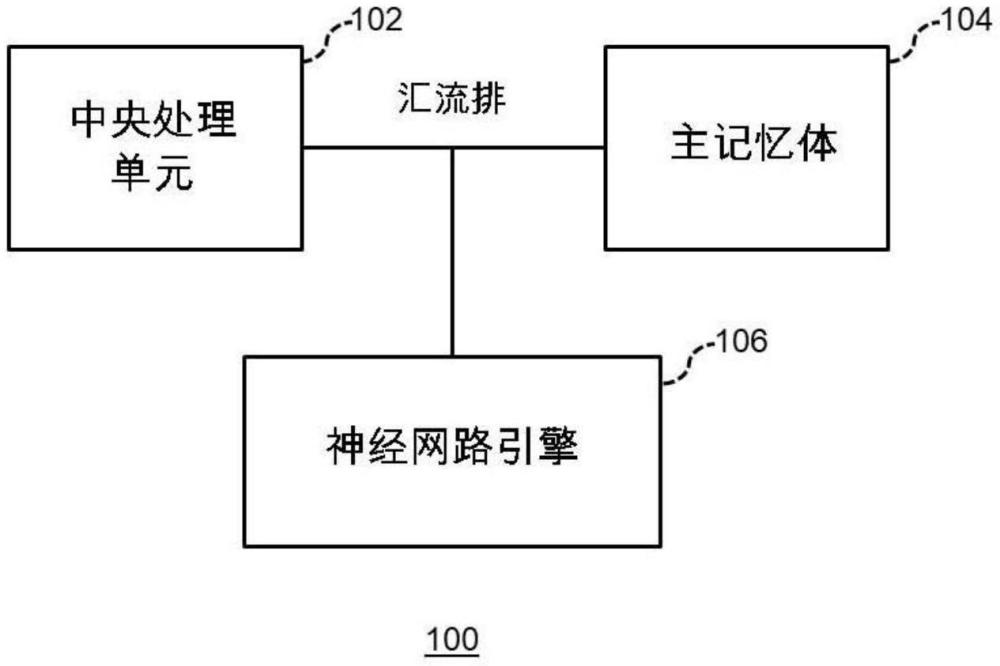

1、图1为通过神经网路引擎执行诸如乘法及累加的神经网络操作的习知处理器100的示意方块图。如图1所示,中央处理单元(central processing unit,cpu)102、主记忆体104及神经网路引擎106为神经网路引擎的关键元件。

2、在此电脑架构中,这些实体通过汇流排交换资料而使得彼此可以通讯。由于中央处理单元102及神经网路引擎106共用储存于主记忆体104中的资料,因此通过中央处理单元102与神经网路引擎106之间的通讯协议,使得主记忆体104为可存取的。

3、举例来说,当中央处理单元102正在存取主记忆体104时,神经网路引擎106根据协议而被限制存取主记忆体104。为了减轻在共用主记忆体104中的资料时的这种通讯负担,快取记忆体可以嵌入至中央处理单元102及神经网路引擎106中。然而,储存在快取记忆体中的信息仍应保持一致。中央处理单元102中的快取信息也应该为神经网路引擎106所知。相似地,神经网路引擎106中的这种信息也应该提供至中央处理单元102,其同样可能导致通讯负担。

4、汇流排及快取记忆体管理上的通讯协议将会降低处理器的性能。因此,建议使用大量的专用于神经网路操作并嵌入至神经网路引擎中的记忆体。如即将所见,本发明在本揭露中将这种记忆体命名为记忆体巨集或记忆体阵列。

5、应注意的是,神经网路计算需要汲取大量的资料,因此如果神经网路引擎中的记忆体巨集或者记忆体阵列的容量不足,可以预期的是资料汇流排上将会有非常大量的通讯负担,且因此需要频繁地存取主记忆体。因此,嵌入至神经网路引擎中的密集记忆体巨集或记忆体阵列为较佳的,而乘法及累加运算则是从神经网路引擎106中有效地计算面积及功率。

技术实现思路

1、有鉴于上述困难及问题而创作出了本发明。本发明的主要目的在于,提供一种包含密集记忆体阵列的神经网路引擎,此密集记忆体阵列被实现为高效率地执行乘法及累加运算。本发明的另一个目的在于,相较于当神经网路引擎需要频繁地存取电脑系统的汇流排上的主记忆体时,提高神经网路操作的性能。

2、在一般态样中,一种用以执行神经网路计算的神经网路引擎包含:第一记忆区块,被配置为提供第一运算元;第二记忆区块,被配置为提供第二运算元;突触阵列,被配置为产生第一及第二运算元的部分乘积,其中突触阵列位于第一及第二记忆区块之外;以及累加器阵列,用于对突触阵列产生的部分乘积执行求和。

3、在另一态样中,突触阵列连接至第一组的多个平行汇流排线路,其中各平行汇流排线路包含多个平行通道,其用于将第一运算元的多个资料位元分别从第一记忆区块平行传输至突触阵列。突触阵列连接至第二组的多个平行汇流排线路,其中各平行汇流排线路包含多个通道,其用于将第二运算元的多个位元分别从第二记忆区块传输至突触阵列

4、在另一态样中,突触阵列包含多个平行突触电路,其用于执行第一及第二运算元的所有位元的多个平行乘法运算。各突触电路连接至第一及第二平行汇流排线路以从第一及第二记忆区块接收第一及第二运算元的位元。各突触电路包含多个平行突触,其中各突触被配置为基于第一及第二运算元的资料位元以同步地产生多个部分乘积。各突触电路连接至两组平行通道,使得第一组平行通道能够从第一记忆区块传输第一运算元的两个互补输入,并且第二组通道能够从第二记忆区块平行传输第二运算元的多个位元。

5、在一般态样中,突触电路进一步包含符号选择单元,其与产生部分乘积的最高有效位元的突触相邻,符号选择单元包含:一对平行输入通道,包含输入线px及输入线nx,其连接至各别的第一组通道;一对平行输出线,包含输出线p及输出线n,其连接至突触阵列中的排列成一列的多个平行突触中的多个;输入端口,其连接至第二组通道中的对应的一个,且用于从第二记忆区块接收第二运算元的一个符号输入位元;以及多个开关,其可响应于第二运算元的符号输入位元值而操作。

6、在另一态样中,第一组的多个开关被配置为当输入端口接收第二运算元的1的符号位元值时,连接输入线px至输出线n以及输入线nx至输出线p。第二组的多个开关被配置为当输入端口从第二运算元接收0的符号位元值时,连接输入线px至输出线p以及输入线nx至输出线n。输入线px、输入线nx的通道上的位元值包含互补值(1,0)或(0,1)又或者全零(0,0)。

7、在一般态样中,突触包含四个金属氧化物半导体(metal-oxide-semiconductor,mos)转译器,其中各电晶体包含四个金属氧化物半导体电晶体以执行第一及第二运算元的1位元乘法运算。四个金属氧化物半导体电晶体中的第一个及第二个为串联连接,且具有连接至各别的该输出线p及该输出线n的闸,并且分别连接至一对主及互补位元线。第一电晶体的一端耦接至主位元线bl,并且第二电晶体的一端耦接至互补位元线blb。第一电晶体连接至主位元线bl以在运算元a及b具有相同的符号值时,输出乘法运算的各别的1位元部分乘积;并且其中第二电晶体连接至互补位元线blb以在运算元a及b具有不同的符号值时,输出乘法运算的各别的1位元部分乘积。四个金属氧化物半导体电晶体中的第三个及第四个为串联连接,且其中第三电晶体具有连接至与第二记忆区块连接的第二组通道中的一个的闸极端子,并且第四电晶体具有连接至参考信号源vref的闸,其中参考信号源vref为具有vdd及vss范围的类比电压源。

8、在一般态样中,平行突触包含:第一及闸,其具有连接至p输出线p的第一输入、连接至第二组通道中的一个的第二输入以及连接至一对位元线中的主位元线的输出;以及第二及闸,其具有连接至输出线(n)的第一输入、连接至第一及闸所连接的通道的第二输入以及连接至一对位元线中的互补位元线的输出。

9、在一般态样中,神经网路引擎进一步包含:突触驱动器,被配置以连接内部记忆体至突触阵列,其中突触驱动器被配置为转换串流原始输入资料(streaming raw inputdata)为两对或多对输入资料,以平行执行多个1位元乘法运算。突触驱动器被配置为产生对应于原始资料的1位元的一对位元,其中原始资料响应于其接收的符号位元值。

技术特征:

1.一种神经网路引擎,用于执行计算,其包含:

2.根据权利要求1所述的神经网路引擎,其中该突触阵列连接至第一组的多个平行汇流排线路,其中各该平行汇流排线路包含多个平行通道,其用于将该第一运算元的多个资料位元分别从该第一记忆区块平行传输至该突触阵列。

3.根据权利要求2所述的神经网路引擎,其中该突触阵列连接至第二组的该多个平行汇流排线路,其中各该平行汇流排线路包含多个通道,其用于将该第二运算元的多个位元分别从该第二记忆区块传输至该突触阵列。

4.根据权利要求3所述的神经网路引擎,其中该突触阵列包含多个平行突触电路,其用于执行该第一运算元及该第二运算元的所有位元的多个平行乘法运算。

5.根据权利要求4所述的神经网路引擎,其中各该平行突触电路连接至第一组及第二组的该平行汇流排线路以从该第一记忆区块及该第二记忆区块接收该第一运算元及该第二运算元的位元。

6.根据权利要求5所述的神经网路引擎,其中各该平行突触电路包含多个平行突触,其中各该平行突触被配置为基于该第一运算元及该第二运算元的该资料位元以产生多个部分乘积。

7.根据权利要求6所述的神经网路引擎,其中各该平行突触电路连接至两组平行通道,使得第一组平行通道能够从该第一记忆区块传输该第一运算元的两个互补输入,并且第二组通道能够从该第二记忆区块平行传输该第二运算元的多个位元。

8.根据权利要求7所述的神经网路引擎,其中该平行突触电路进一步包含一符号选择单元,其与产生部分乘积的最高有效位元的突触相邻,该符号选择单元包含:

9.根据权利要求8所述的神经网路引擎,其中第一组的该多个开关被配置为当该输入端口接收该第二运算元的1的符号位元值时,连接该输入线(px)至该输出线(n)以及该输入线(nx)至该输出线(p)。

10.根据权利要求9所述的神经网路引擎,其中第二组的该多个开关被配置为当该输入端口从该第二运算元接收0的符号位元值时,连接该输入线(px)至该输出线(p)以及该输入线(nx)至该输出线(n)。

11.根据权利要求10所述的神经网路引擎,其中该输入线(px)、该输入线(nx)的通道上的位元值包含互补值(1,0)或(0,1)又或者全零(0,0)。

12.根据权利要求11所述的神经网路引擎,其中该平行突触包含四个金属氧化物半导体翻译器,其中各电晶体包含四个金属氧化物半导体电晶体以执行该第一运算元及该第二运算元的1位元乘法运算。

13.根据权利要求12所述的神经网路引擎,其中四个该金属氧化物半导体电晶体中的一第一电晶体及一第二电晶体为串联连接,且具有连接至各别的该输出线(p)及该输出线(n)的闸,并且分别连接至一对主及互补位元线。

14.根据权利要求13所述的神经网路引擎,其中该第一电晶体的一端耦接至一主位元线(bl),并且该第二电晶体的一端耦接至一互补位元线(blb)。

15.根据权利要求14所述的神经网路引擎,其中该第一电晶体连接至该主位元线(bl)以在该第一运算元及该第二运算元具有相同的符号值时,输出乘法运算的各别的1位元部分乘积;并且其中该第二电晶体连接至该互补位元线(blb)以在该第一运算元及该第二运算元具有不同的符号值时,输出乘法运算的各别的1位元部分乘积。

16.根据权利要求15所述的神经网路引擎,其中四个该金属氧化物半导体电晶体中的一第三电晶体及一第四电晶体为串联连接,且其中该第三电晶体具有连接至与该第二记忆区块连接的第二组通道中的一个的闸极端子,并且该第四电晶体具有连接至一参考信号源(vref)的闸,其中该参考信号源(vref)为具有vdd及vss范围的类比电压源。

17.根据权利要求11所述的神经网路引擎,其中该平行突触包含:

18.根据权利要求1所述的神经网路引擎,其进一步包含一突触驱动器,被配置为连接一内部记忆体至该突触阵列,其中该突触驱动器被配置为转换一串流原始输入资料为两对或多对输入资料,以平行执行多个1位元乘法运算。

19.根据权利要求11所述的神经网路引擎,其中一突触驱动器被配置为产生对应于一原始资料的1位元的一对位元,其中该原始资料响应于其接收的符号位元值。

技术总结

本发明为一种神经网路引擎,其配置为执行神经网路计算。神经网路引擎包含:第一记忆区块,其配置为提供第一运算元;第二记忆区块,其配置为提供第二运算元;突触阵列,其配置为产生第一及第二运算元的部分乘积,其中突触阵列位于第一及第二记忆区块之外;以及,累加器阵列,其对突触阵列产生的部分乘积执行求和。

技术研发人员:宋承桓,金时焕

受保护的技术使用者:安纳富来希股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!