企业主机存储器缓冲区的制作方法

本公开的实施方案总体涉及数据存储设备,诸如固态驱动器(ssd),并且更具体地,涉及经由数据存储设备与主机设备之间的接口使用外部存储设备。相关领域的描述企业ssd具有特定要求,以便集成到数据中心环境中。例如,要求可以包括用于读取操作的可预测性和短延迟,并且维持来自ssd的逻辑地址范围的任何部分的读取的相同的服务质量(qos)水平。由于所述要求,逻辑块地址(lba)到物理块地址(pba)(l2p)表可以存储在dram中,其中dram容量可以呈1:1000比率(例如,2tb ssd=2gb dram,针对l2p表高速缓存)。在一些示例中,由于增加的间接,以性能为代价,比率可以更大(例如,1:2000)。因此,随着ssd容量增加,ssd中包含的dram的容量也增加,这可能增加ssd的成本。用于企业存储系统的数据存储设备可以基于每天驱动写入(dwpd)数目来评定驱动器的寿命。客户可以选择超过数据存储设备的dwpd,以更快地磨损设备为代价。因此,数据存储设备的成本转换为写入循环(例如,程序擦除循环(pec))数目。因为dram不以与非易失性存储器(例如nand存储器)相同的速度磨损,大容量数据存储设备可以具有不均匀的存储器使用,使得非易失性存储器可以在需要使dram退役之前退役。因此,本领域需要用于更好地集成到数据中心环境中的改进的存储系统。

背景技术:

技术实现思路

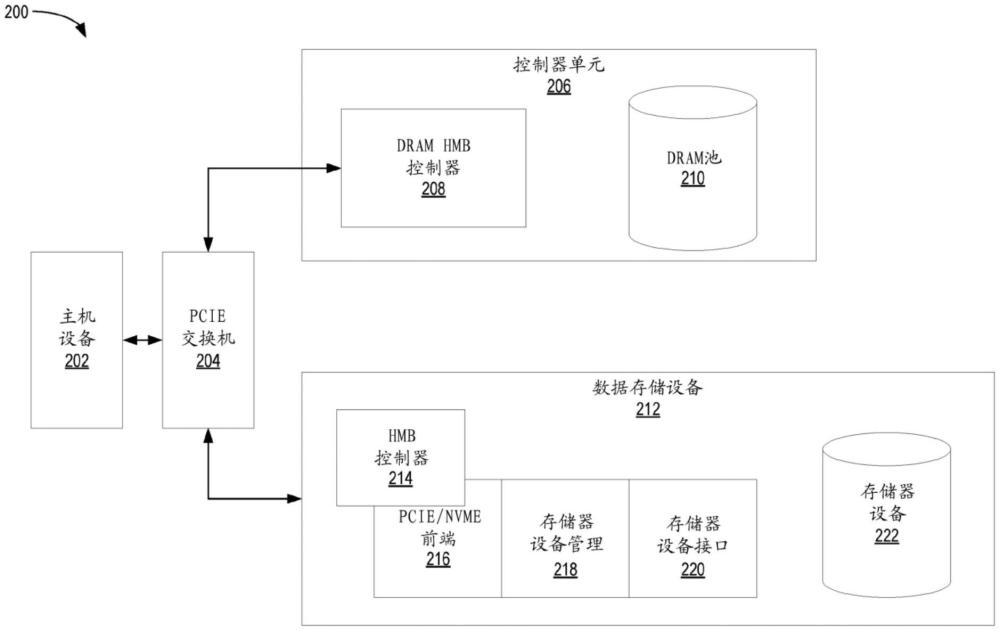

1、本公开总体涉及数据存储设备,诸如固态驱动器(ssd),并且更具体地,涉及经由数据存储设备与主机设备之间的接口使用外部存储设备。本发明涉及存储系统,该存储系统包括一个或多个数据存储设备、耦接到一个或多个数据存储设备的pcie交换机以及耦接到pcie交换机的控制器单元。控制器单元包括动态随机存取存储器(dram)主机存储器缓冲区(hmb)控制器和dram池或控制器存储器缓冲区(cmb)控制器、根复合体/端口和dram池。该dram池包括一个或多个dram设备。该一个或多个数据存储设备被配置成与控制器单元交互并将数据存储到控制器单元的dram池的dram。

2、在一个实施方案中,存储系统包括一个或多个数据存储设备、耦接到一个或多个数据存储设备的pcie交换机以及耦接到pcie交换机的控制器单元。控制器单元包括动态随机存取存储器(dram)主机存储器缓冲区(hmb)控制器和dram池。该dram池包括一个或多个dram设备。

3、在另一实施方案中,存储系统包括第一数据存储设备、第二数据存储设备、耦接到第一数据存储设备和第二数据存储设备的pcie交换机、以及耦接到第一数据存储设备和第二数据存储设备的控制器单元。控制器单元包括动态随机存取存储器(dram)主机存储器缓冲区(hmb)控制器和dram池。该dram池包括一个或多个dram设备。

4、在另一实施方案中,存储系统包括第一数据存储设备,该第一数据存储设备包括第一存储器装置;第二数据存储设备,该第二数据存储设备包括第二存储器装置;耦接到第一数据存储设备和第二数据存储设备的pcie交换机;和控制器单元,该控制器单元耦接到第一数据存储设备和第二数据存储设备。控制器单元包括控制器存储器缓冲区(cmb)控制器和根复合体/端口。

技术特征:

1.一种存储系统,所述存储系统包括:

2.根据权利要求1所述的存储系统,其中所述pcie交换机直接耦接到所述dram hmb控制器。

3.根据权利要求1所述的存储系统,其中所述一个或多个数据存储设备中的每个数据存储设备包括:

4.根据权利要求1所述的存储系统,其中所述控制器单元充当所述一个或多个数据存储设备的根复合体。

5.根据权利要求1所述的存储系统,其中所述一个或多个数据存储设备不同于所述控制器单元。

6.根据权利要求1所述的存储系统,其中所述控制器单元作为所述一个或多个数据存储设备的对等pcie设备出现。

7.根据权利要求1所述的存储系统,其中所述dram池由所述一个或多个数据存储设备共享。

8.根据权利要求1所述的存储系统,其中所述一个或多个数据存储设备是两个或更多个数据存储设备。

9.根据权利要求1所述的存储系统,其中所述一个或多个数据存储设备中的每个数据存储设备包括第一端口和第二端口,并且其中所述第一端口耦接到所述pcie交换机。

10.一种存储系统,所述存储系统包括:

11.根据权利要求10所述的存储系统,其中所述第一数据存储设备和所述第二数据存储设备各自具有第一端口和第二端口,并且其中所述第一端口耦接到所述pcie交换机。

12.根据权利要求11所述的存储系统,其中所述第二端口耦接到所述控制器单元。

13.根据权利要求12所述的存储系统,其中所述第二端口耦接到hmb控制器。

14.根据权利要求13所述的存储系统,其中所述hmb控制器设置在所述第一数据存储设备和所述第二数据存储设备中。

15.根据权利要求12所述的存储系统,其中所述第二端口耦接到所述dram hmb控制器。

16.根据权利要求10所述的存储系统,其中所述控制器单元被配置成在检测到所述控制器单元的电力故障事件时,将所述dram池的数据推送到下列中的任一者:所述第一数据存储设备、所述第二数据存储设备或所述第一数据存储设备和所述数据存储设备两者。

17.一种存储系统,所述存储系统包括:

18.根据权利要求17所述的存储系统,其中所述第一数据存储设备、所述第二数据存储设备和所述控制器单元各自包括:

19.根据权利要求17所述的存储系统,其中所述第一数据存储设备和所述第二数据存储设备各自包括第一端口和第二端口,其中所述第一端口耦接到所述pcie交换机,并且其中所述第二端口耦接到所述根复合体/端口。

20.根据权利要求17所述的存储系统,其中所述cmb控制器耦接到dram池。

技术总结

存储系统包括一个或多个数据存储设备、耦接到一个或多个数据存储设备的PCIe交换机以及耦接到PCIe交换机的控制器单元。控制器单元包括动态随机存取存储器(DRAM)主机存储器缓冲区(HMB)控制器和DRAM池或控制器存储器缓冲区(CMB)控制器、根复合体/端口和DRAM池。该DRAM池包括一个或多个DRAM设备。该一个或多个数据存储设备被配置成与控制器单元交互并将数据存储到控制器单元的DRAM池的DRAM。

技术研发人员:J·G·哈恩,A·H·霍德斯,S·贝尼斯蒂,M·詹姆斯

受保护的技术使用者:西部数据技术公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!