用于使用具有减少的引脚选项的串行外围设备接口(SPI)的芯片操作的系统和方法与流程

背景技术:

技术实现思路

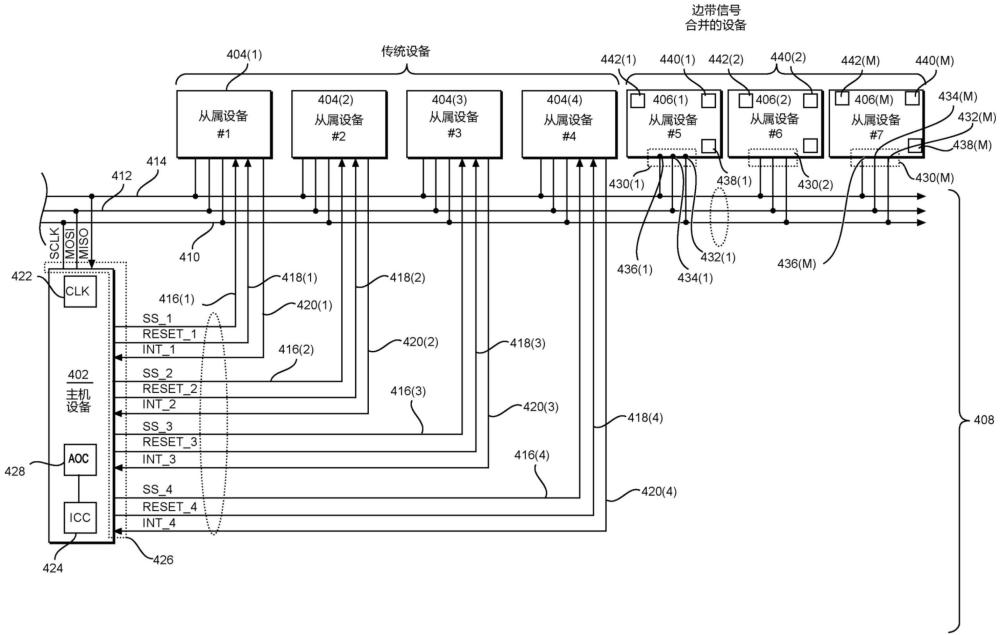

1、具体实施方式中公开的各方面包括用于使用具有减少的引脚选项的串行外围设备接口(spi)的芯片操作的系统和方法。具体地,示例性方面考虑消除用于主机(也称为主设备)到设备(也称为从设备)通信链路的芯片选择引脚、中断引脚和/或复位引脚,同时在需要时保留传统设备的向后兼容的可能性。该通信链路可包括时钟线、主机到设备线以及设备到主机线。该主机可使用该时钟线和该主机到设备线上的特定信号序列来提供开始和停止序列命令、中断、或复位命令。通过将这些命令合并到该时钟线和该主机到设备线上,可减少主机电路和从电路的部分的引脚计数。同样地,可能需要更少(或至少可能更短)的导电迹线来将该主机互连到该设备。此类改变可节省成本、使布局设计更容易和/或节省计算设备内的空间。

2、就这一点而言,在一方面,公开了一种集成电路(ic)。该ic包括总线接口。该总线接口包括被配置为耦合到相关联总线上的时钟线的时钟引脚。该总线接口还包括被配置为耦合到该相关联总线的主机到从属(host-to-subordinate)引脚。该总线接口还包括被配置为耦合到该相关联总线的从属到主机引脚。该ic还包括控制电路。该控制电路被配置为改变该主机到从属引脚的逻辑状态,随后激活该时钟线,并且通过该主机到从属引脚随后发送地址和命令。

3、在另一方面,公开了一种ic。该ic包括总线接口。该总线接口包括被配置为耦合到相关联总线上的时钟线的时钟引脚。该总线接口还包括被配置为耦合到该相关联总线的主机到从属引脚。该总线接口还包括被配置为耦合到该相关联总线的从属到主机引脚。该ic还包括控制电路。该控制电路被配置为将该主机到从属引脚上的状态从逻辑空闲状态改变为断言状态。当保持该主机到从属引脚处于该断言状态时,该控制电路还被配置为切换该时钟引脚预定次数以发信号通知复位。

4、在另一方面,公开了一种ic。该ic包括总线接口。该总线接口包括被配置为耦合到相关联总线上的时钟线的时钟引脚。该总线接口还包括被配置为耦合到该相关联总线的主机到从属引脚。该总线接口还包括被配置为耦合到该相关联总线的从属到主机引脚。该ic还包括控制电路。当处于逻辑空闲状态时,该控制电路被配置为检测由从属芯片引起的该从属到主机引脚上的状态变化。响应于该从属到主机引脚上的该状态变化,该控制电路被配置为启动该时钟引脚上的时钟信号。

5、在另一方面,公开了一种系统。该系统包括从属芯片。该系统还包括耦合到该从属芯片的总线。该系统还包括主机芯片。该主机芯片包括总线接口。该总线接口包括被配置为耦合到该总线上的时钟线的时钟引脚。该总线接口还包括被配置为耦合到该总线的主机到从属引脚。该总线接口还包括被配置为耦合到该总线的从属到主机引脚。该主机芯片还包括控制电路。该控制电路被配置为改变该主机到从属引脚的逻辑状态,随后激活该时钟线,并且通过该主机到从属引脚随后发送地址和命令以向该从属芯片指示芯片选择。该控制电路还被配置为将该主机到从属引脚上的状态从逻辑空闲状态改变为断言状态。当保持该主机到从属引脚处于该断言状态时,该控制电路还被配置为切换该时钟引脚预定次数以向该从属芯片发信号通知复位。当处于该逻辑空闲状态时,该控制电路被配置为检测由该从属芯片引起的该从属到主机引脚上的状态变化。响应于该从属到主机引脚上的该状态变化,该控制电路被配置为启动该时钟引脚上的时钟信号。

技术特征:

1.一种集成电路(ic),包括:

2.根据权利要求1所述的ic,还包括传统从选择引脚。

3.根据权利要求2所述的ic,其中所述控制电路还被配置为将所述传统从选择引脚保持在逻辑空闲状态,同时改变所述主机到从属引脚的所述逻辑状态。

4.根据权利要求1所述的ic,其中所述控制电路还被配置为:在发送所述地址和命令之后,通过所述从属到主机引脚从从属芯片接收数据。

5.根据权利要求1所述的ic,其中所述总线接口包括串行外围设备接口(spi)总线接口。

6.根据权利要求1所述的ic,其中所述控制电路被配置为通过所述主机到从属引脚向多个从属芯片发送命令。

7.根据权利要求1所述的ic,其中所述控制电路被配置为使用所述主机到从属引脚和所述时钟引脚来向从属芯片发送复位命令。

8.一种集成电路(ic),包括:

9.根据权利要求8所述的ic,还包括传统复位引脚。

10.根据权利要求9所述的ic,其中所述控制电路还被配置为激活所述传统复位引脚,同时在所述时钟引脚上发信号通知所述复位。

11.根据权利要求8所述的ic,其中所述控制电路被配置为使用所述时钟引脚上的第一命令向单个从属芯片发信号通知软复位。

12.根据权利要求11所述的ic,其中所述控制电路被配置为使用所述时钟引脚上的第二命令向多个从属芯片发信号通知全局软复位。

13.根据权利要求11所述的ic,其中所述控制电路被配置为使用所述时钟引脚上的第三命令向单个从属芯片发信号通知硬复位。

14.根据权利要求13所述的ic,其中所述控制电路被配置为使用所述时钟引脚上的第四命令向多个从属芯片发信号通知全局硬复位。

15.根据权利要求8所述的ic,其中所述总线接口包括串行外围设备接口(spi)总线接口。

16.一种集成电路(ic),包括:

17.根据权利要求16所述的ic,其中所述控制电路还被配置为:在检测到所述状态变化之后,将所述从属到主机引脚驱动到逻辑相反状态。

18.根据权利要求16所述的ic,其中所述控制电路还被配置为在所述主机到从属引脚上发送获取代码。

19.根据权利要求18所述的ic,其中所述获取代码包括标识符请求。

20.根据权利要求19所述的ic,其中所述控制电路还被配置为响应于所述获取代码从所述从属芯片接收从属标识符。

21.根据权利要求18所述的ic,其中所述获取代码包括具有中断澄清请求的标识符。

22.根据权利要求21所述的ic,其中所述控制电路还被配置为响应于所述获取代码而接收从属标识符和中断标识代码。

23.根据权利要求18所述的ic,其中所述获取代码包括标识符和中断命令请求。

24.根据权利要求23所述的ic,其中所述控制电路还被配置为响应于所述获取代码而接收从属标识符、中断标识代码和补救命令。

25.一种系统,包括:

技术总结

用于使用具有减少的引脚选项的串行外围设备接口(SPI)的芯片操作的系统和方法,这些系统和方法考虑消除用于主机(也称为主设备)到设备(也称为从设备)通信链路的芯片选择引脚、中断引脚和/或复位引脚,同时在需要时保留传统设备的向后兼容的可能性。该通信链路可包括时钟线、主机到设备线以及设备到主机线。该主机可使用时钟和主机到设备线上的特定信号序列来提供开始和停止序列命令、中断、或复位命令。通过将这些命令合并到该时钟和主机到设备线上,可减少主机电路和从电路的部分的引脚计数。同样地,可能需要更少(或至少可能更短)的导电迹线来将该主机互连到该设备。此类改变可节省成本、使布局设计更容易和/或节省计算设备内的空间。

技术研发人员:L·J·米什拉,R·皮特戈伊-阿伦,R·D·维特菲尔德

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!