一种存内计算单元及阵列的制作方法

本发明涉及集成电路设计领域,特别是涉及一种存内计算单元及阵列。

背景技术:

1、卷积神经网络(cnn)在目标检测、图像识别等领域的快速发展,需要更多的考虑到功耗以及能效问题。而受限于传统冯·诺伊曼架构中存在运算器和存储器分离的缺陷,无法实现高速低功耗的要求,因此亟需一种存算一体单元来实现低功耗计算。

技术实现思路

1、本发明所要解决的技术问题是提供一种存内计算单元及阵列,能够进行高速低功耗的卷积计算。

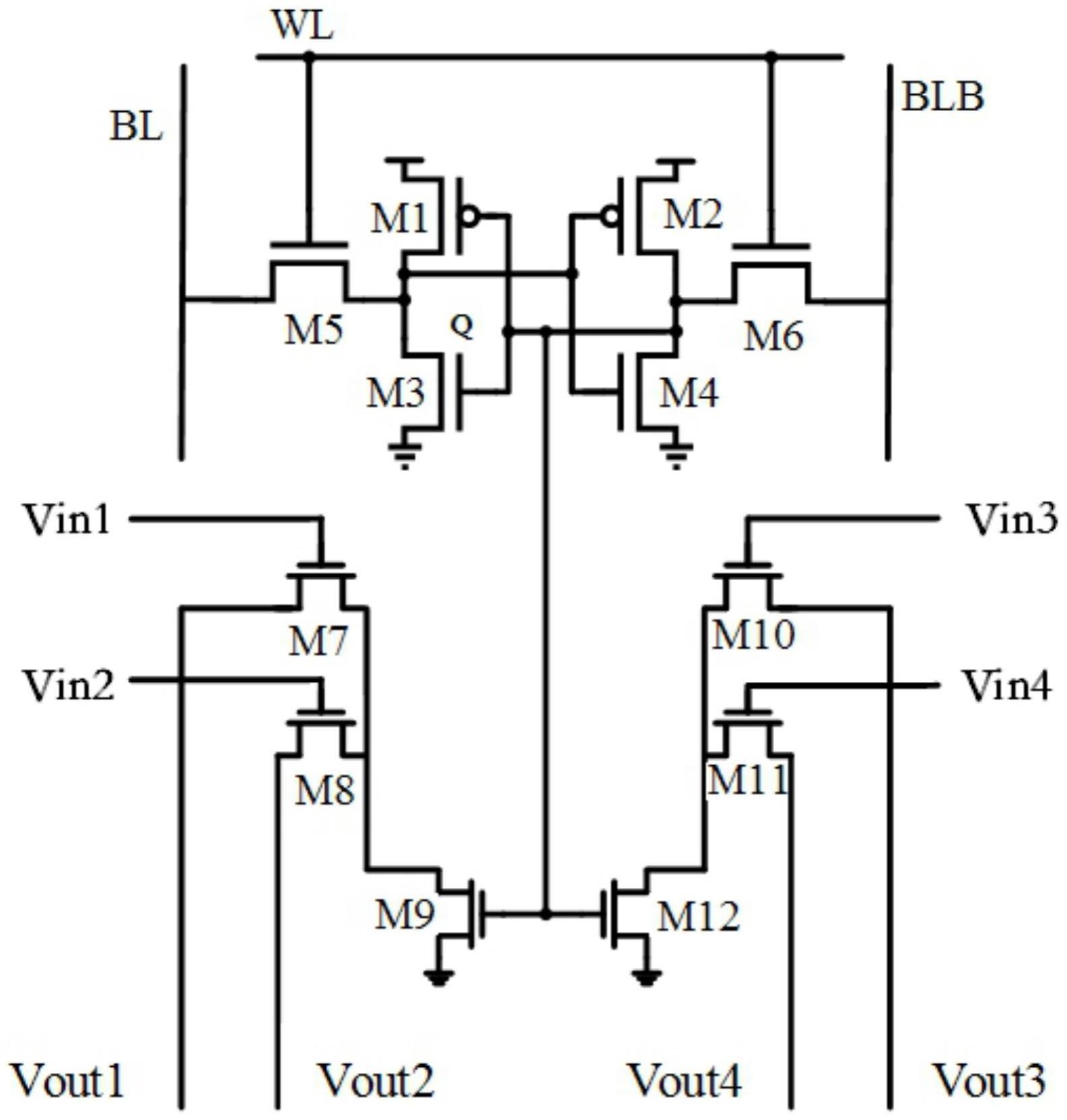

2、本发明解决其技术问题所采用的技术方案是:提供一种存内计算单元,包括单端口sram和计算部分,所述单端口sram用于存储权重,所述计算部分用于进行乘法运算,包括第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管和第十二mos管;所述单端口sram的存储节点分别与所述第九mos管的栅极和第十二mos管的栅极相连;所述第九mos管的漏极分别与所述第七mos管的源极和第八mos管的源极相连,所述第十二mos管的漏极分别与所述第十mos管的源极和第十一mos管的源极相连;所述第九mos管的源极和第十二mos管的源极均接地;所述第七mos管的栅极与第一输入端相连,漏极与第一输出端相连;所述第八mos管的栅极与第二输入端相连,漏极与第二输出端相连;所述第十mos管的栅极与第三输入端相连,漏极与第三输出端相连;所述第十一mos管的栅极与第四输入端相连,漏极与第四输出端相连。

3、所述单端口sram为6tsram。

4、所述第一输入端、第二输入端、第三输入端和第四输入端分别对应4bit输入信号的最低位、次低位、次高位和最高位。

5、所述第一输入端和第二输入端在输入信号时两者之间存在延时,所述第三输入端和第四输入端在输入信号时两者之间存在延时。

6、本发明解决其技术问题所采用的技术方案是:一种存内计算阵列,包括4×n2个上述的存内计算单元,所述存内计算单元按照n2行4列排列,每一行中的所有的存内计算单元的第一输入端连接在一起,第二输入端连接在一起,第三输入端连接在一起,第四输入端连接在一起;每一列中所有的存内计算单元的第一输出端连接在一起,第二输出端连接在一起,第三输出端连接在一起,第四输出端连接在一起;连接在一起的第一输出端、第二输出端、第三输出端和第四输出端分别与adc模块的输入端相连,所述adc模块的输出端与加法器模块的输入端相连。

7、所述的存内计算阵列中每一行用来存储1个4bit的权重,每一行中的4个存内计算单元依次用来存储所述4bit的权重的最低位、次低位、次高位和最高位。

8、所述的存内计算阵列中每一列的存内计算单元存储的权重相同。

9、有益效果

10、由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明通过6个mos管在存储单元中加入了计算单元,克服了传统冯·诺伊曼架构中存在运算器和存储器分离的缺陷,实现了高速低功耗的卷积计算。

技术特征:

1.一种存内计算单元,其特征在于,包括单端口sram和计算部分,所述单端口sram用于存储权重,所述计算部分用于进行乘法运算,包括第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管和第十二mos管;所述单端口sram的存储节点分别与所述第九mos管的栅极和第十二mos管的栅极相连;所述第九mos管的漏极分别与所述第七mos管的源极和第八mos管的源极相连,所述第十二mos管的漏极分别与所述第十mos管的源极和第十一mos管的源极相连;所述第九mos管的源极和第十二mos管的源极均接地;所述第七mos管的栅极与第一输入端相连,漏极与第一输出端相连;所述第八mos管的栅极与第二输入端相连,漏极与第二输出端相连;所述第十mos管的栅极与第三输入端相连,漏极与第三输出端相连;所述第十一mos管的栅极与第四输入端相连,漏极与第四输出端相连。

2.根据权利要求1所述的存内计算单元,其特征在于,所述单端口sram为6t sram。

3.根据权利要求1所述的存内计算单元,其特征在于,所述第一输入端、第二输入端、第三输入端和第四输入端分别对应4bit输入信号的最低位、次低位、次高位和最高位。

4.根据权利要求3所述的存内计算单元,其特征在于,所述第一输入端和第二输入端在输入信号时两者之间存在延时,所述第三输入端和第四输入端在输入信号时两者之间存在延时。

5.一种存内计算阵列,其特征在于,包括4×n2个如权利要求1-4中任一所述的存内计算单元,所述存内计算单元按照n2行4列排列,每一行中的所有的存内计算单元的第一输入端连接在一起,第二输入端连接在一起,第三输入端连接在一起,第四输入端连接在一起;每一列中所有的存内计算单元的第一输出端连接在一起,第二输出端连接在一起,第三输出端连接在一起,第四输出端连接在一起;连接在一起的第一输出端、第二输出端、第三输出端和第四输出端分别与adc模块的输入端相连,所述adc模块的输出端与加法器模块的输入端相连。

6.根据权利要求5所述的存内计算阵列,其特征在于,每一行用来存储1个4bit的权重,每一行中的4个存内计算单元依次用来存储所述4bit的权重的最低位、次低位、次高位和最高位。

7.根据权利要求6所述的存内计算阵列,其特征在于,每一列的存内计算单元存储的权重相同。

技术总结

本发明涉及一种存内计算单元和阵列,其中,存内单元包括单端口SRAM和计算部分,单端口SRAM用于存储权重,计算部分用于进行乘法运算,包括第七MOS管、第八MOS管、第九MOS管、第十MOS管、第十一MOS管和第十二MOS管;单端口SRAM的存储节点分别与第九MOS管的栅极和第十二MOS管的栅极相连;第九MOS管的漏极分别与第七MOS管的源极和第八MOS管的源极相连,第十二MOS管的漏极分别与第十MOS管的源极和第十一MOS管的源极相连;第九MOS管的源极和第十二MOS管的源极均接地;第七MOS管、第八MOS管、第十MOS管和第十一MOS管的栅极分别与第一输入端、第二输入端、第三输入端和第四输入端相连,漏极分别与第一输出端、第二输出端、第三输出端和第四输出端相连。本发明能够进行高速低功耗的卷积计算。

技术研发人员:刘建文,赵信,方华,张立,童仙雨

受保护的技术使用者:上海高性能集成电路设计中心

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!