一种基于ReRAM的神经网络权重映射方法与流程

本发明涉及神经网络加速器领域,尤其涉及一种基于reram神经网络加速器的权重映射方法。

背景技术:

1、随着数据规模的飞速增长,存算密集型的神经网络应用对硬件算力和数据存储容量的需求也相应增大。为了突破传统冯诺依曼架构中计算存储分离造成的访存带宽瓶颈,越来越多的研究开始关注高密度的存算一体计算架构,以期通过将计算和存储紧密耦合,减少由于数据在存储部件和计算部件间频繁搬运而额外增加的访存能耗和带宽需求,从而最大化硬件架构的能效比。

2、新兴的非易失性存储器——阻变存储器(reram)利用电导值进行存储,通过欧姆定律组织乘法累加计算,形成了传统存储器不具备的原位计算功能。传统的加速对基于冯·诺伊曼体系结构,需要同时搬运weight与feature才能进行计算。而基于reram的神经网络加速器将输入向量转变成电压施加在rram的字线(word-line)上,再将另一个权重输入预先映射为reram各个单元的电导,利用位线(bit-line)上的累积电流表征为两个向量的数量积,实现原位存内处理,大大减缓数据带宽压力以提高性能。

3、现阶段,主流存算一体加速器常采用层次化的拓扑结构,电路被自顶而下划分成不同规模的功能模块。架构中最小粒度计算模块为reram交叉阵列与算术逻辑单元,基本单元组合形成上层运算模块,上层模块间仍可以相互组合,以此类推直至架构顶层。根据模块的调度和驱动方式,现有的加速器体系可以分成两类:数据流驱动型和指令流驱动型。

4、数据流驱动型结构指在计算执行过程中,各功能模块的数据存取和交互均由状态机控制完成,过程无指令干涉。神经网络推理中,一旦网络的结构和权重确定,整个运算中数据的规模和执行模式也随之确定。数据流驱动型存算一体结构正是瞄准这一特性,在执行前将网络层的结构、连接关系以及权重值映射到对应的功能阵列上,通过执行时输入输出控制,即可实现网络推理过程。此类结构中,典型的加速器有isaac,prime等。

5、在专利cn202110406885.5中公开了基于阻变忆阻器的精简指令集存算一体神经网络协处理器,通过reram阵列,在存储器中实现快速而准确的卷积运算,用于加速神经网络中存在的大量乘累加计算,减少了数据搬运带来了功耗和时间开销,节省了硬件消耗。在专利cn202111061410.3中公开了一种基于数据稀疏性的超额行激活存算一体加速器设计,构建基于行激活数据的预测机制,建模外围电路器件限制与计算并行度,以解决所述外围电路与所述计算并行度的匹配问题;构建行激活超额订阅机制,自适应地调整所述计算并行度和资源使用,以解决稀疏数据下计算阵列和所述外围电路利用率低,资源冗余的问题;针对神经网络数据稀疏性的特点,重新规划控制流和数据流,以解决利用数据稀疏性而引入的复杂电路设计的问题。但都未考虑过其采用reram计算阵列中,权重映射时的优化问题。

6、而目前业界主流的reram权重映射模式也存在问题:1.权重映射模式较固定,映射算法普遍基于权重输入通道和输出通道的展开模式,灵活性差;2.映射算法的内在要求导致硬件结构复杂,reram寻址过程需要遍历卷积计算的各维度。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提出一种基于reram神经网络加速器的权重映射方法。

2、本发明的目的是通过以下技术方案来实现的:

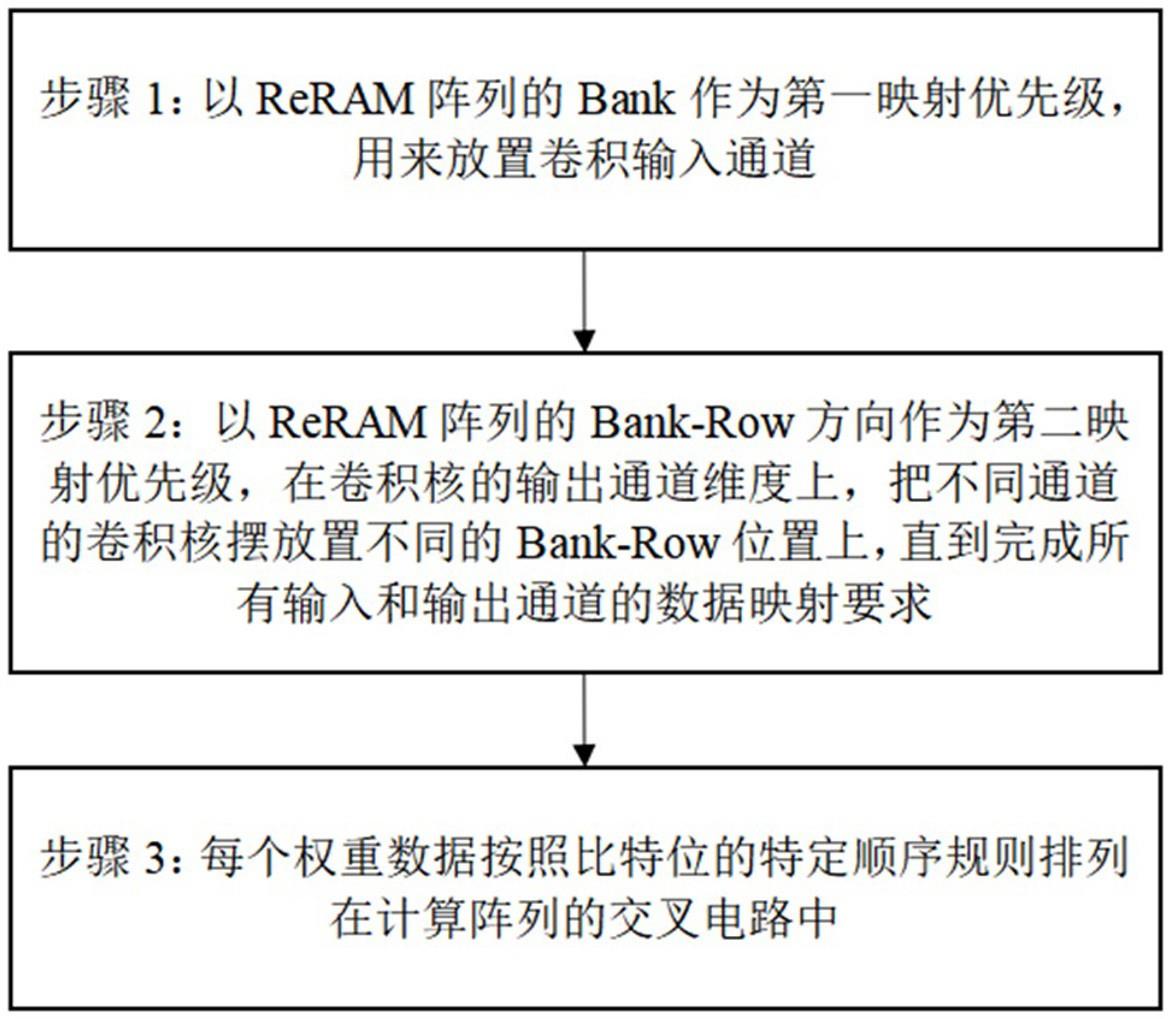

3、一种基于reram神经网络加速器的权重映射方法,包括以下步骤:

4、步骤1:以reram阵列的bank作为第一映射优先级,用来放置卷积输入通道;

5、步骤2:以reram阵列的bank-row方向作为第二映射优先级,在卷积核的输出通道维度上,把不同通道的卷积核摆放置不同的bank-row位置上,直到完成所有输入和输出通道的数据映射要求;

6、步骤3:每个权重数据按照比特位的特定顺序规则排列在计算阵列的交叉电路中。

7、进一步的,所述步骤3中的特定顺序包括由高到低或由低到高的顺序。

8、进一步的,所述步骤3中的权重数据平均的放置在不同array中的同一bank-row中。

9、进一步的,所述reram阵列由多个bank构成,并分为了多个array组,bank内部包括多组bank-row,所述reram阵列通过reram器件对比特数据进行映射。

10、进一步的,每个所述reram器件在进行映射时表示2个比特数据。

11、进一步的,所述reram阵列的输出端是多级加法器树,用于对reram阵列内以及reram阵列间输出的部分和进行累加。

12、本发明的有益效果:

13、(1)采用了以bank为核心的映射方案,在阵列bank的维度上延伸拓宽了计算并行度。

14、(2)解决了数据流寻址复杂的问题,reram寻址呈现三维形态,分别为bank group、bank-row、bank col;原有算法需要遍历各个维度,本发明中寻址被降低到两个维度,即bank group和bank-row,寻址逻辑更为简单。

15、(3)简化阵列array规模,兼顾映射算法灵活性的同时,降低阵列加法树级数;

16、简化了控制逻辑的复杂度,降低了控制电路的面积和功耗开销。

技术特征:

1.一种基于reram神经网络加速器的权重映射方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种基于reram神经网络加速器的权重映射方法,其特征在于,所述步骤3中的特定顺序包括由高到低或由低到高的顺序。

3.根据权利要求1所述的一种基于reram神经网络加速器的权重映射方法,其特征在于,所述步骤3中的权重数据平均的放置在不同array中的同一bank-row中。

4.根据权利要求1所述的一种基于reram神经网络加速器的权重映射方法,其特征在于,所述reram阵列由多个bank构成,并分为了多个array组,bank内部包括多组bank-row,所述reram阵列通过reram器件对比特数据进行映射。

5.根据权利要求4所述的一种基于reram神经网络加速器的权重映射方法,其特征在于,每个所述reram器件在进行映射时表示2个比特数据。

6.根据权利要求1所述的一种基于reram神经网络加速器的权重映射方法,其特征在于,所述reram阵列的输出端是多级加法器树,用于对reram阵列内以及reram阵列间输出的部分和进行累加。

技术总结

本发明公开了一种基于ReRAM神经网络加速器的权重映射方法,属于神经网络加速器领域,方法包括:步骤1:以ReRAM阵列的Bank作为第一映射优先级,用来放置卷积输入通道;步骤2:以ReRAM阵列的Bank‑Row方向作为第二映射优先级,在卷积核的输出通道维度上,把不同通道的卷积核摆放置不同的Bank‑Row位置上,直到完成所有输入和输出通道的数据映射要求;步骤3:每个权重数据按照比特位的特定顺序规则排列在计算阵列的交叉电路中。本发明提出一种新颖的高并行度权重映射算法设计,极大程度挖掘了卷积和矩阵乘法计算的并行性的同时,也降低硬件复杂度的。

技术研发人员:景乃峰,董光达,熊大鹏,李涛

受保护的技术使用者:苏州亿铸智能科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!