指令处理器及其方法与流程

本公开涉及计算机,更具体地,涉及一种指令处理器及其方法。

背景技术:

1、中央处理器(central processing unit,cpu)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。现有的cpu都采用流水线技术,一般多级流水线包括取指(instruction fetch)、译码(decoder)、执行(execute)、访存(memory access)和写回(write back),即在同一个处理周期,可以有5条指令分别处于不同的流水级。

2、相关技术中,cpu通常需要多个时钟周期来执行一些较为复杂的待处理指令(例如多周期指令)。当cpu在执行多周期指令结束之后,再执行下一条指令,该过程中存在各指令之间的相关性问题。

3、由于各指令之间存在的相关性,cpu在执行多周期指令时,一般会让在后的待处理指令等待多个时钟周期,在多周期指令执行结束之后再继续执行在后的待处理指令。这种传统的指令处理方式虽然能有效避免各指令之间的相关性所带来的指令执行异常问题,但在后的待处理指令需要等待多个时钟周期才被执行,导致在后的待处理指令不能被流水执行,降低了cpu的执行效率。

技术实现思路

1、本公开提出了一种指令处理器及其方法。

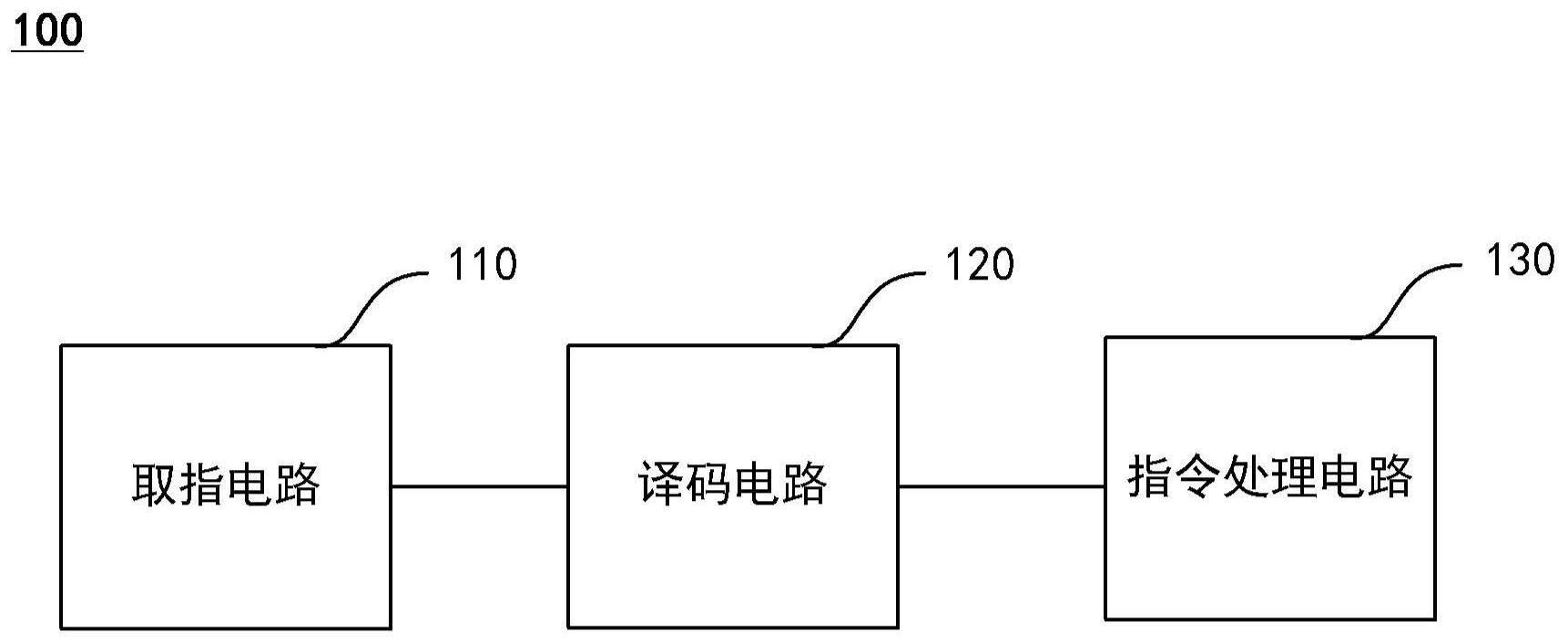

2、根据本公开的第一方面,提出了一种指令处理器,包括取指电路,配置为获取至少两个待处理指令;译码电路,配置为对至少两个待处理指令进行译码处理,得到与至少两个待处理指令分别对应的指令信息;以及根据指令信息,确定至少两个待处理指令的各待处理指令彼此之间的相关性,得到确定结果;其中,指令信息包括源操作数寄存器地址;以及指令处理电路,配置为获取与源操作数寄存器地址对应的源操作数据,并根据确定结果对源操作数据依次进行逻辑运算处理,得到处理后的操作数据。

3、例如,至少两个待处理指令包括至少一个多周期指令和/或至少一个单周期指令;译码电路包括:译码子电路,配置为对至少一个多周期指令和至少一个单周期指令依次进行译码处理,得到指令信息;

4、第一寄存器子电路,配置为对至少一个多周期指令的指令信息进行延时处理,并存储延时处理后的至少一个多周期指令的指令信息;

5、第二寄存器子电路,配置为对延时处理后的至少一个多周期指令的指令信息进行二次延时处理,并存储二次延时处理后的至少一个多周期指令的指令信息;以及指令确认子电路,配置为确认延时处理后的至少一个多周期令的指令信息和至少一个单周期指令的指令信息之间的相关性,得到确认结果。

6、例如,确认结果包括至少一个多周期指令和至少一个单周期指令为相关指令或至少一个多周期指令和至少一个单周期指令为非相关指令;其中,取指电路配置为在确认结果指示至少一个多周期指令和至少一个单周期指令为相关指令的情况下,在多周期指令被译码的过程中,取指电路重新获取单周期指令,并将单周期指令输出至译码电路。

7、例如,译码电路配置为在确认结果指示至少一个多周期指令和至少一个单周期指令为非相关指令的情况下,依次对多周期指令和单周期指令进行译码处理。

8、例如,延时后的至少一个多周期指令和至少一个单周期指令为相关指令,指示延时后的至少一个多周期指令和至少一个单周期指令为先写后读指令、先读后写指令或先写后写指令。

9、例如,还包括控制电路,配置为根据控制使能信号对取指电路进行电控制。

10、例如,控制电路包括状态机子电路,该状态机子电路包括多个信号输入端和多个信号输出端;其中,多个信号输入端的各信号输入端配置为输入输入信号;多个信号输出端的各信号输处端配置为根据输入信号,输出与各输入信号对应的输出信号。

11、例如,取指电路还配置为根据控制使能信号,对至少两个待处理指令进行指令操作处理。

12、例如,控制使能信号包括开始等待多周期指令信号、等待多周期指令完成中信号和结束等待多周期指令信号;取指电路还配置为当开始等待多周期指令信号为高电平时,获取并保存至少两个待处理指令;当等待多周期指令完成中信号为高电平时,停止获取新的待处理指令,并将指令有效信号置为低电平;当结束等待多周期指令信号为高电平时,获取待处理指令,并将指令有效信号置为高电平,以及将待处理指令输出至译码电路。

13、例如,还包括数据存储电路,配置为存储指令信息。

14、例如,数据存储电路包括:第一输入接口,配置为接收指令信息的目的寄存器地址;第二输入接口,配置为接收处理后的操作数据;第三输入接口,配置为接收待处理指令的多周期指令所对应的写回信号。

15、例如,指令处理电路包括第一运算子电路,配置为对源操作数寄存器地址对应的源操作数据进行第一运算处理,得到处理后的第一操作数据;第二运算子电路,配置为对处理后的第一操作数据进行多周期处理,得到处理后的操作数据。

16、例如,指令处理电路还包括加载存储子电路,配置为加载及存储处理后的第一操作数据。

17、例如,还包括指令存储电路,配置为存储待处理指令。

18、根据本公开实施例的第二方面,提供了一种指令处理方法,包括获取至少两个待处理指令;对至少两个待处理指令进行译码处理,得到与至少两个待处理指令分别对应的指令信息;以及根据指令信息,确定至少两个待处理指令的各待处理指令彼此之间的相关性,得到确定结果;其中,指令信息包括源操作数寄存器地址;以及获取与源操作数寄存器地址对应的源操作数据,并根据确定结果对源操作数据依次进行逻辑运算处理,得到处理后的操作数据。

19、根据公开实施例的技术方案,提供了一种指令处理器。该指令处理器通过译码电路对待处理指令进行译码处理,并根据译码得到指令信息确定各待处理指令彼此的相关性,以及根据确定结果对待处理指令依次运算处理,得到处理后的操作数据。该指令处理器有效避免了各待处理指令彼此之间的相关性带来的指令处理异常问题。以及在待处理指令中同时存在多周期指令和单周期指令时,该处理器避免单周期指令需等待多个时钟周期在多周期指令被执行结束后,才执行单周期指令,提高了处理器的执行效率。

技术特征:

1.一种指令处理器,包括:

2.根据权利要求1所述的处理器,其中,所述至少两个待处理指令包括至少一个多周期指令和/或至少一个单周期指令;所述译码电路包括:

3.根据权利要求2所述的处理器,其中,所述确认结果包括所述至少一个多周期指令和所述至少一个单周期指令为相关指令或所述至少一个多周期指令和所述至少一个单周期指令为非相关指令;其中,

4.根据权利要求3所述的处理器,其中,所述译码电路配置为:

5.根据权利要求2所述的处理器,其中,所述延时后的至少一个多周期指令和所述至少一个单周期指令为相关指令,指示所述延时后的至少一个多周期指令和所述至少一个单周期指令为先写后读指令、先读后写指令或先写后写指令。

6.根据权利要求1所述的处理器,还包括:

7.根据权利要求6所述的处理器,其中,所述控制电路包括:

8.根据权利要求6所述的处理器,其中,所述取指电路(ifu)还配置为:

9.根据权利要求7所述的处理器,其中,所述控制使能信号包括开始等待多周期指令信号、等待多周期指令完成中信号和结束等待多周期指令信号;所述取指电路还配置为:

10.根据权利要求1所述的处理器,还包括:

11.根据权利要求10所述的处理器,其中,所述数据存储电路包括:

12.根据权利要求1所述的处理器,其中,所述指令处理电路包括:

13.根据权利要求1所述的处理器,其中,所述指令处理电路还包括:

14.根据权利要求1所述的处理器,还包括:

15.一种指令处理方法,包括:

技术总结

本公开提供了一种指令处理器及其方法,该指令处理器包括取指电路,配置为获取至少两个待处理指令;译码电路,配置为对至少两个待处理指令进行译码处理,得到与至少两个待处理指令分别对应的指令信息;以及根据指令信息,确定至少两个待处理指令的各待处理指令彼此之间的相关性,得到确定结果;其中,指令信息包括源操作数寄存器地址;以及指令处理电路,配置为获取与源操作数寄存器地址对应的源操作数据,并根据确定结果对源操作数据依次进行逻辑运算处理,得到处理后的操作数据。

技术研发人员:王皓星

受保护的技术使用者:北京奕斯伟计算技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!