一种计算机打印口测试治具、测试方法、装置、设备与流程

本发明涉及打印机接口测试,具体涉及一种计算机打印口测试治具、测试方法、装置、设备。

背景技术:

1、随着国产pc,服务器,交换机的发展,本着降低成本和老旧设备替代的平滑运行,国产pc一般都会设计打印口(lpt),用来连接老式的25针式打印机。而在工厂测试中,本着降低成本及测试时间的需求,不可能用打印机作为测试治具去测试,这就需要设计一种全新的测试覆盖率高,低成本,测试速度快的方法。

2、并口打印机主要在linux kernel 2.6以前使用,过去的测试方法基本上都是基于redhat linux开发,直接访问i/o,但是国产pc基本上都设计有专用的国产操作系统,主要是uos(universe operation system,联合操作系统,是统信软件技术有限公司研发的基于linux内核的自主研发的操作系统),终端用户也是在uos下使用,uos的kernel基本都升级到4.19,所以已经不能直接通过直接访问i/o的方式去测试。原来的测试方法已经不能在国产pc的uos操作系统下使用。

3、现有的技术方案基本上都是基于intel,amd的x86 cpu所做的开发,主要存在如下问题:(1)测试覆盖率不够,只测试了cpu到并口卡(国产pc的lpt是独立的pcie插卡)寄存器的值,无法测试lpt连接器的机构部分,如果有焊接不良,无法甄别。(2)在uos操作系统下,直接读写i/o难度较大,而且因为收uos机构的影响,有大量的中断irq的影响,i/o读写的数据很容易受到其它进程的影响,准确性很差,产线程序运行起来误测较多。(3)这种测试覆盖率较低的方案,实际上给公司的国产pc出货带来了潜在的质量风险。

技术实现思路

1、针对现有的测试方法测试覆盖率不够,只测试了cpu到并口卡(国产pc的lpt是独立的pcie插卡)寄存器的值,无法测试lpt连接器的机构部分,如果有焊接不良,无法甄别。在uos操作系统下,直接读写i/o难度较大,而且因为收uos机构的影响,有大量的中断irq的影响,i/o读写的数据很容易受到其它进程的影响,准确性很差,产线程序运行起来误测较多的问题,本发明提供一种计算机打印口测试治具、测试方法、装置、设备。

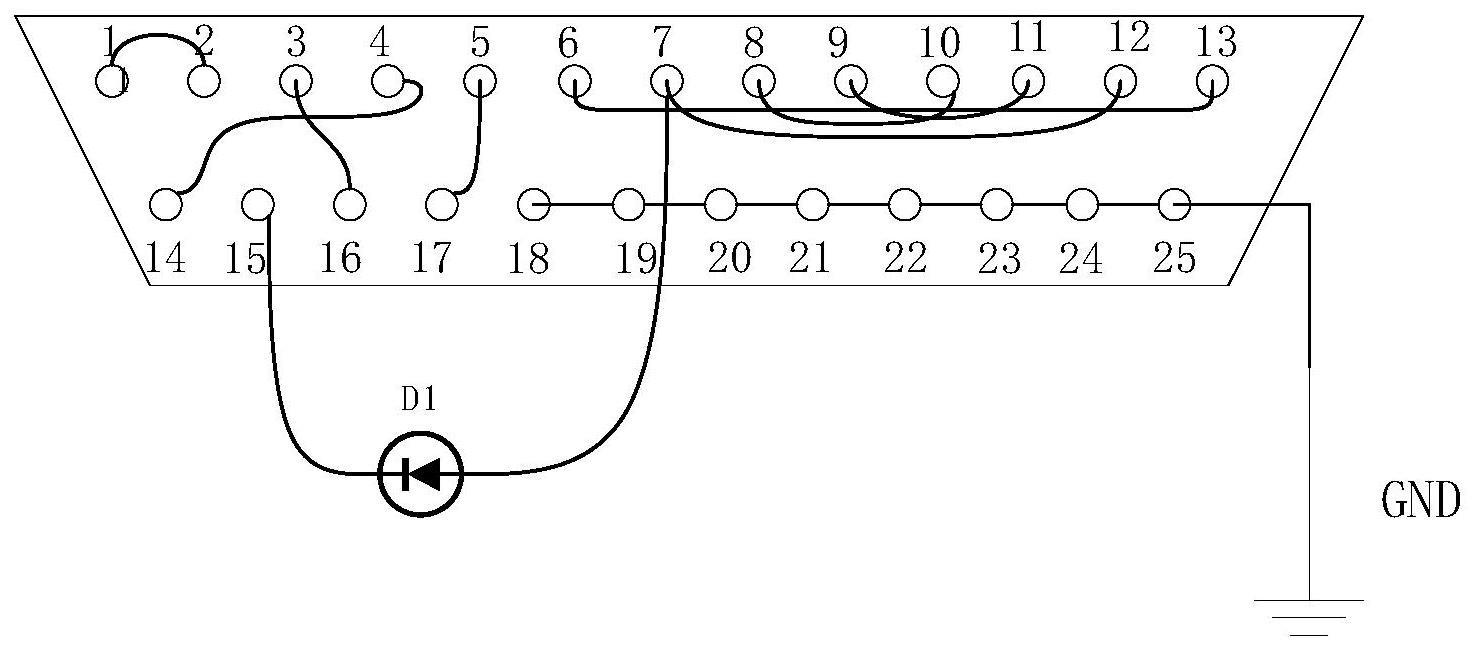

2、第一方面,本发明技术方案提供一种计算机打印口测试治具,包括lpt连接器公头,lpt连接器公头设置有二十五个引脚,lpt连接器公头的第一引脚与第二引脚连接,lpt连接器公头的第三引脚与第十六引脚连接,lpt连接器公头的第四引脚与第十四引脚连接,lpt连接器公头的第五引脚与第十七引脚连接,lpt连接器公头的第六引脚与第十三引脚连接,lpt连接器公头的第七引脚与第十二引脚连接,lpt连接器公头的第八引脚与第十引脚连接,lpt连接器公头的第九引脚与第十一引脚连接,lpt连接器公头的第十八引脚到第二十五引脚接地;lpt连接器公头的第七引脚通过二级管与第十五引脚连接。

3、作为本发明技术方案的进一步限定,lpt连接器公头的第七引脚连接二极管的阳极,第十五引脚连接二极管的阴极。

4、第二方面,本发明技术方案提供一种计算机打印口测试方法,包括如下步骤:

5、将测试治具安装在pc并口连接器上,启动联合操作系统;所述测试治具包括如第一方面所述的测试治具;

6、修改并口驱动程序,关闭中断irq7,编译完成后加载并行端口驱动模块;

7、指定并口并设置数据输出方向为out;

8、产生一个随机数,将产生的随机数写入数据寄存器;

9、设定时间后依次读取数据输出寄存器、状态寄存器、控制寄存器的数据,并将读取的数据保存为对应的变量;

10、将从数据寄存器、控制寄存器和状态寄存器读取的数据分别进行处理比较;

11、当比较结果均相等时,测试通过,否则,测试失败。

12、作为本发明技术方案的进一步限定,指定并口并设置数据输出方向为out的步骤之前包括:

13、查询联合操作系统下并口的数量。

14、作为本发明技术方案的进一步限定,指定并口并设置数据输出方向为out的步骤包括:

15、通过ioctl函数指定并口;

16、设置数据输出的方向为out。

17、作为本发明技术方案的进一步限定,设定时间后依次读取数据输出寄存器、状态寄存器、控制寄存器的数据,并将读取的数据保存为对应的变量的步骤包括:

18、设定时间后读取数据输出寄存器的数据并将读取的数据保存为变量data;

19、读取状态寄存器的数据,并将读取的数据保存为变量stat;

20、读取控制寄存器的数据,并将读取的数据保存为变量ctrl。

21、作为本发明技术方案的进一步限定,将从数据寄存器、控制寄存器和状态寄存器读取的数据分别进行处理比较的步骤包括:

22、将控制寄存器读的数据的低四位异或0x0d后,判断是否和数据输出寄存器的低四位相等;

23、将状态寄存器的bit7异或后,比较状态寄存器的高四位是否和数据寄存器的高四位是否相等;

24、检查状态寄存器的bit3是否和数据寄存器的bit 5相等。

25、作为本发明技术方案的进一步限定,当比较结果均相等时,测试通过,否则,测试失败的步骤之后包括:

26、生成测试报告并输出显示。

27、第三方面,本发明技术方案还提供一种计算机打印口测试装置,包括测试治具,所述测试治具安装在pc并口连接器上,所述测试治具包括如第一方面所述的测试治具;

28、该装置还包括操作系统启动模块、驱动修改模块、并口设置模块、写入模块、读取处理模块和处理比较模块;

29、操作系统启动模块,用于启动联合操作系统;

30、驱动修改模块,用于修改并口驱动程序,关闭中断irq7,编译完成后加载并行端口驱动模块;

31、并口设置模块,用于指定并口并设置数据输出方向为out;

32、写入模块,用于产生一个随机数,将产生的随机数写入数据寄存器;

33、读取处理模块,用于设定时间后依次读取数据输出寄存器、状态寄存器、控制寄存器的数据,并将读取的数据保存为对应的变量;

34、处理比较模块,用于将从数据寄存器、控制寄存器和状态寄存器读取的数据分别进行处理比较;当比较结果均相等时,测试通过,否则,测试失败。

35、作为本发明技术方案的进一步限定,该装置还包括查询模块,用于查询联合操作系统下并口的数量。

36、作为本发明技术方案的进一步限定,并口设置模块,具体用于通过ioctl函数指定并口,设置数据输出的方向为out。

37、作为本发明技术方案的进一步限定,读取处理模块,具体用于设定时间后读取数据输出寄存器的数据并将读取的数据保存为变量data;读取状态寄存器的数据,并将读取的数据保存为变量stat;读取控制寄存器的数据,并将读取的数据保存为变量ctrl。

38、作为本发明技术方案的进一步限定,处理比较模块,具体用于将控制寄存器读的数据的低四位异或0x0d后,判断是否和数据输出寄存器的低四位相等;将状态寄存器的bit7异或后,比较状态寄存器的高四位是否和数据寄存器的高四位是否相等;检查状态寄存器的bit3是否和数据寄存器的bit 5相等。

39、作为本发明技术方案的进一步限定,该装置还包括输出模块,用于生成测试报告并输出显示。

40、第四方面,本发明技术方案还提供一种电子设备,所述电子设备包括:

41、至少一个处理器;以及,

42、与所述至少一个处理器通信连接的存储器;其中,

43、存储器存储有可被至少一个处理器执行的计算机程序指令,所述计算机程序指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行如第二方面所述的计算机打印口测试方法。

44、从以上技术方案可以看出,本发明具有以下优点:根据并口的信号特点,设计出一种专用的并口测试治具,并结合并口驱动的修改,能够在低成本的情况下,保证出货计算机能正常使用并口打印机。实现了国产操作系统uos下对国产pc并口功能测试的完全覆盖,使工厂出货质量得到了保证。

45、此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

46、由此可见,本发明与现有技术相比,具有突出的实质性特点和显著地进步,其实施的有益效果也是显而易见的。

- 还没有人留言评论。精彩留言会获得点赞!