基于边沿传输延迟的存算单元电路及乘累加计算电路

本发明涉及集成电路设计,更具体的,涉及基于边沿传输延迟的存算单元电路,和采用该种单元电路构建的多比特时域的乘累加计算电路。

背景技术:

1、存算一体技术突破了冯·诺伊曼瓶颈,为人工智能时代带来新的变革。在存算一体架构下,存储器不仅保留了原有的存储功能,还可以在读出数据的过程中在其内部执行一些逻辑或乘加运算,即不需要将大量原始数据传输到处理器计算,因此存内计算大大减少了计算过程中存取数据造成的能量损耗,增加了数据的吞吐量,极大提高了计算速度和能效。

2、静态随机存储器(static random-access memory,sram)读取数据速度快,与先进逻辑工艺具有较好的兼容性,因此是存内计算常见的存储器。sram存内乘累加(multiply-accumulate,mac)计算可以根据计算原理分为电压域、数字域、时间域(time domain,td)、频域等,其中,时域计算数据表示为脉冲宽度或路径延迟,mac是通过按比例改变脉冲宽度或是比较脉冲边沿时间差来实现的。

3、时域计算打破了模拟域中工作电压、电流对计算精度的限制,同时具有较低能耗。但针对不同的乘法实现结构,基于路径延迟的td-mac单元大多还是停留在单比特计算,工作的效率仍有提高空间。此外,时域计算延迟时序易受工艺、电压、温度影响,延迟信号变化不稳定,对量化工作造成困难。

技术实现思路

1、基于此,有必要针对现有时域计算效率偏低的问题,提供基于边沿传输延迟的存算单元电路和采用该种单元电路构建的多比特时域的乘累加计算电路,其中,存算单元电路可进行8bit输入乘2bit权重,多比特时域的乘累加计算电路可稳定、准确地实现多比特乘累加操作。

2、本发明采用以下技术方案实现:

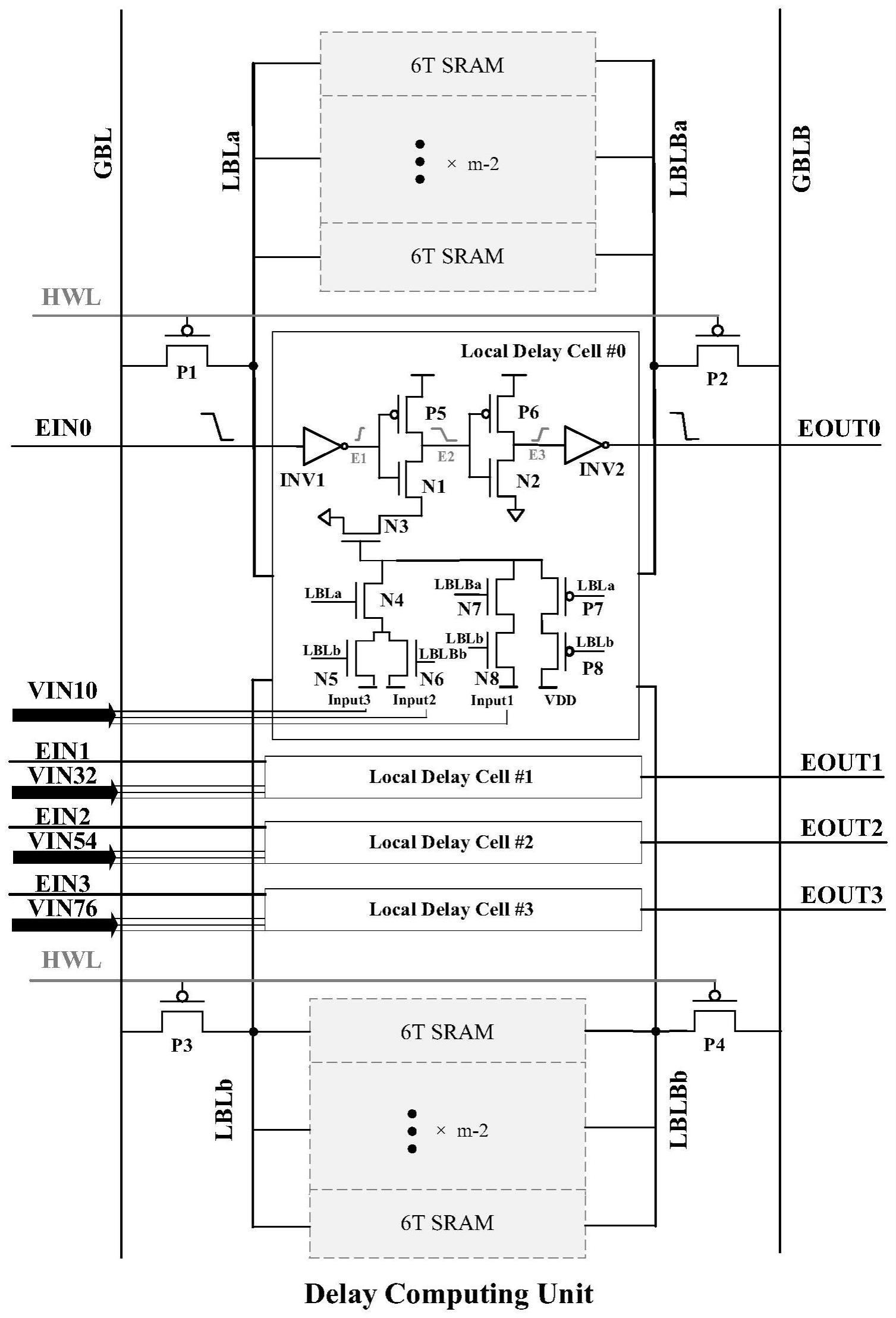

3、第一方面,本发明提供了基于边沿传输延迟的存算单元电路,包括两个sram存储部、位线联通开关、延迟计算单元。

4、两个sram存储部用于存储计算时需要的权重。其中一个sram存储部表示高位,另一个sram存储部表示低位,以实现权重位的加权。高位sram存储部共用同一根局部位线lbla、同一根局部位线lblba,低位sram存储部共用同一根局部位线lblb、同一根局部位线lblbb。两个sram存储部共用同一根全局位线gbl、同一根全局位线gblb。

5、位线联通开关用于控制局部位线与全局位线接通或断开。

6、延迟计算单元用于计算2bit权重乘8bit输入。延迟计算单元包括四个局部延时单元。8bit输入分为4个2bit输入,4个2bit输入以组电压的形式一对一输入到四个局部延时单元中,用于控制延迟时长。局部延时单元与两个sram存储部电性连接,用于计算2bit权重乘2bit输入。

7、其中,2bit权重包括从高位sram存储部获取的1bit权重和从底位sram存储部获取的1bit权重。

8、每个局部延时单元均接入一个输入边沿信号,通过传输延迟时长表征乘积结果。局部延时单元根据乘积结果,在固有延迟的基础上延迟n*δt,其中,n为乘积结果。

9、该种存算单元电路的实现根据本公开的实施例的方法或过程。

10、第二方面,本发明公开了一种多比特时域的乘累加计算电路,用于计算k组第一方面存算单元电路运算结果的累加,即计算2bit权重乘8bit输入的乘累加。

11、多比特时域的乘累加计算电路包括k组第一方面的基于边沿传输延迟的存算单元电路。k>1。

12、k组的存算单元电路横向串联,构成k级运算电路。上一级运算电路的输出边沿信号作为下一级运算电路的输入边沿信号。k级运算电路共用同一根横向字线hwl。

13、该种多比特时域的乘累加计算电路的实现根据本公开的实施例的方法或过程。

14、与现有技术相比,本发明具备如下有益效果:

15、1,本发明的存算单元电路采用了由四个局部延时单元组成的延迟计算单元,每个局部延时单元可以计算2bit权重乘2bit输入,使延迟计算单元可以计算2bit权重乘8bit输入,满足提高了单元计算效率;此外,本发明存算单元电路可采用k组进行横向串联使用,构建出k级运算电路,可以计算出k个2bit权重乘8bit输入之和,实现多比特时域的乘累加。

16、2,本发明的延迟计算单元在边沿的输入和输出端添加反相器,其中一个反相器规范输入边沿信号为快速变化的上升沿信号e1,另一个反相器规范延迟信号e3为快速变化的下降沿信号,并作为输出边沿信号,这样使输入和输出理想化,使边沿延迟的计量更趋于理想;而且在多比特时域的乘累加计算电路中,上一级的输出边沿信号可作为下一级的输入边沿信号,由于信号经过上述处理后,使延迟稳定准确,从而保证整体的计算准确性。

技术特征:

1.基于边沿传输延迟的存算单元电路,其特征在于,包括:

2.根据权利要求1所述的基于边沿传输延迟的存算单元电路,其特征在于,高位sram存储部包括若干个6t-sram存储单元,共用同一根局部位线lbla、同一根局部位线lblba;

3.根据权利要求1所述的基于边沿传输延迟的存算单元电路,其特征在于,每组组电压包括由2bit输入转换成的三个输入电压;

4.根据权利要求1所述的基于边沿传输延迟的存算单元电路,其特征在于,所述位线联通开关包括:

5.根据权利要求4所述的基于边沿传输延迟的存算单元电路,其特征在于,所述局部延时单元包括:

6.根据权利要求5所述的基于边沿传输延迟的存算单元电路,其特征在于,p5/n1/n3组成反相结构一、p6/n2组成反相结构二,两者构成缓冲器,用于延迟信号;

7.根据权利要求6所述的基于边沿传输延迟的存算单元电路,其特征在于,所述反相器inv1包括:

8.根据权利要求7中任一项所述的基于边沿传输延迟的存算单元电路,其特征在于,所述存算单元电路的一个计算周期包括两个阶段,两个阶段包括:

9.一种多比特时域的乘累加计算电路,用于计算2bit权重乘8bit输入的乘累加,其特征在于,包括k组如权利要求1-8中任一项所述的存算单元电路;k>1;

10.根据权利要求9所述的多比特时域的乘累加计算电路,其特征在于,

技术总结

本发明涉及集成电路设计技术领域,更具体的,涉及基于边沿传输延迟的存算单元电路,和采用该种单元电路构建的多比特时域的乘累加计算电路。本发明的存算单元电路包括两个SRAM存储部、延迟计算单元、位线联通开关。其中,两个SRAM存储部用于存储计算时需要的权重,并提供2bit权重作为乘数。延迟计算单元采用了由四个局部延时单元,每个局部延时单元可以计算2bit权重乘2bit输入,使延迟计算单元可以计算2bit权重乘8bit输入,以提高计算效率。此外,在局部延时单元中添加用于规范边沿信号的反相器,提高单元延迟和时域累加的准确性。

技术研发人员:郭嘉琦,柏苏,朱童,姜瑞齐

受保护的技术使用者:安徽大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!