一种编译码系统

本发明涉及通信,尤其涉及一种编译码系统。

背景技术:

1、随着芯片产业的发展,芯片逐渐向系统芯片的领域发展,其存储容量和数据处理效率也有了与以往截然不同的提升,然而随之而来的是功耗的剧增。

2、ldpc(low-density parity-check,低密度奇偶校验)编译码涉及大多数通信系统,以其优秀的性能逐渐成为包括但不限于卫星通信、手机通信等领域的首选。其编译码所需要的数据量大,计算繁琐,尤其是译码迭代次数较多,耗时长,功耗大,对于往往应用于边缘环境下的ldpc编译码微控制器系统芯片,其使用功耗会受到引用场景的极大限制,因此需要进行低功耗设计和处理。

技术实现思路

1、鉴于上述问题,提出了本发明以便提供一种克服上述问题或者至少部分地解决上述问题的编译码系统。

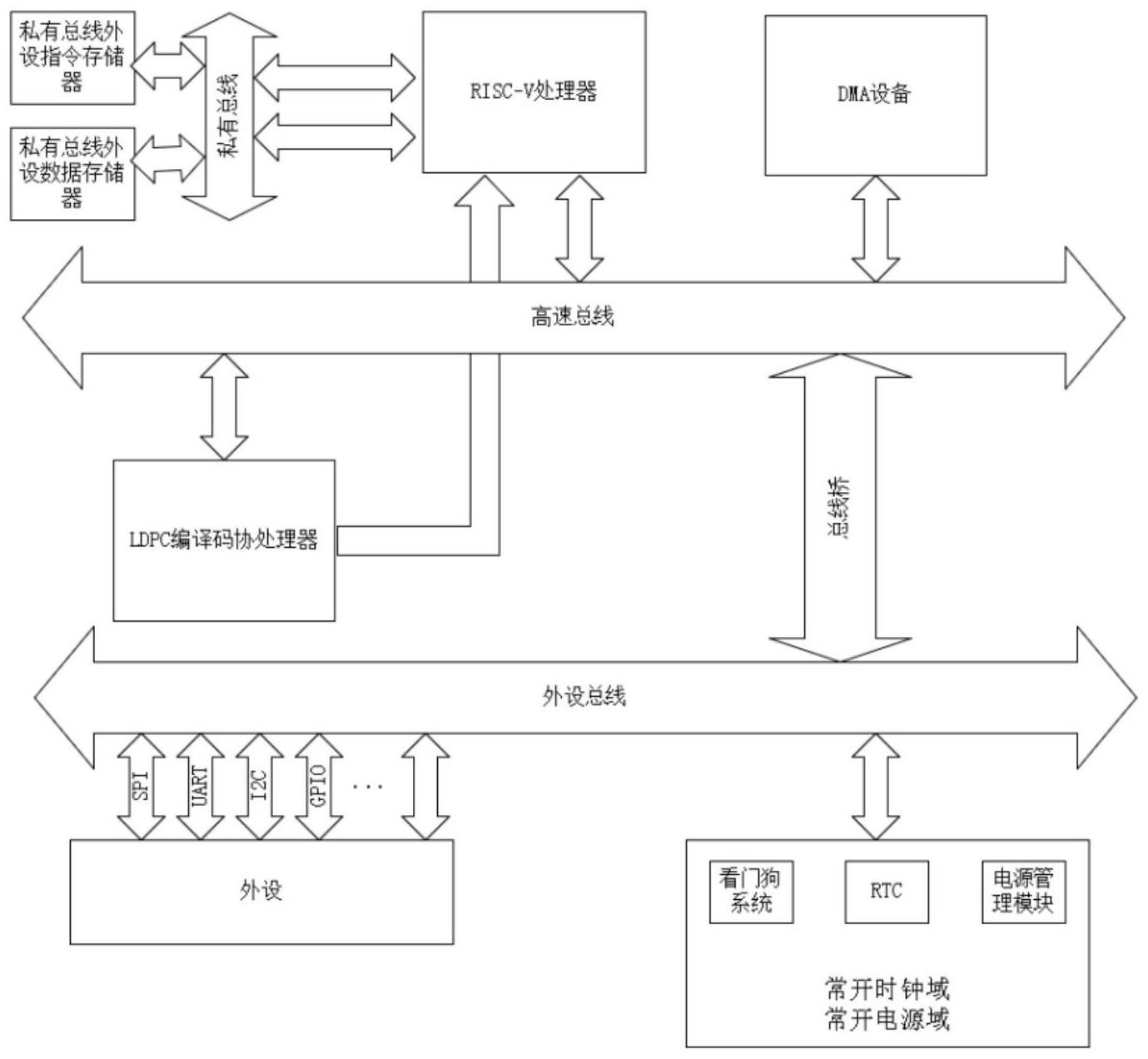

2、提供一种编译码系统,包括:risc-v处理器、ldpc编译码器以及通用设备;

3、所述risc-v处理器与所述ldpc编译码器、所述通用设备通信连接;

4、所述risc-v处理器,用于根据编写的程序进行指令的执行以及数据的保存以实现对编译码系统的控制;

5、所述ldpc编译码器,用于在risc-v处理器的调度下进行编译码工作以及与通用设备的数据交互。

6、可选的,所述risc-v处理器,包括:

7、指令译码单元,用于将所述指令翻译成对应操作的控制信号;

8、执行单元,用于根据所述对应操作的控制信号执行运算;

9、访存单元,用于根据所述对应操作的控制信号访问数据;

10、所述执行单元、所述访存单元并行读取所述指令译码单元翻译出的所述对应操作的控制信号。

11、可选的,所述risc-v处理器,包括:

12、第一流水线寄存器,用于保存所述指令,供所述指令译码单元读取;

13、第二流水线寄存器,用于保存所述执行单元在执行运算中形成的数据信号和控制信号,以及用于保存所述访存单元在访问数据时形成的数据信号和控制信号。

14、可选的,所述risc-v处理器,包括:

15、第三流水线寄存器,用于保存所述对应操作的控制信号,供所述执行单元或者所述访存单元读取。

16、可选的,所述risc-v处理器,包括:

17、私有存储器,用于保存所述指令与所述数据;

18、预取指令单元,用于从所述私有存储器中读取并预存所述指令;

19、取指令单元,用于读取所述预取指令单元或者所述私有存储器中的指令并保存在所述第一流水线寄存器中;

20、寄存器堆单元,用于临时保存数据;

21、写回单元,用于将所述第二流水线寄存器中保存的数据写入所述寄存器堆单元;

22、控制单元,用于处理所述编译码系统中的冲突、等待、中断和异常。

23、可选的,所述私有存储器,包括私有总线外设指令存储器、紧耦合指令存储器,所述预取指令单元从所述私有总线外设指令存储器中读取所述指令;所述取指令单元从所述预取指令单元或者所述紧耦合指令存储器中读取所述指令。

24、可选的,所述私有存储器,包括私有总线外设数据存储器、紧耦合数据存储器,所述访存单元根据所述对应操作的控制信号访问所述私有总线外设数据存储器、所述紧耦合数据存储器或者所述通用设备中的所述数据。

25、可选的,所述ldpc编译码器,包括:

26、数据缓存单元,用于暂时保存数据;

27、编码器,用于进行ldpc编码;

28、译码器,用于进行ldpc译码;

29、存储器,用于保存编译码所需要的数据、中间变量值;

30、所述编码器与所述译码器分立且并行运行。

31、可选的,所述通用设备,包括:

32、外设,用于进行数据交互;

33、存储器访问设备,用于在所述risc-v处理器的调度下,命令所述外设与所述ldpc编译码器进行数据交互。

34、可选的,所述通用设备,还包括:定时器、实时时钟、电源管理模块;

35、所述定时器、所述实时时钟、所述电源管理模块位于常开电源域和常开时钟域;

36、位于所述常开电源域外的设备电源采用门控电源,所述电源管理模块,用于控制所述门控电源在所述设备不工作时关闭其电源,在所述设备工作时打开其电源;

37、位于所述常开电源域外的设备时钟采用门控时钟,所述门控时钟在所述设备不工作时关闭其时钟,在所述设备工作时打开其时钟;

38、所述实时时钟,用于供所述设备的时钟打开时读取时间;

39、所述定时器,用于对所述设备进行重启,使所述设备的电源、时钟打开时处于初始状态。

40、本发明实施例中提供的技术方案,至少具有如下技术效果或优点:

41、本发明实施例提供的编译码系统,以risc-v处理器作为通用处理器与ldpc编译码器进行联合使用,risc-v处理器可编辑性强,可以灵活编写程序进行指令的调度、执行以及数据的访问、保存,以实现对编译码系统的控制;ldpc编译码协处理器,可以脱离risc-v处理器独立进行ldpc编译码的运算和处理;编译码系统从整体上有效的降低risc-v处理器的功耗、提高ldpc编译码的处理速度,适用性广、可移植性强、可靠性高。

42、该编译码系统在架构层面可以使用多种手段降低功耗,一方面,可通过灵活的编辑,对risc-v处理器的内核配置为低功耗的三级流水线或者四级流水线,使用时在满足性能要求的范围内尽可能降低流水线的级数,从而降低功耗。另一方面,使risc-v处理器内核中的执行单元和访存单元可分别读取指令译码单元翻译出对应操作的控制信号,依照控制信号独立运行对应操作,指令译码单元翻译出对应操作的控制信号可以越过执行单元直接进入访存单元,降低数据通路的长度,进一步降低功耗。再一方面,使用多种低功耗手段降低功耗,例如通过电源开关控制、时钟开关控制在不必要运行的情况下切断部分设备的电源、时钟以降低功耗;在关键路径上使用低阈值电压单元提高速度,非关键路径使用高阈值电压单元降低漏电流功耗;在非关键路径上使用尺寸小的门以降低驱动电流等。

43、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种编译码系统,其特征在于,包括:risc-v处理器、ldpc编译码器以及通用设备;

2.如权利要求1所述的编译码系统,其特征在于,所述risc-v处理器,包括:

3.如权利要求2所述的编译码系统,其特征在于,所述risc-v处理器,包括:

4.如权利要求3所述的编译码系统,其特征在于,所述risc-v处理器,包括:

5.如权利要求3所述的编译码系统,其特征在于,所述risc-v处理器,包括:

6.如权利要求5所述的编译码系统,其特征在于,所述私有存储器,包括私有总线外设指令存储器、紧耦合指令存储器;

7.如权利要求5所述的编译码系统,其特征在于,所述私有存储器,包括私有总线外设数据存储器、紧耦合数据存储器;

8.如权利要求1所述的编译码系统,其特征在于,所述ldpc编译码器,包括:

9.如权利要求1至8任一所述的编译码系统,其特征在于,所述通用设备,包括:

10.如权利要求9所述的编译码系统,其特征在于,所述通用设备,还包括:定时器、实时时钟、电源管理模块;

技术总结

本发明公开了一种编译码系统,包括RISC‑V处理器、LDPC编译码器以及通用设备。所述RISC‑V处理器与所述LDPC编译码器、所述通用设备通信连接<subgt;;</subgt;所述RISC‑V处理器,用于根据编写的程序进行指令的执行以及数据的保存以实现对编译码系统的控制;所述LDPC编译码器,用于在RISC‑V处理器的调度下进行编译码工作以及与通用设备的数据交互。通过本发明提供了一种处理速度,适用性广、可移植性强、可靠性高的编译码系统。

技术研发人员:宋秋阳,余志杰,刘学勇,陈杰,王海永

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!