一种同步配置寄存器的电路、方法及同步配置模块与流程

本发明涉及半导体,特别是涉及一种同步配置寄存器的电路、方法及同步配置模块。

背景技术:

1、现有技术中,芯片中功能模块的内部都设置有多个寄存器,通过对这些寄存器进行配置,使芯片能够按照指定的逻辑功能进行正常工作。主流的配置寄存器方案有以下几种:

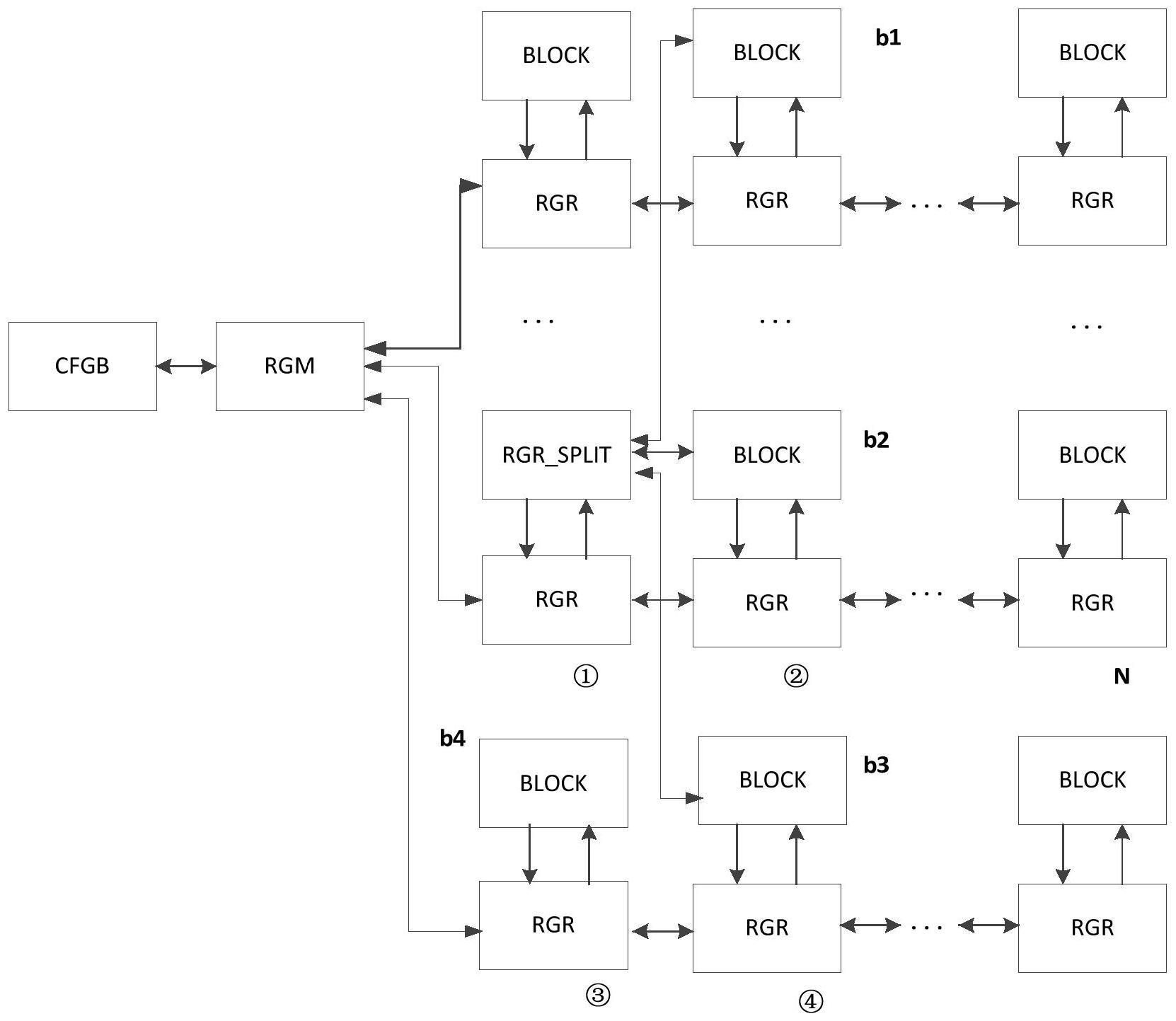

2、第一种配置寄存器方案,该方案是基于hosttree的结构进行设计的,hosttree结构由rgm(register master,寄存器控制)和rgr(register route,寄存器路由)组成,如图1所示,图1为现有技术中第一种配置寄存器方案的示意图,其中,rgm模块用于解析地址信息,并基于地址信息向指定rgr模块发送配置信息。rgr模块用于接收并解析rgm模块发送的配置信息,function block(功能模块)为具有独立功能的模块,以下简称block。配置信息从rgm模块到各个具有独立功能的模块,取决于该功能模块与rgm模块的距离,在某些特殊场景,多个功能模块的寄存器需要同时进行配置,如果这些功能模块布局在不同的链路上,或在同一链路上的不同节点,就无法同时配置。

3、第二种配置寄存器方案,如图2所示,图2为现有技术中第二种配置寄存器方案的示意图,rgm模块管理所有功能模块,每个功能模块都有独立的总线和rgm模块相连,此方案虽然延时比较低,但扇出极大,且需要rgm模块和多个功能模块都有通信。

4、第三种配置寄存器方案,如图3所示,图3为现有技术中第三种配置寄存器方案的示意图,该方案不再需要rgm模块对地址信息进行解析,所有的rgr模块在一条链路上,地址信息和配置信息从cfgb模块发出,每个rgr模块都会解析地址信息,如果地址信息匹配,则把配置信息下发给对应的功能模块。但是该方案对链路上靠后的功能模块寄存器配置的时刻较晚,不能实现对多个功能模块进行同时配置。

5、可见,以上三种方案都是依据功能模块的布局顺序,依次配置功能模块的寄存器,配置速度比较慢,同时也无法满足特定场景下同时配置多个功能模块的需求。

技术实现思路

1、本发明实施例的目的在于提供一种同步配置寄存器的电路、方法及同步配置模快,用以解决现有技术中不能同步配置寄存器,且配置速度较低的问题。具体技术方案如下:

2、为实现上述目的,本发明实施例提供了一种同步配置寄存器的电路,所述电路包括:寄存器配置桥cfgb模块,寄存器控制rgm模块,与所述rgm模块分别连接的多个配置链路,每个配置链路包括多个依次相连的寄存器路由rgr模块,每个rgr模块连接一个功能模块或一个同步配置模块;所述同步配置模块与预先设定的需要同步配置寄存器的多个功能模块相连;

3、所述cfgb模块被配置为:将不同接口协议下的初始配置信息转换为统一接口协议下的配置信息,并将所述配置信息发送至所述rgm模块,所述配置信息包括:目标地址和寄存器配置数据;

4、所述rgm模块被配置为:确定所述目标地址所属的目标配置链路,将所述配置信息发送至所述目标配置链路的首个rgr模块;

5、所述rgr模块被配置为:判断所述目标地址是否属于自身相连的功能模块或同步配置模块,若是,将所述寄存器配置数据发送至自身相连的功能模块或同步配置模块;若否,将所述配置信息发送至自身相连的另一个rgr模块;

6、所述同步配置模块被配置为:对所述配置信息进行复制,并同步发送至自身相连的功能模块;

7、所述功能模块被配置为:基于所述寄存器配置数据对内部寄存器进行配置。

8、可选的,所述配置信息还包括:目标寄存器地址;

9、所述功能模块具体被配置为:基于所述寄存器配置数据和所述目标寄存器地址对内部寄存器进行配置。

10、可选的,所述同步配置模块还被配置为:接收自身相连的功能模块在完成寄存器配置后发送的第一反馈信息,并将所述第一反馈信息发送至所述rgr模块;

11、所述rgr模块还被配置为:接收自身相连的功能模块或同步配置模块发送的所述第一反馈信息,并将所述第一反馈信息发送至所述rgm模块;

12、所述rgm模块还被配置为:接收所述rgr模块发送的所述第一反馈信息,并将所述第一反馈信息发送至所述cfgb模块;

13、所述cfgb模块还被配置为:接收所述rgm模块发送的所述第一反馈信息,并将所述第一反馈信息转换为适用不同接口协议的第二反馈信息。

14、可选的,所述第一反馈信息包括:读数据rdata和写有效反馈信号。

15、为实现上述目的,本发明实施例还提供了一种同步配置寄存器的方法,所述方法包括:cfgb模块将不同接口协议下的初始配置信息转换为统一接口协议下的配置信息,并将所述配置信息发送至rgm模块,所述配置信息包括:目标地址和寄存器配置数据;

16、所述rgm模块确定所述目标地址所属的目标配置链路,将所述配置信息发送至所述目标配置链路的首个rgr模块;

17、所述rgr模块判断所述目标地址是否属于自身相连的功能模块或同步配置模块,若是,将所述寄存器配置数据发送至自身相连的功能模块或同步配置模块;若否,将所述配置信息发送至自身相连的下一个rgr模块;

18、所述同步配置模块对所述配置信息进行复制,并同步发送至自身相连的功能模块;

19、所述功能模块基于所述寄存器配置数据对内部寄存器进行配置。

20、可选的,所述配置信息还包括:目标寄存器地址;

21、所述功能模块具体用于基于所述寄存器配置数据和所述目标寄存器地址对内部寄存器进行配置。

22、可选的,所述同步配置模块还用于接收自身相连的功能模块在完成寄存器配置后发送的第一反馈信息,并将所述第一反馈信息发送至所述rgr模块;

23、所述rgr模块还用于接收自身相连的功能模块或同步配置模块发送的所述第一反馈信息,并将所述第一反馈信息发送至所述rgm模块;

24、所述rgm模块还用于接收所述rgr模块发送的所述第一反馈信息,并将所述第一反馈信息发送至所述cfgb模块;

25、所述cfgb模块还用于接收所述rgm模块发送的所述第一反馈信息,并将所述第一反馈信息转换为适用不同接口协议的第二反馈信息。

26、可选的,所述第一反馈信息包括:读数据rdata和写有效反馈信号。

27、为实现上述目的,本发明实施例还提供了一种同步配置模块,包括:

28、复制单元,所述复制单元与预先设定的需要同步配置寄存器的n个功能模块相连;

29、n个第一寄存器,分别与n个功能模块一一对应连接;n个第二寄存器,分别与n个功能模块一一对应连接;

30、与逻辑单元,所述与逻辑单元的n个输入引脚分别与n个第一寄存器连接;

31、第一数据选择器mux,所述第一mux的第一输入通道连接有效信号寄存单元的输出引脚,所述第一mux的第二输入通道连接所述与逻辑单元的输出引脚;

32、数据校验单元,所述数据校验单元的n个输入引脚分别与n个第二寄存器连接;

33、第二mux,所述第二mux的输入通道连接n个第二寄存器中的任一个寄存器,所述第二mux的通道选择引脚连接所述数据校验单元的输出引脚;

34、所述复制单元被配置为:接收rgr模块发送的配置信息,所述配置信息包括:写使能wr信号、写数据data、写有效信号valid和写请求req信号,将所述配置信息复制n份,并同步分发至相连的n个功能模块;

35、有效信号寄存单元被配置为:通过输入引脚获取所述写有效信号valid,并在锁存预设拍数后输出所述写有效信号valid;

36、所述第一mux被配置为:通过通道选择引脚获取所述写使能wr信号,在所述写使能信号有效期间,保持所述第一输入通道导通,否则保持所述第二输入通道导通;

37、所述n个第一寄存器被配置为:接收并锁存自身相连的功能模块在完成寄存器配置后返回的写有效反馈信号;

38、所述n个第二寄存器被配置为:接收并锁存自身相连的功能模块在完成寄存器配置后返回的读数据rdata;

39、所述数据校验单元被配置为:对所述n个第二寄存器锁存的读数据进行一致性校验,若通过校验,则输出使能信号,在所述使能信号有效期间,保持所述第二mux的输入通道导通。

40、可选的,所述第一mux还被配置为:当所述第二输入通道导通时,将所述写有效反馈信号通过输出引脚发送至与所述同步配置模块相连的寄存器路由rgr模块;

41、所述第二mux还被配置为:当所述输入通道导通时,将所述读数据rdata通过输出引脚发送至所述rgr模块。

42、本发明实施例有益效果:

43、应用本发明实施例提供的一种同步配置寄存器的电路,包括:寄存器配置桥cfgb模块,寄存器控制rgm模块,与rgm模块分别连接的多个配置链路,每个配置链路包括多个依次相连的rgr模块,每个rgr模块连接一个功能模块或一个同步配置模块;同步配置模块与预先设定的需要同步配置寄存器的多个功能模块相连;cfgb模块被配置为:将不同接口协议下的初始配置信息转换为统一接口协议下的配置信息,并将配置信息发送至rgm模块,配置信息包括:目标地址和寄存器配置数据;rgm模块被配置为:确定目标地址所属的目标配置链路,将配置信息发送至目标配置链路的首个rgr模块;rgr模块被配置为:判断目标地址是否属于自身相连的功能模块或同步配置模块,若是,将寄存器配置数据发送至自身相连的功能模块或同步配置模块;若否,将配置信息发送至自身相连的另一个rgr模块;同步配置模块被配置为:对配置信息进行复制,并同步发送至自身相连的功能模块,以使与该同步配置模块相连的功能模块基于寄存器配置数据配置内部寄存器。

44、可见,本发明实施例提供的同步配置寄存器电路,在hosttree电路结构中添加同步配置模块,在扇出相对较小的情况下,将芯片上布局较为分散、间隔较远,但耦合度较高需要同时配置寄存器的功能模块,预先与同一同步配置模块连接,这样可以不依赖功能模块的布局,从电路结构上解决位于不同链路位置相差较远的功能模块,或位于同一链路不同位置的功能模块,不能同时配置寄存器的问题。

45、具体的,本发明通过rgm模块对目标地址进行识别,确定目标地址所属的配置链路后,将配置信息发送至目标配置链路的首个rgr模块。配置链路上的rgr模块再对目标地址做进一步识别,当目标地址为自身相连同步配置模块的寄存器地址时,将目标地址发送到同步配置模块。

46、因为同步配置模块预先和需要进行同步配置的功能模块相连,因此,同步配置模块在接收到配置信息,将配置信息复制多份后,就可以将多份配置信息同时发送给需要同步配置的多个功能模块,即针对多个功能模块同时下发配置信息,这不仅实现了同时下发配置信息给多个功能模块的寄存器,也提升了寄存器配置的速度。

47、当然,实施本发明的任一产品或方法并不一定需要同时达到以上所述的所有优点。

- 还没有人留言评论。精彩留言会获得点赞!