时钟同步电路及测试机的制作方法

本申请属于半导体,具体涉及一种时钟同步电路及测试机。

背景技术:

1、现有时钟同步技术均是采用通用逻辑芯片,下发时钟信号到各个子板卡。因为逻辑芯片的各个通道之间的延迟偏离控制在几百皮秒,难以做严格的对齐,因此下发的时基信号(timebase)与同步触发信号(synctrigger)清零信号,仅能实现纳秒级的同步。

2、为了提高同步精度,只能提高时基信号的频率。但是时基信号的频率对于输出端、接收端都有上限,因此精度无法达到小于1纳秒级。同时时钟板卡下发到各个子板卡的时基信号和同步触发信号没有严格的时序约束关系,导致同步触发信号同步触发计数器清零的时间点,各个子板卡无法统一,存在跨时钟周期的问题,精度取决于时基信号的频率。

3、此外,经过逻辑芯片送出来的时基信号抖动性能恶化严重。通用逻辑芯片的电路规模比较庞大,因此物料成本较高。同时通用逻辑芯片需要进行仿真编程,因此人力成本较高。

技术实现思路

1、本申请的目的是提供一种时钟同步电路及测试机以避免采用逻辑芯片进行时钟同步。

2、根据本申请实施例的第一方面,提供了一种时钟同步电路,该电路包括:

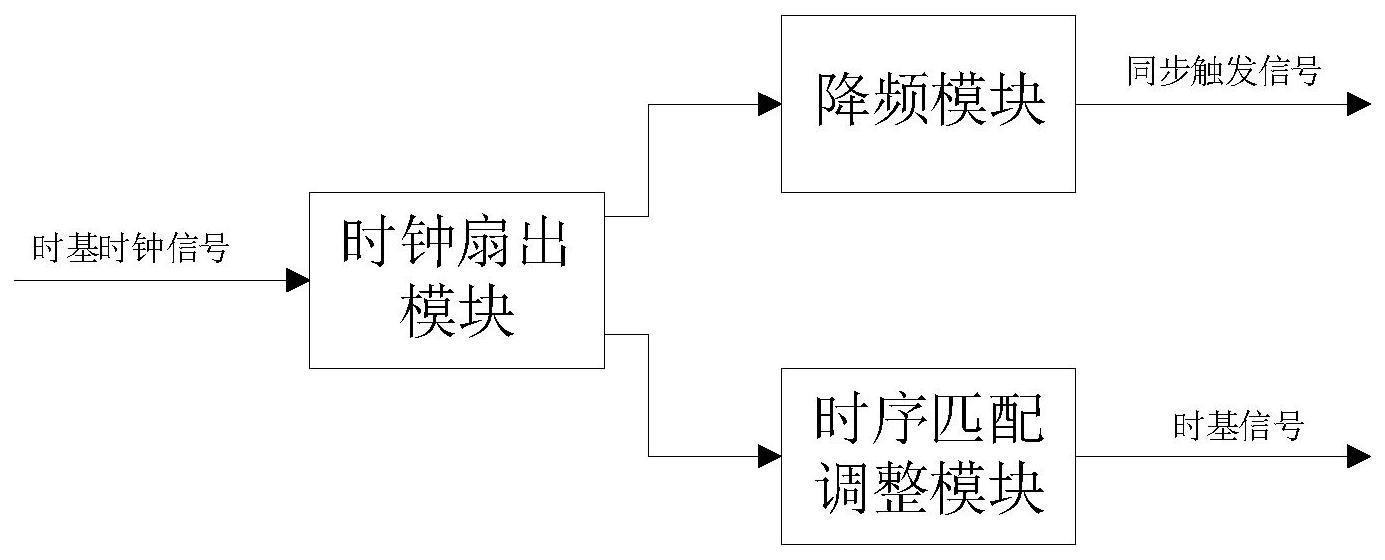

3、时钟扇出模块,用于将时基时钟信号进行扇出,形成第一时钟信号和第二时钟信号;

4、降频模块,与时钟扇出模块连接,用于将第一时钟信号进行降频处理,形成同步触发信号;

5、时序匹配调整模块,与时钟扇出模块连接,用于对第二时钟信号进行时序匹配调整,形成与同步触发信号具有预设时序约束关系的时基信号。

6、在本申请的一些可选实施例中,第一时钟信号的频率和第二时钟信号的频率相同,第一时钟信号和第二时钟信号的相位差恒定;

7、预设时序约束关系为:时基信号的频率为同步触发信号的频率的整数倍,且同步触发信号的上升沿与时基信号的上升沿相差时基信号的半个周期。

8、在本申请的一些可选实施例中,时钟同步电路还包括:

9、第一驱动模块,与降频模块连接,用于将同步触发信号驱动到目标板卡;

10、第二驱动模块,与时序匹配调整模块连接,用于将时基信号驱动到所述目标板卡。

11、在本申请的一些可选实施例中,目标板卡包括接收芯片;接收芯片用于根据同步触发信号和时基信号进行同步计数。

12、在本申请的一些可选实施例中,目标板卡还包括整数计数器和小数计数器;整数计数器和小数计数器分别与接收芯片连接,接收芯片具体用于在接收到同步触发信号的上升沿,在整数计数器上增加第一阈值,并清零小数计数器;接收芯片具体还用于在接收到时基信号的上升沿,在小数计数器上增加第二阈值,直到再次接收到同步触发信号的上升沿,清零小数计数器。

13、在本申请的一些可选实施例中,第一驱动模块与目标板卡之间的走线,和第二驱动模块与目标板卡之间的走线等长。

14、在本申请的一些可选实施例中,目标板卡为多个;第一驱动模块与多个目标板卡之间的走线均等长,且第二驱动模块与多个目标板卡之间的走线均等长。

15、在本申请的一些可选实施例中,第一驱动模块与第二驱动模块均为低偏斜缓冲器,第一驱动模块的时钟偏移与第二驱动模块的时钟偏移相同。

16、在本申请的一些可选实施例中,时钟扇出模块为时钟扇出缓冲器,降频模块为分频器,时序匹配调整模块为延迟补偿器。

17、根据本申请实施例的第二方面,提供一种测试机,该测试机包括:第一方面实施例任一项所述的时钟同步电路。

18、本申请的上述技术方案具有如下有益的技术效果:

19、本申请实施例电路通过利用降频模块和时序匹配调整模块将时钟扇出模块扇出生成的两路时钟信号建立预设时序约束关系,这样再不需要将时基信号倍频得特别高的情况下,就可以实现在各个子板卡接收端的时钟同步。不需要逻辑器件的大规模电路设计,不需要特殊的复杂的时序编程,物料成本和人力成本较低。

技术特征:

1.一种时钟同步电路,其特征在于,包括:

2.根据权利要求1所述的时钟同步电路,其特征在于,所述第一时钟信号的频率和所述第二时钟信号的频率相同,所述第一时钟信号和所述第二时钟信号的相位差恒定;

3.根据权利要求1或2所述的时钟同步电路,其特征在于,还包括:

4.根据权利要求3所述的时钟同步电路,其特征在于,所述目标板卡包括接收芯片;

5.根据权利要求4所述的时钟同步电路,其特征在于,所述目标板卡还包括整数计数器和小数计数器;所述整数计数器和所述小数计数器分别与所述接收芯片连接,所述接收芯片具体用于在接收到所述同步触发信号的上升沿,在整数计数器上增加第一阈值,并清零小数计数器;所述接收芯片具体还用于在接收到所述时基信号的上升沿,在小数计数器上增加第二阈值,直到再次接收到所述同步触发信号的上升沿,清零小数计数器。

6.根据权利要求3所述的时钟同步电路,其特征在于,所述第一驱动模块与所述目标板卡之间的走线,和所述第二驱动模块与所述目标板卡之间的走线等长。

7.根据权利要求3所述的时钟同步电路,其特征在于,所述目标板卡为多个;

8.根据权利要求3所述的时钟同步电路,其特征在于,所述第一驱动模块与所述第二驱动模块均为低偏斜缓冲器,所述第一驱动模块的时钟偏移与所述第二驱动模块的时钟偏移相同。

9.根据权利要求1或2所述的时钟同步电路,其特征在于,所述时钟扇出模块为时钟扇出缓冲器,所述降频模块为分频器,所述时序匹配调整模块为延迟补偿器。

10.一种测试机,其特征在于,包括:权利要求1-9任一项所述的时钟同步电路。

技术总结

本申请公开了一种时钟同步电路及测试机,其中,时钟同步电路包括:时钟扇出模块,用于将时基时钟信号进行扇出,形成第一时钟信号和第二时钟信号;降频模块,与时钟扇出模块连接,用于将第一时钟信号进行降频处理,形成同步触发信号;时序匹配调整模块,与时钟扇出模块连接,用于对第二时钟信号进行时序匹配调整,形成与同步触发信号具有预设时序约束关系的时基信号。该电路利用降频模块和时序匹配调整模块将时钟扇出模块扇出生成的两路时钟信号建立预设时序约束关系,这样再不需要将时基信号倍频得特别高的情况下,就可以实现在各个子板卡接收端的时钟同步。不需要逻辑器件的大规模电路设计,不需要特殊的复杂的时序编程,极大降低物料成本和人力成本。

技术研发人员:黄辉蓝

受保护的技术使用者:杭州长川科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!