用于将比原生支持的数据宽度更宽的数据原子地存储到存储器的处理器、方法、系统和指令与流程

本文描述的实施例一般涉及处理器。具体地,本文描述的实施例一般涉及保证处理器中的存储原子性。

背景技术:

1、许多处理器具有单指令多数据(simd)架构。在simd架构中,打包数据指令、矢量指令或simd指令可以同时或并行地在多个数据元素或多个数据元素对上进行操作。处理器可以具有响应于打包数据指令的并行执行硬件,以同时或并行地执行多个操作。

2、可以将多个数据元素打包在一个寄存器内作为打包数据或矢量数据。在打包数据中,其它存储位置或寄存器的位可以逻辑地划分成数据元素序列。例如,128位宽打包数据寄存器可以具有两个64位宽数据元素、四个32位数据元素、八个16位数据元素或十六个8位数据元素。数据元素的每个可以表示单独的独立数据片(例如,像素颜色、复数的分量等),可以单独地和/或独立于其余的数据元素来对其操作。

技术实现思路

技术特征:

1.一种处理器,包括:

2.如权利要求1所述的处理器,其中所述状态信息指示所述第一数据是否已被装置接受。

3.如权利要求1所述的处理器,其中所述状态信息将基于与到所述目的地存储器位置的所述第一数据的所述原子存储相关的响应的接收来存储。

4.如权利要求1所述的处理器,其中所述目的地存储器位置对应于针对装置的工作提交队列。

5.如权利要求4所述的处理器,其中所述工作提交队列是共享工作提交队列。

6.如权利要求4所述的处理器,其中所述工作提交队列是内存映射输入输出(mmio)共享工作队列寄存器。

7.如权利要求4所述的处理器,其中所述第一数据用于将工作分配给所述装置。

8.如权利要求4所述的处理器,其中所述装置是存储控制器。

9.如权利要求1所述的处理器,其中所述指令是用于向装置提交工作的工作提交指令。

10.如权利要求1所述的处理器,其中所述目的地存储器位置在内存映射输入输出(mmio)范围内。

11.如权利要求1所述的处理器,其中所述第一数据绕过所述多个高速缓冲存储器,而不管所述目的地存储器位置的存储器类型如何。

12.如权利要求1所述的处理器,其中所述原子存储的成功完成要求所述目的地存储器位置是64字节对齐的。

13.如权利要求1所述的处理器,其中所述执行电路模块用于防止比所述指令更年轻的存储数据与所述第一数据合并。

14.如权利要求1所述的处理器,其中用于提供所述信息以寻址所述目的地存储器位置的所述指令用于指定通用寄存器,所述通用寄存器具有要与来自段寄存器的地址信息进行组合的地址信息。

15.如权利要求1所述的处理器,其中所述第一数据为512位。

16.如权利要求1所述的处理器,其中所述第一数据为256位。

17.一种处理器,包括:

18.如权利要求17所述的处理器,其中所述mmio工作提交队列是共享的mmio工作提交队列。

19.如权利要求17所述的处理器,其中所述第一数据绕过所述多个高速缓冲存储器,而不管所述mmio工作提交队列中的所述位置的存储器类型如何。

20.如权利要求17所述的处理器,其中所述原子存储的成功完成要求所述mmio工作提交队列中的所述位置是64字节对齐的。

21.如权利要求17所述的处理器,其中所述执行电路模块用于防止比所述指令更年轻的存储数据与所述第一数据合并。

22.如权利要求17所述的处理器,其中所述装置是加速器装置。

23.如权利要求17所述的处理器,还包括与所述执行电路模块耦合的状态寄存器,其中状态信息将被存储在所述状态寄存器的一个位中,所述状态信息指示所述第一数据是否已被存储到所述mmio工作提交队列中的所述位置。

24.如权利要求23所述的处理器,其中所述状态信息指示所述第一数据是否已被所述装置接受。

25.如权利要求23所述的处理器,其中所述装置用于将所述状态信息存储在所述状态寄存器的所述位中。

26.如权利要求17所述的处理器,其中用于提供所述信息以寻址所述mmio工作提交队列中的所述位置的指令用于指定通用寄存器,所述通用寄存器具有要与来自段寄存器的地址信息进行组合的地址信息。

27.如权利要求17所述的处理器,其中所述第一数据为512位。

28.如权利要求17所述的处理器,其中所述第一数据为256位。

29.如权利要求17所述的处理器,其中所述装置是存储控制器。

30.一种设备,包括:

31.如权利要求30所述的设备,其中所述状态信息指示第一数据是否已经被加速器装置接受。

32.如权利要求30所述的设备,其中所述状态信息将基于与到所述目的地存储器位置的所述第一数据的所述原子存储相关的响应的接收来存储。

33.如权利要求30所述的设备,其中所述目的地存储器位置对应于针对所述加速器装置的内存映射输入输出(mmio)共享工作提交队列,并且其中所述第一数据用于将工作分配给所述加速器装置。

34.如权利要求30所述的设备,其中所述第一数据绕过所述多个高速缓冲存储器,而不管所述目的地存储器位置的存储器类型如何,其中所述原子存储的成功完成要求所述目的地存储器位置是64字节对齐的,并且其中所述执行电路模块用于防止比所述指令更年轻的存储数据与所述第一数据合并。

35.一种处理器,包括:

36.如权利要求35所述的处理器,其中所述原子存储到存储器指令是用于将工作提交给装置的指令,并且其中所述状态信息指示到所述存储器位置的所述512位数据的所述存储已经被存储在所述装置的工作队列中。

37.如权利要35求所述的处理器,其中所述状态信息基于接收到的与到所述存储器位置的所述512位数据的所述原子存储相关的响应。

38.如权利要求35所述的处理器,其中为了执行所述解码的原子存储到存储器指令,所述执行电路模块用于:

39.如权利要求35所述的处理器,其中所述原子存储的成功完成要求所述存储器位置是64字节对齐的,其中所述存储器位置的存储器类型是不可高速缓存的存储器类型,并且其中所述执行电路模块用于经由不可高速缓存的存储操作将所述512位数据原子地存储到所述存储器位置。

40.一种系统,包括:

41.如权利要求40所述的系统,其中所述原子存储到存储器指令是用于将工作提交给装置的指令,并且其中所述状态信息指示到所述存储器位置的所述512位数据的所述存储已经被存储在所述装置的工作队列中。

42.如权利要求40所述的系统,其中所述原子存储的成功完成要求所述存储器位置是64字节对齐的,其中所述存储器位置的存储器类型是不可高速缓存的存储器类型,并且其中所述执行电路模块用于经由不可高速缓存的存储操作将所述512位数据原子地存储到所述存储器位置。

43.一种处理器,所述处理器包括:

44.如权利要求43所述的处理器,其中所述执行单元包括分级缓冲器,并且其中所述执行单元响应于所述原子存储到存储器指令而要:

45.一种处理器,所述处理器包括:

46.如权利要求45所述的处理器,其中所述执行单元包括分级缓冲器,并且其中所述执行单元响应于所述原子存储到存储器指令而要:

47.一种计算机系统,所述计算机系统包括:

48.如权利要求47所述的计算机系统,其中所述处理器包括分级缓冲器和写组合缓冲器,并且其中所述处理器响应于所述原子存储到存储器指令,而要:

49.一种处理器,所述处理器包括:

50.一种由处理器执行的方法,所述方法包括:

51.如权利要求50所述的方法,其中所述原子地存储包括将具有至少512位宽度的所指示的数据原子地存储到所述存储器位置,并且其中所述最宽数据寄存器的宽度不大于256位。

52.如权利要求50所述的方法,其中所述原子地存储还包括,响应于所述原子存储到存储器指令:

技术总结

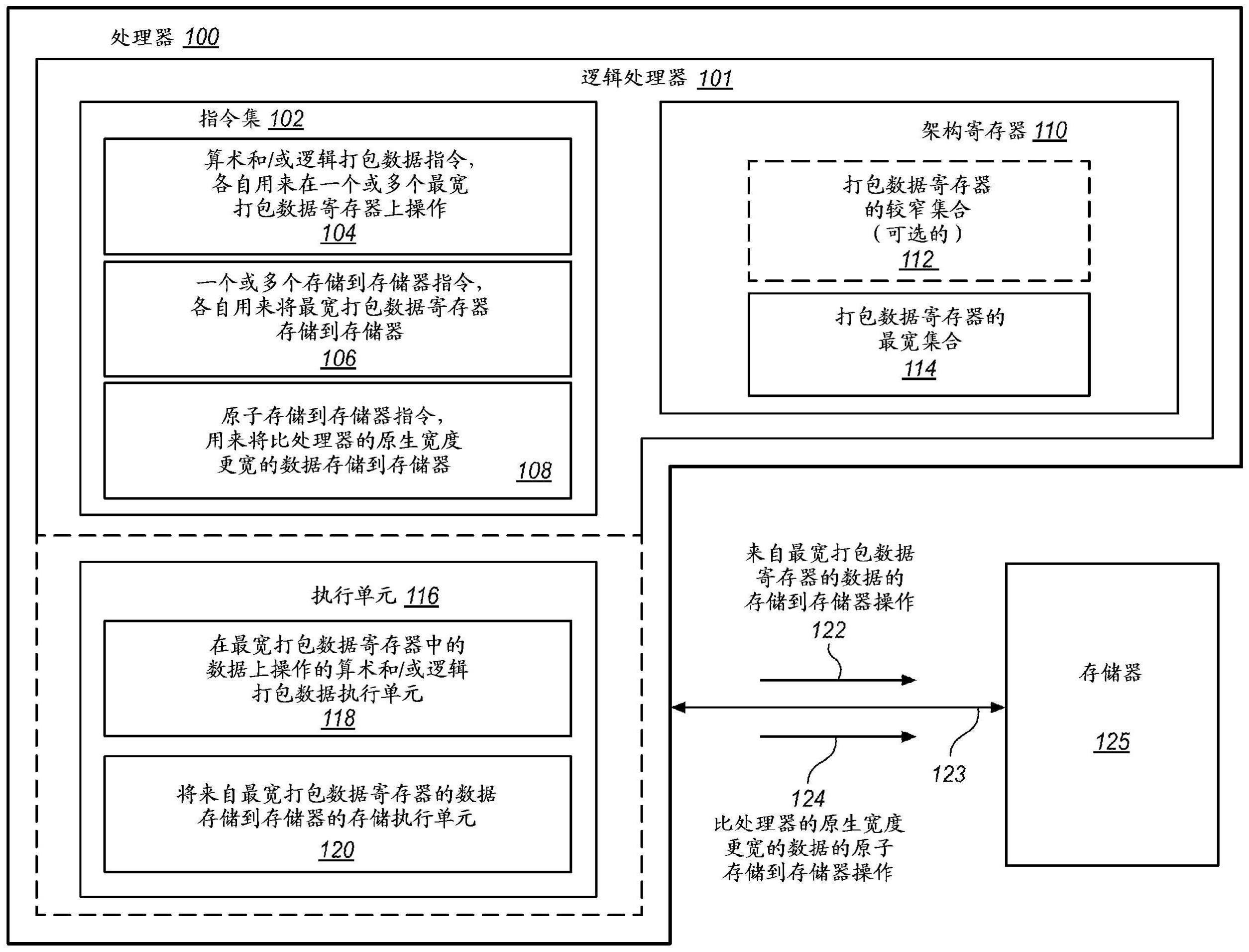

处理器包括对应于给定逻辑处理器的数据寄存器的最宽集合。最宽集合的数据寄存器的每个具有以位计的第一宽度。对应于给定逻辑处理器的解码单元要解码指定最宽集合的数据寄存器的指令,并且要解码原子存储到存储器指令。原子存储到存储器指令要指示要具有以位计的第二宽度的数据,所述以位计的第二宽度比以位计的第一宽度更宽。原子存储到存储器指令要指示与存储器位置关联的存储器地址信息。执行单元与解码单元耦合。执行单元响应于原子存储到存储器指令,要将指示的数据原子地存储到存储器位置。

技术研发人员:V.尚布霍格,S.J.罗宾逊,C.D.布赖恩特,J.W.布兰特

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!