Flash读写系统的制作方法

本发明涉及数据存储,尤其涉及一种flash读写系统。

背景技术:

1、flash闪存是属于内存器件的一种,是一种非易失性(non-volatile)内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

2、现有的flash数据读取过程中,cpu(central processing unit,中央处理器)需要多个周期等待才能进行数据读取,flash数据读取效率较低,且在cpu读取数据过程中需要系统频率达到要求时才能将flash数据安全读出,系统效率较低。

技术实现思路

1、本发明的目的之一在于提供一种flash读写系统,以解决现有技术中cpu读取flash数据需要较长的等待时间,以及读取效率较低的技术问题。

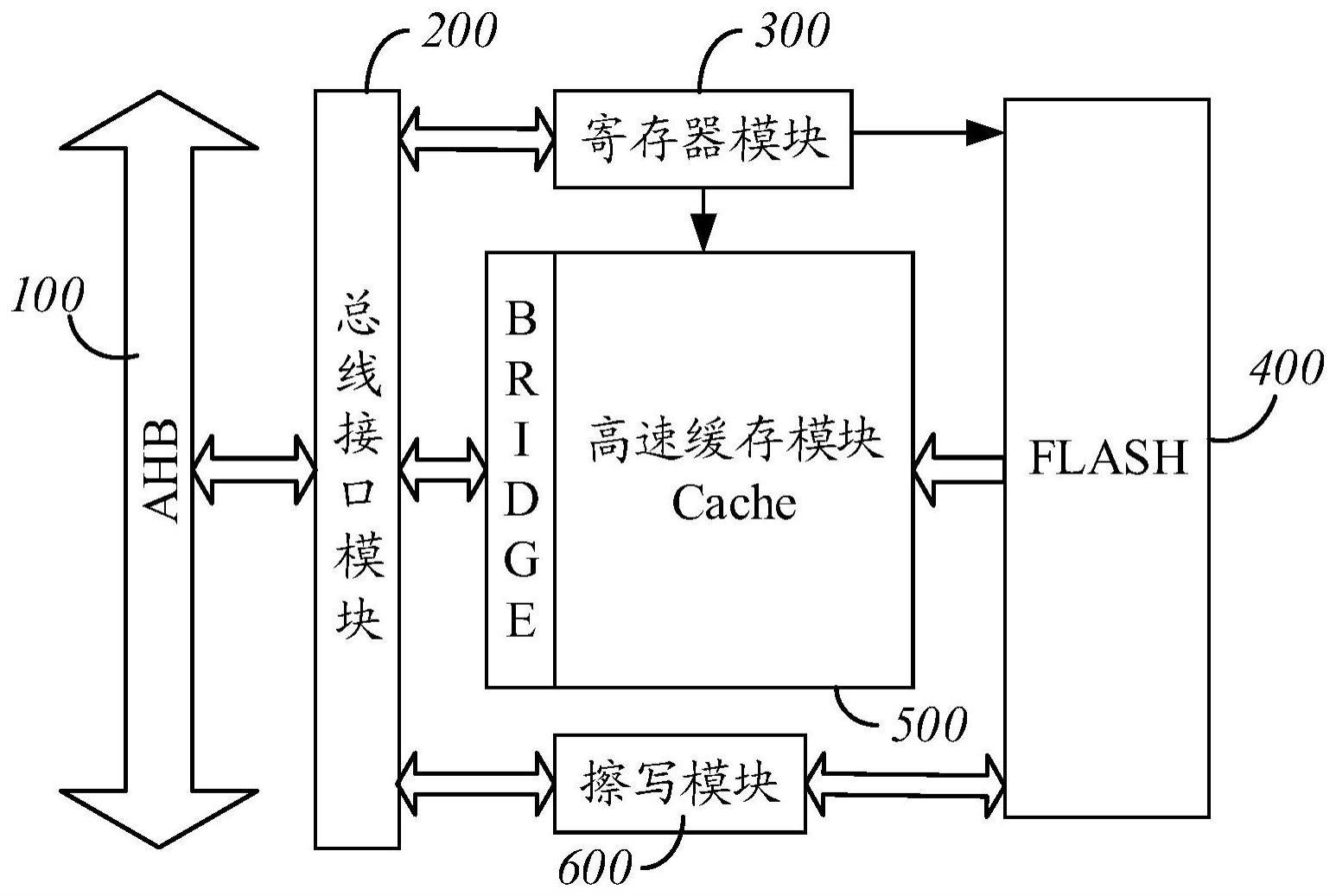

2、为实现上述发明目的之一,本发明一实施方式提供一种flash读写系统,用于读取flash模块内存储的数据,其特征在于,所述flash读写系统包括:ahb总线,以及分别与所述ahb总线和所述flash模块电性连接的高速缓存模块,所述高速缓存模块设置于ahb总线与flash模块之间;

3、所述高速缓存模块配置为,存储所述flash模块内的数据,并在第一状态下接受cpu对flash数据的直接调用,完成cpu对flash模块的读写配置。

4、作为本发明一实施方式的进一步改进,所述flash读写系统配置为,在第二状态下控制所述cpu直接对所述flash模块执行读写配置。

5、作为本发明一实施方式的进一步改进,所述flash读写系统还包括总线接口模块,所述ahb总线通过所述总线接口模块与所述高速缓存模块电性连接;所述总线接口模块配置为,根据ahb总线地址,判断读写所述flash模块或所述高速缓存模块。

6、作为本发明一实施方式的进一步改进,所述flash读写系统还包括寄存器模块,所述寄存器模块分别与所述ahb总线、所述高速缓存模块与flash模块电性连接,所述寄存器模块用于存储所述cpu运算的数据。

7、作为本发明一实施方式的进一步改进,所述flash读写系统还包括擦写模块,所述擦写模块分别与所述flash模块、ahb总线电性连接,所述擦写模块用于处理器与flash数据的初始化,并建立内存空间的映射。

8、作为本发明一实施方式的进一步改进,所述寄存器模块用于控制flash模块的擦写请求,并通过擦写模块对所述flash数据进行擦写。

9、作为本发明一实施方式的进一步改进,所述寄存器模块包括时序寄存器、控制寄存器与通用寄存器中的一种或两种以上的组合;其中,所述时序寄存器用于实现所述flash在不同频率下的时序一致性,所述通用寄存器用于发起flash擦写请求和/或控制所述flash模块的状态。

10、作为本发明一实施方式的进一步改进,所述cpu包括cortex m0+内核,且搭载amba2.0ahb总线协议完成与所述ahb总线的通信。

11、作为本发明一实施方式的进一步改进,所述flash系统还包括拓展接口模块,所述拓展接口模块内置有axi-bus协议,所述cpu通过axi-bus协议访问所述高速缓存模块内的flash数据。

12、作为本发明一实施方式的进一步改进,所述ahb总线内置有ahb总线协议,所述ahb总线协议与所述axi-bus协议能够相互转换。

13、与现有技术相比,本发明提供的flash读取缓存系统通过在ahb总线与flash模块之间设置高速缓存模块,使得cpu能够通过调用高速缓存模块内的flash数据以完成对flash模块的读写配置,无需等待周期,减少对flash模块的直接的访问,降低系统功耗,能够提高flash数据的读取速率,避免重复存取数据,减少了cpu的等待时间,提高系统效率。

技术特征:

1.一种flash读写系统,用于读取flash模块内存储的数据,其特征在于,所述flash读写系统包括:ahb总线,以及分别与所述ahb总线和所述flash模块电性连接的高速缓存模块,所述高速缓存模块设置于ahb总线与flash模块之间;

2.根据权利要求1所述的flash读写系统,其特征在于,所述flash读写系统配置为,在第二状态下控制所述cpu直接对所述flash模块执行读写配置。

3.根据权利要求2所述的flash读写系统,其特征在于,所述flash读写系统还包括总线接口模块,所述ahb总线通过所述总线接口模块与所述高速缓存模块电性连接;所述总线接口模块配置为,根据ahb总线地址,判断读写所述flash模块或所述高速缓存模块。

4.根据权利要求1所述的flash读写系统,其特征在于,所述flash读写系统还包括寄存器模块,所述寄存器模块分别与所述ahb总线、所述高速缓存模块与flash模块电性连接,所述寄存器模块用于存储所述cpu运算的数据。

5.根据权利要求4所述的flash读写系统,其特征在于,所述flash读写系统还包括擦写模块,所述擦写模块分别与所述flash模块、ahb总线电性连接,所述擦写模块用于处理器与flash数据的初始化,并建立内存空间的映射。

6.根据权利要求5所述的flash读写系统,其特征在于,所述寄存器模块用于控制flash模块的擦写请求,并通过擦写模块对所述flash数据进行擦写。

7.根据权利要求4所述的flash读写系统,其特征在于,所述寄存器模块包括时序寄存器、控制寄存器与通用寄存器中的一种或两种以上的组合;其中,所述时序寄存器用于实现所述flash在不同频率下的时序一致性,所述通用寄存器用于发起flash擦写请求和/或控制所述flash模块的状态。

8.根据权利要求1所述的flash读写系统,其特征在于,所述cpu包括cortex m0+内核,且搭载amba 2.0ahb总线协议完成与所述ahb总线的通信。

9.根据权利要求1所述的flash读写系统,其特征在于,所述flash系统还包括拓展接口模块,所述拓展接口模块内置有axi-bus协议,所述cpu通过axi-bus协议访问所述高速缓存模块内的flash数据。

10.根据权利要求9所述的flash读写系统,其特征在于,所述ahb总线内置有ahb总线协议,所述ahb总线协议与所述axi-bus协议能够相互转换。

技术总结

本发明揭示了一种Flash读取缓存系统,所述Flash读取缓存系统包括:AHB总线,以及分别与所述AHB总线和所述Flash模块电性连接的高速缓存模块,所述高速缓存模块设置于AHB总线与Flash模块之间;所述高速缓存模块配置为,存储所述Flash模块内的数据,并在第一状态下接受CPU对Flash数据的直接调用,完成CPU对Flash模块的读写配置,本发明提供的Flash读取缓存系统通过在AHB总线与Flash模块之间设置高速缓存模块,通过CPU选择性调取Flash模块内的数据或直接调用高速缓存模块内的Flash数据,无需等待周期,减少Flash的访问,降低系统功耗,能够提高Flash数据的读取速率,避免重复存取数据,减少CPU等待时间,提高系统效率。

技术研发人员:陈家敏,石国城,张季润,岳海群,董厚希,杨维,王荣华,王成

受保护的技术使用者:芯弦半导体(苏州)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!