本文中公开的发明概念的实施例大体上针对重定时器,且更特定来说,针对具有带内低延时切换的pcie重定时器。

背景技术:

1、在外围组件接口快速(pcie)总线通过连接器传递到缆线或印刷电路板(pcb)(即,中平面或后平面布局)的情况下,互连件及pcb/缆线变化造成不连续,且那些不连续产生反应且增加使pcie信号降级的符号间干扰。在无有源电路系统的情况下,接收器可能无法读取经降级信号。pcie基本规格允许串联实施高达两个重定时器(再生pcie信号的有源电路系统)以扩展物理总线的范围。

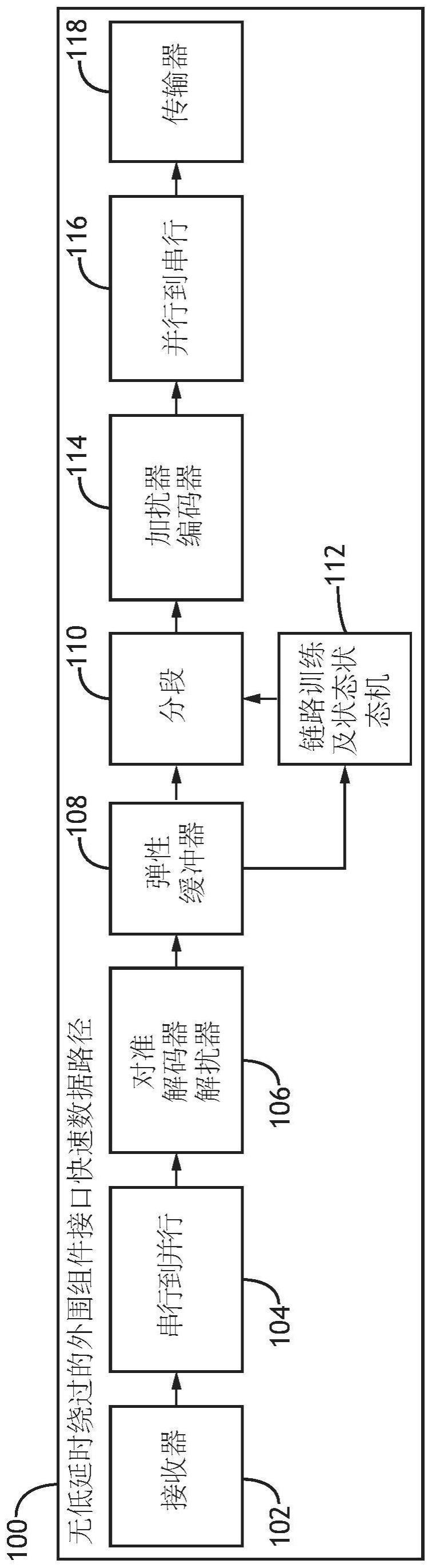

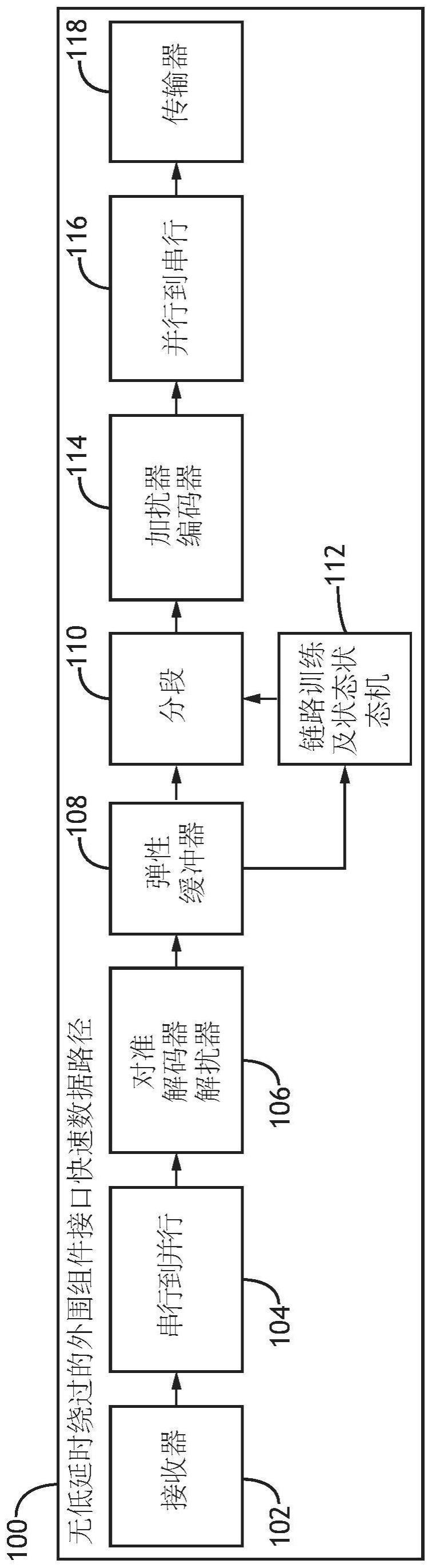

2、重定时器需要具有完整的pcie物理层堆叠,以在链路训练期间完全参与并操纵有序集中的位。周游物理层堆叠的传入分组在遍历传输器侧编码、加扰及并行到串行逻辑之前首先遍历接收器侧串行到并行逻辑、解扰器、解码、弹性缓冲器、对准解码器抗扭斜缓冲器及其它接收器逻辑。针对通过单个重定时器在60到100纳秒范围内的往返延时,现存pcie重定时器针对在每一方向上流动通过重定时器的业务具有在30到50纳秒范围内的单向延时。在具有两个重定时器的系统中,往返延时可多达120到200纳秒。一些应用看到由于延时增加而致的性能降级。

技术实现思路

1、一方面,本文中公开的发明概念的实施例针对一种具有具低延时模式进入及退出值的只读供应商寄存器的pcie重定时器。带内低延时切换逻辑监测弹性缓冲器的输出是否有供应商寄存器的读取命令,且当此类读取命令被接收时,读取对应地址且基于读取操作的回传值使多路复用器在链路训练数据路径与低延时数据路径之间切换。读取命令且因此数据路径切换的控制完全在带内处置。

2、另一方面,所述读取操作的回传值指示模式切换到根联合体的成功或失败。

3、应理解,前述一般描述及以下详细描述仅是示范性及解释性的,且不应限制权利要求的范围。并入本说明书中且构成本说明书的一部分的附图说明本文中公开的发明概念的示范性实施例且与一般描述一起用于解释原理。

技术特征:1.一种pcie重定时器,其包括:

2.根据权利要求1所述的pcie重定时器,其中所述切换逻辑进一步包括:

3.根据权利要求1所述的pcie重定时器,其中所述处理逻辑进一步经配置以:

4.根据权利要求3所述的pcie重定时器,其中所述接收到的信号包括通道裕度读取命令。

5.根据权利要求1所述的pcie重定时器,其中所述处理逻辑进一步经配置以基于将所述信号施加到所述多路复用器的成功或失败将回传代码回传到根联合体。

6.根据权利要求1所述的pcie重定时器,其中所述处理逻辑进一步经配置以:

7.根据权利要求1所述的pcie重定时器,其中到所述多路复用器的所述信号包括当读取对应于供应商地址信号的供应商地址时回传的读取值。

8.一种pcie装置,其包括:

9.根据权利要求8所述的pcie装置,其中所述切换逻辑进一步包括:

10.根据权利要求8所述的pcie装置,其中所述低延时模式进入/退出信号包括通道裕度读取命令。

11.根据权利要求8所述的pcie装置,其中所述处理逻辑进一步经配置以基于将所述信号施加到所述多路复用器的成功或失败将回传代码回传到根联合体。

12.根据权利要求8所述的pcie装置,其中所述处理逻辑进一步经配置以:

13.根据权利要求8所述的pcie装置,其中到所述多路复用器的所述信号包括当读取对应于供应商地址信号的供应商地址时回传的读取值。

14.一种系统,其包括:

15.根据权利要求14所述的系统,其中所述切换逻辑进一步包括:

16.根据权利要求14所述的系统,其中所述处理逻辑进一步经配置以:

17.根据权利要求16所述的系统,其中所述低延时模式进入信号包括通道裕度读取命令。

18.根据权利要求14所述的系统,其中所述处理逻辑进一步经配置以基于将所述信号施加到所述多路复用器的成功或失败将回传代码回传到根联合体。

19.根据权利要求14所述的系统,其中所述处理逻辑进一步经配置以:

20.根据权利要求14所述的系统,其中到所述多路复用器的所述信号包括当读取对应于所述读取信号的所述寄存器地址时回传的读取值。

技术总结本公开涉及PCIe应用中低延时数据路径的自主进入及退出。PCIe重定时器包含具有低延时模式进入及退出值的只读供应商寄存器。带内低延时切换逻辑监测弹性缓冲器的输出是否有供应商寄存器的读取命令,且当此类读取命令被接收时,读取对应地址且基于读取操作的回传值使多路复用器在链路训练数据路径与低延时数据路径之间切换。读取命令且因此数据路径切换的控制完全在带内处置。所述读取操作的回传值指示模式切换到根联合体的成功或失败。

技术研发人员:J·R·多斯特

受保护的技术使用者:安华高科技股份有限公司

技术研发日:技术公布日:2024/1/15