一种系统故障时BIOS自动复位的电路及其使用方法与流程

本发明属于bios复位,尤其涉及一种系统故障时bios自动复位的电路及其使用方法。

背景技术:

1、现有的计算机中,按下主板的电源按键后,主板会进行开机。但bios有损坏的概率,bios损坏会导致主板不能正常开机,这时最好的解决办法就是对bios进行复位。

2、若需要对bios进行复位使主板正常开机,需要拆开机箱后移除电源(s0电源和s5电源),然后抠出rtc电池,使主板断电,coms断电重置,bios回到初始状态,完成bios的复位,最后对主板重新进行开机。

3、但是在一些场合,例如主板应用在电视牆、提款机等场所中,若bios发生故障了,是不能进行拆开机箱以及移除电源(s0电源和s5电源)、抠出rtc电池等操作的,需要有维修人员到场对bios进行复位,较为费时。

技术实现思路

1、本发明的目的在于提供一种系统故障时bios自动复位的电路及其使用方法,旨在解决由于现有技术无法提供一种系统故障时bios自动复位的电路及其使用方法,导致对bios进行复位时需要断电并拆开机箱移除电源和电池的问题。

2、一方面,本发明提供了一种系统故障时bios自动复位的电路,包括:

3、主板,设置有s0电源、s5电源、rtc电源、gnd接口;

4、第一控制电路,与s0电源连接且可控制s0电源的通断;

5、第二控制电路,与s5电源连接且可控制s5电源的通断;

6、第三控制电路,与rtc电源连接且可控制rtc电源的通断;

7、嵌入式处理器,设置在主板上,具有对应与第一控制电路、第二控制电路、第三控制电路连接的第一io引脚、第二io引脚、第三io引脚。

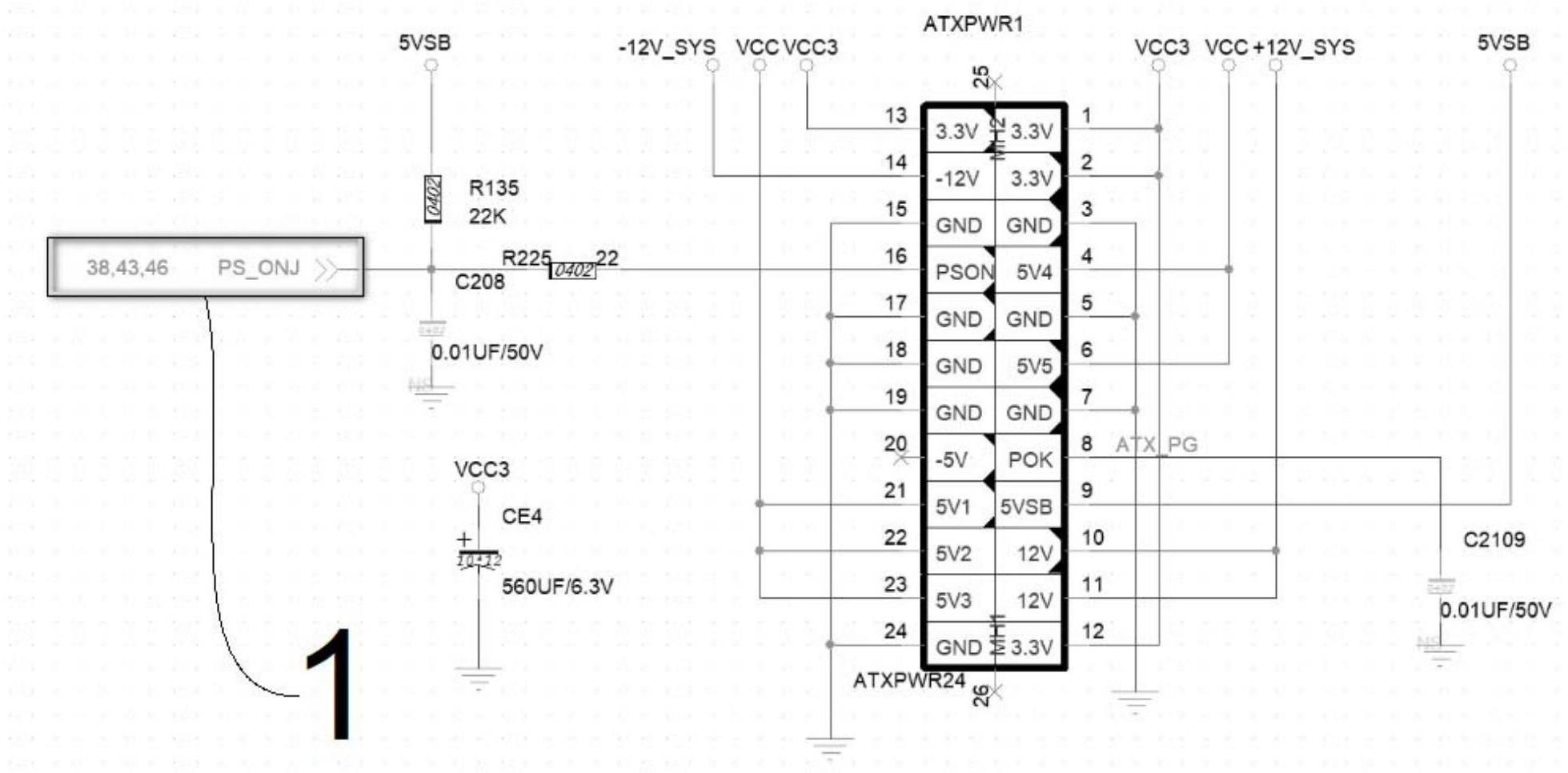

8、优选的,所述s0电源具有可控制s0电源通断的pson引脚,所述第一控制电路包括5vsb接口、上拉电阻r135,所述pson引脚通过上拉电阻r135与5vsb接口连接,所述嵌入式处理器的第一io引脚与pson引脚连接。

9、优选的,所述s5电源具有可控制s5电源通断的en引脚,所述第二控制电路包括nmos管q53、nmos管q51、上拉电阻r162、下拉电阻r138、5vdual接口,所述nmos管q53的g极、d极、s极对应与第二io引脚、nmos管q51的g极、gnd接口连接,所述nmos管q51的d极、s极对应与en引脚、gnd接口连接,所述en引脚通过上拉电阻r162与5vdual接口连接,所述en引脚通过下拉电阻r138与gnd接口连接。

10、优选的,所述第二控制电路还包括上拉电阻r663、下拉电阻r2343,所述上拉电阻r663、上拉电阻r162的第一端均与5vdual接口连接,所述上拉电阻r663、上拉电阻r162的第二端对应与nmos管q51的g极、en引脚连接,所述下拉电阻r2343的两端对应与nmos管q51的g极、gnd接口连接,所述下拉电阻r138的两端对应与en引脚、gnd接口连接。

11、优选的,所述rtc电源的负极与gnd接口连接,所述第三控制电路包括nmos管q16、与rtc电源的正极耦接的vccrtc接口,所述nmos管q16的g极、d极、s极对应与第三io引脚、vccrtc接口、gnd接口连接。

12、优选的,还包括rsmrst信号电路,所述主板还包括有pch芯片,所述pch芯片具有rsmrst引脚,所述rsmrst信号电路包括nmos管q16、nmos管q5、上拉电阻r19、3d3vsb接口,所述nmos管q16的g极、s极对应与第二io引脚、gnd接口连接,所述nmos管q16的d极与nmos管q5的管g极耦接,所述nmos管q5的d极、s极对应与rsmrst引脚、gnd接口连接,所述nmos管q5的d极通过上拉电阻r19与rsmrst引脚连接。

13、优选的,所述rsmrst信号电路还包括npn型三极管q9、上拉电阻r40、下拉电阻r46、上拉电阻r37、下拉电阻r97、5vsb接口,所述上拉电阻r40和下拉电阻r46的第一端对应与上拉电阻r40、下拉电阻r46连接,所述上拉电阻r40和下拉电阻r46的第二端均与npn型三极管q9的b极连接,所述npn型三极管q9的c极、e极对应与nmos管q5的管g极、nmos管q16的管d极连接,所述nmos管q16的d极通过npn型三极管q9与nmos管q5的管g极耦接,所述npn型三极管q9的c极通过上拉电阻r37与5vsb接口连接,所述npn型三极管q9的e极通过下拉电阻r97与gnd接口连接。

14、优选的,所述主板上还设置有电源按键,所述电源按键通过主板与嵌入式处理器电连接。

15、另一方面,本发明还提供了一种系统故障时bios自动复位的电路的使用方法,所述方法包括如下步骤:

16、嵌入式处理器依次向第一io引脚发出关闭s0电源的信号、向第二io引脚发出关闭s5电源的信号、向第三io引脚发出关闭rtc电源的信号,等待5s后,嵌入式处理器依次向第三io引脚发出打开rtc电源的信号、向第二io引脚发出打开s5电源的信号、向第一io引脚发出打开s0电源的信号。

17、另一方面,本发明还提供了一种系统故障时bios自动复位的电路的使用方法,所述方法包括如下步骤:

18、按下电源按键,电源按键向嵌入式处理器发送指令;

19、嵌入式处理器判断bios是否损坏:如是,嵌入式处理器依次向第一io引脚发出关闭s0电源的信号、向第二io引脚发出关闭s5电源的信号、向第三io引脚发出关闭rtc电源的信号,等待5s后,嵌入式处理器依次向第三io引脚发出打开rtc电源的信号、向第二io引脚发出打开s5电源的信号、向第一io引脚发出打开s0电源的信号;

20、反之,嵌入式处理器不执行操作。

21、本发明的有益效果在于:区别于现有技术,本发明在主板上设置有第一控制电路、第二控制电路、第三控制电路以及嵌入式处理器,嵌入式处理器能通过分别控制第一控制电路、第二控制电路、第三控制电路进而控制s0电源、s5电源、rtc电源的通断,需要对bios进行复位时,可通过嵌入式处理器依次控制第一控制电路、第二控制电路、第三控制电路,进而对s0电源、s5电源、rtc电源进行断电,使coms断电重置,bios回到初始状态完成bios的复位,无需拆开机箱进行操作,节省维修时间和维修成本。

技术特征:

1.一种系统故障时bios自动复位的电路,包括:

2.如权利要求1所述的系统故障时bios自动复位的电路,其特征在于:所述s0电源具有可控制s0电源通断的pson引脚,所述第一控制电路包括5vsb接口、上拉电阻r135,所述pson引脚通过上拉电阻r135与5vsb接口连接,所述嵌入式处理器的第一io引脚与pson引脚连接。

3.如权利要求1所述的系统故障时bios自动复位的电路,其特征在于:所述s5电源具有可控制s5电源通断的en引脚,所述第二控制电路包括nmos管q53、nmos管q51、上拉电阻r162、下拉电阻r138、5vdual接口,所述nmos管q53的g极、d极、s极对应与第二io引脚、nmos管q51的g极、gnd接口连接,所述nmos管q51的d极、s极对应与en引脚、gnd接口连接,所述en引脚通过上拉电阻r162与5vdual接口连接,所述en引脚通过下拉电阻r138与gnd接口连接。

4.如权利要求3所述的系统故障时bios自动复位的电路,其特征在于:所述第二控制电路还包括上拉电阻r663、下拉电阻r2343,所述上拉电阻r663、上拉电阻r162的第一端均与5vdual接口连接,所述上拉电阻r663、上拉电阻r162的第二端对应与nmos管q51的g极、en引脚连接,所述下拉电阻r2343的两端对应与nmos管q51的g极、gnd接口连接,所述下拉电阻r138的两端对应与en引脚、gnd接口连接。

5.如权利要求1所述的系统故障时bios自动复位的电路,其特征在于:所述rtc电源的负极与gnd接口连接,所述第三控制电路包括nmos管q16、与rtc电源的正极耦接的vccrtc接口,所述nmos管q16的g极、d极、s极对应与第三io引脚、vccrtc接口、gnd接口连接。

6.如权利要求1所述的系统故障时bios自动复位的电路,其特征在于:还包括rsmrst信号电路,所述主板还包括有pch芯片,所述pch芯片具有rsmrst引脚,所述rsmrst信号电路包括nmos管q16、nmos管q5、上拉电阻r19、3d3vsb接口,所述nmos管q16的g极、s极对应与第二io引脚、gnd接口连接,所述nmos管q16的d极与nmos管q5的管g极耦接,所述nmos管q5的d极、s极对应与rsmrst引脚、gnd接口连接,所述nmos管q5的d极通过上拉电阻r19与rsmrst引脚连接。

7.如权利要求6所述的系统故障时bios自动复位的电路,其特征在于:所述rsmrst信号电路还包括npn型三极管q9、上拉电阻r40、下拉电阻r46、上拉电阻r37、下拉电阻r97、5vsb接口,所述上拉电阻r40和下拉电阻r46的第一端对应与上拉电阻r40、下拉电阻r46连接,所述上拉电阻r40和下拉电阻r46的第二端均与npn型三极管q9的b极连接,所述npn型三极管q9的c极、e极对应与nmos管q5的管g极、nmos管q16的管d极连接,所述nmos管q16的d极通过npn型三极管q9与nmos管q5的管g极耦接,所述npn型三极管q9的c极通过上拉电阻r37与5vsb接口连接,所述npn型三极管q9的e极通过下拉电阻r97与gnd接口连接。

8.如权利要求1所述的系统故障时bios自动复位的电路,其特征在于:所述主板上还设置有电源按键,所述电源按键通过主板与嵌入式处理器电连接。

9.一种系统故障时bios自动复位的方法,采用如权利要求1-8任一项所述的系统故障时bios自动复位的电路,其特征在于:所述方法包括如下步骤:

10.一种系统故障时bios自动复位的方法,采用如权利要求8所述的系统故障时bios自动复位的电路,其特征在于:所述方法包括如下步骤:

技术总结

本发明涉及BIOS复位技术领域,提供了一种系统故障时BIOS自动复位的电路及其使用方法,包括主板、嵌入式处理器,主板上设置有S0电源、S5电源、RTC电源、第一控制电路、第二控制电路、第三控制电路,嵌入式处理器可通过控制第一控制电路、第二控制电路、第三控制电路对应控制S0电源、S5电源、RTC电源的通断。区别于现有技术,本发明在需要对BIOS进行复位时,可通过嵌入式处理器依次控制第一控制电路、第二控制电路、第三控制电路,进而对S0电源、S5电源、RTC电源进行断电,使COMS断电重置,BIOS回到初始状态完成BIOS的复位,无需拆开机箱进行操作,节省维修时间和维修成本。

技术研发人员:康洛誠

受保护的技术使用者:深圳市智微智能科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!