芯片版图设计的接线检查方法、装置、设备及存储介质与流程

本申请涉及芯片版图设计,尤其涉及一种芯片版图设计的接线检查方法、检查装置、计算机设备以及计算机可读存储介质。

背景技术:

1、目前芯片设计的版图工程师一般会使用mentor公司的calibre物理验证工具,来执行设计规则检查(design rule check,drc)和电路规则检查(layout versusschematic,lvs)。在芯片设计中,通常情况下,电源线通过电源pad引入芯片的内部模块,地线通过地线pad引入芯片的内部模块,这样电源线和地线的连接信息会通过金属走线进入到芯片的内部模块中,而利用calibre lvs 就可以检查出器件衬底是否连接正确(如检查p型衬底是否接到了地线上、n型衬底是否接到了电源线上)。

2、在一些情况中,为了保持良好的噪声隔离及其电路性能,同一个电源pad上会连接多组不同名字的电源引脚(分别用不同电源标签区分,如avdd、dvdd),以及同一个地线pad上也会会连接多组不同名字的地线引脚(分别用不同地线标签区分,如avss、dvss),且需要使用金属电阻隔离开不同名字的电源引脚和地线引脚(如图1所示)。但是这种连接方式在calibre lvs的检查中会产生报错,因为金属电阻会阻断其电源线或地线的连接关系,即若任一电源引脚经金属电阻连接电源pad,在calibre lvs的检查中就不会得到相应电源接线正确的结果(同理,地线也是如此),因此就会产生误报。

3、而对于这种报错情况,目前的解决方式是需要版图工程师人为地进行层次化检查和肉眼检查,这无疑大大增加了人工排查的成本,尤其是当被金属电阻分割的电源引脚或地线引脚数量过多时,这样不仅大大增加了版图工程师的工作量,还有可能使得版图工程师会因排查工作过于繁多而导致有漏查的情况发生。

4、上述内容仅用于辅助理解本申请的技术方案,并不代表承认上述内容是现有技术。

技术实现思路

1、本申请的主要目的在于提供一种芯片版图设计的接线检查方法、检查装置、计算机设备以及计算机可读存储介质,旨在减少利用calibre检查芯片版图设计时产生误报的情况。

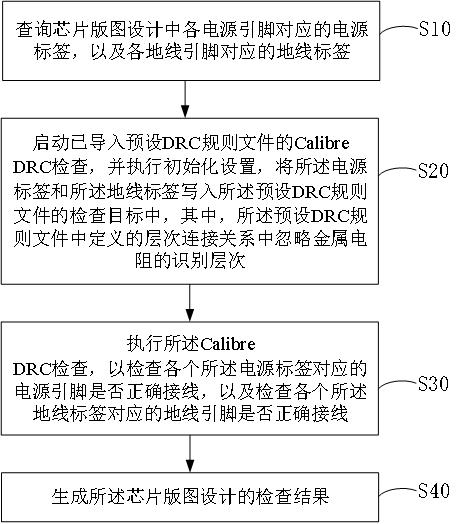

2、为实现上述目的,本申请提供一种芯片版图设计的接线检查方法,包括以下步骤:

3、查询芯片版图设计中各电源引脚对应的电源标签,以及各地线引脚对应的地线标签;

4、启动已导入预设drc规则文件的calibre drc检查,并执行初始化设置,将所述电源标签和所述地线标签写入所述预设drc规则文件的检查目标中,其中,所述预设drc规则文件中定义的层次连接关系中忽略金属电阻的识别层次;

5、执行所述calibre drc检查,以检查各个所述电源标签对应的电源引脚是否正确接线,以及检查各个所述地线标签对应的地线引脚是否正确接线;

6、生成所述芯片版图设计的检查结果。

7、可选的,所述执行所述calibre drc检查的步骤还包括:

8、查询未连接电源的n型衬底;

9、其中,所述预设drc规则文件中定义的检查规则语句包括:

10、若所述n型衬底所连接的mos管的源极或漏极未连接电源,则忽略所述n型衬底。

11、可选的,所述执行所述calibre drc检查的步骤还包括:

12、查询未连接地线的p型衬底;

13、其中,所述预设drc规则文件中定义的检查规则语句包括:

14、若所述p型衬底所连接的mos管的源极或漏极未连接地线,则忽略所述p型衬底。

15、可选的,所述生成所述芯片版图设计的检查结果的步骤还包括:

16、若所述检查结果存在报错项,输出报错信息;

17、若接收到所述报错信息的确认响应,以及检测到所述芯片版图设计更新后,返回执行所述calibre drc检查;

18、若接收到所述报错信息的取消响应,忽略所述取消响应针对的报错项。

19、可选的,所述查询芯片版图设计中各电源引脚对应的电源标签,以及各地线引脚对应的地线标签的步骤之前,还包括:

20、在所述芯片版图设计生成后,执行未导入所述预设drc规则文件的calibre drc检查。

21、为实现上述目的,本申请还提供一种检查装置,包括:

22、查询模块,用于查询芯片版图设计中各电源引脚对应的电源标签,以及各地线引脚对应的地线标签;

23、启动模块,用于启动已导入预设drc规则文件的calibre drc检查,并执行初始化设置,将所述电源标签和所述地线标签写入所述预设drc规则文件的检查目标中,其中,所述预设drc规则文件中定义的层次连接关系中忽略金属电阻的识别层次;

24、检查模块,用于执行所述calibre drc检查,以检查各个所述电源标签对应的电源引脚是否正确接线,以及检查各个所述地线标签对应的地线引脚是否正确接线;

25、生成模块,用于生成所述芯片版图设计的检查结果。

26、为实现上述目的,本申请还提供一种计算机设备,所述计算机设备包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的芯片版图设计的接线检查程序,所述芯片版图设计的接线检查程序被所述处理器执行时实现如上述芯片版图设计的接线检查方法的步骤。

27、为实现上述目的,本申请还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有芯片版图设计的接线检查程序,所述芯片版图设计的接线检查程序被处理器执行时实现如上述芯片版图设计的接线检查方法的步骤。

28、本申请提供的芯片版图设计的接线检查方法、检查装置、计算机设备以及计算机可读存储介质,通过在drc规则文件中定义的层次连接关系中忽略金属电阻的识别层次,这样calibre 基于drc规则文件对芯片版图设计进行drc检查时,就可以避免因芯片的电源引脚或地线引脚经金属电阻连接电源或地线而导致calibre产生误报,从而减少了利用calibre检查芯片版图设计时产生误报的情况的发生,进而减少了版图工程师排查calibre检查报错的工作量,不仅相应降低了人工参与的成本,而且还可以避免版图工程师会因排查工作过于繁多而导致有漏查的情况发生。

技术特征:

1.一种芯片版图设计的接线检查方法,其特征在于,包括:

2.根据权利要求1所述的芯片版图设计的接线检查方法,其特征在于,所述执行所述calibre drc检查的步骤还包括:

3.根据权利要求1所述的芯片版图设计的接线检查方法,其特征在于,所述执行所述calibre drc检查的步骤还包括:

4.根据权利要求1所述的芯片版图设计的接线检查方法,其特征在于,所述生成所述芯片版图设计的检查结果的步骤还包括:

5.根据权利要求1-4中任一项所述的芯片版图设计的接线检查方法,其特征在于,所述查询芯片版图设计中各电源引脚对应的电源标签,以及各地线引脚对应的地线标签的步骤之前,还包括:

6.一种检查装置,其特征在于,包括:

7.一种计算机设备,其特征在于,所述计算机设备包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的芯片版图设计的接线检查程序,所述芯片版图设计的接线检查程序被所述处理器执行时实现如权利要求1至5中任一项所述的芯片版图设计的接线检查方法的步骤。

8.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有芯片版图设计的接线检查程序,所述芯片版图设计的接线检查程序被处理器执行时实现如权利要求1至5中任一项所述的芯片版图设计的接线检查方法的步骤。

技术总结

本申请涉及芯片版图设计技术,公开了一种芯片版图设计的接线检查方法,包括:查询芯片版图设计中各电源引脚对应的电源标签,以及各地线引脚对应的地线标签;启动已导入预设DRC规则文件的Calibre DRC检查,并执行初始化设置,将电源标签和地线标签写入预设DRC规则文件的检查目标中,其中,预设DRC规则文件中定义的层次连接关系中忽略金属电阻的识别层次;执行Calibre DRC检查;生成芯片版图设计的检查结果。本申请还公开了一种检查装置、计算机设备和计算机可读存储介质。本申请旨在减少利用Calibre检查芯片版图设计时产生误报的情况。

技术研发人员:宋志勋,兰金保,张云福,陈建威,肖勇

受保护的技术使用者:深圳前海深蕾半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!