智能预取缓冲器和队列管理的制作方法

背景技术:

1、数据预取是计算机系统中使用的一种技术,用于从较慢的存储器中预取数据,并在计算机系统执行的过程需要数据之前将数据提供给较快的存储器或处理器。预取可以减少延迟并提高读取操作的带宽。然而,如果存储数据的存储器位置不是按顺序排列的,或者如果预取缓冲器从多个主机设备接收到试图访问存储器中完全不同的地址空间的请求,则预取操作可能会降低读取性能。

技术实现思路

1、本文档一般涉及计算系统,尤其涉及使用智能预取缓冲器预取存储器数据的技术,该智能预取缓冲器包括用于决定何时准予预取请求并执行预取操作以及何时忽略将对系统性能产生负面影响的预取请求的逻辑。

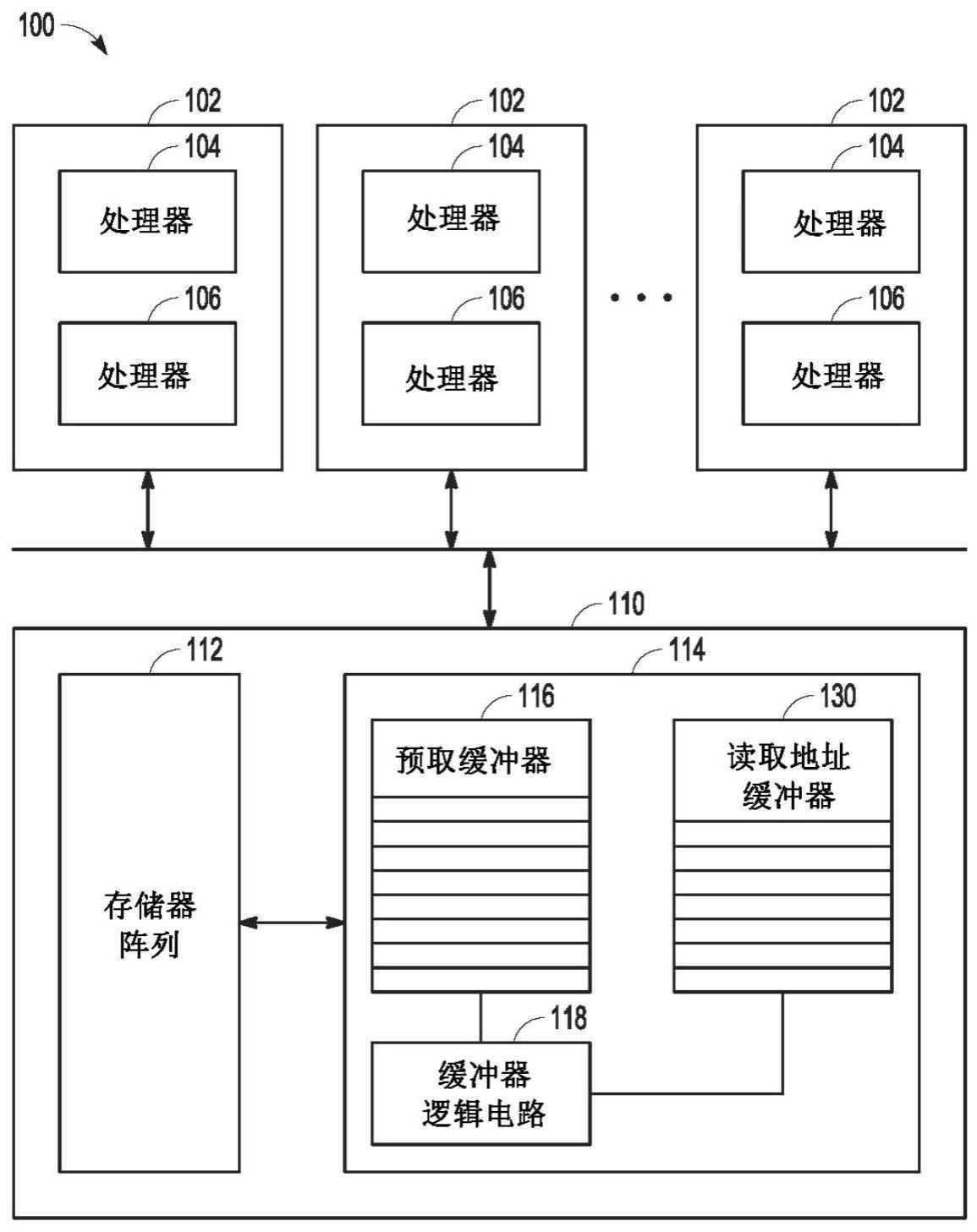

2、存储器设备的示例包括存储器阵列和可操作地耦合到存储器阵列的存储器控制器。存储器阵列包括用于存储存储器数据的存储器单元。存储器控制器包括预取缓冲器;读取地址缓冲器,包括用于存储从至少一个单独设备接收的存储器读取请求的地址的存储器寄存器和逻辑电路。所述逻辑电路被配置为当读取请求的地址是存储在所述读取地址缓冲器中的地址的连续地址时,将额外读取数据存储在所述预取缓冲器中;和当所述读取请求的地址是存储在所述读取地址缓冲器中的地址的非连续地址时,省略预取所述额外数据。

3、一种操作存储器设备的方法的例子包括:由所述存储器设备从至少一个单独的设备接收包括当前读取地址的存储器读取请求;将所述当前读取地址与存储在读取地址缓冲器中的先前读取地址进行比较;当预取逻辑电路确定当前读取地址是存储在读取地址缓冲器中的地址的连续地址时,从与当前读取地址连续的一个或多个存储器地址预取未请求的额外数据;以及当所述预取逻辑电路确定所述当前读取地址是对存储在所述读取地址缓冲器中的地址的非连续地址时,不预取所述额外数据。

4、计算系统的示例包括多个主机设备和用于从主机设备接收存储器请求的共享存储器设备。存储器设备包括存储器阵列和可操作地耦合到存储器阵列的存储器控制器。存储器阵列包括用于存储存储器数据的存储器单元。存储器控制器包括预取缓冲器、读取地址缓冲器和逻辑电路。读取地址缓冲器包括存储器寄存器,用于存储从至少一个单独设备接收的存储器读取请求的地址。所述逻辑电路被配置为当确定所述读取请求的地址是存储在读取地址缓冲器中的地址的连续地址时,将额外读取数据存储在所述预取缓冲器中;和当确定所述读取请求的地址是存储在所述读取地址缓冲器中的地址的非连续地址时,省略对所述额外读取数据的预取。

5、本部分旨在提供本专利申请的主题的概述。其并非旨在提供对本发明的排他性或详尽的解释。包括详细描述是为了提供关于本专利申请的进一步信息。

技术特征:

1.一种存储器设备,包括:

2.根据权利要求1所述的存储器设备,其中所述存储器寄存器包括在先进先出移位缓冲器中,并且所述逻辑电路被配置为将导致所述额外数据的预取的读取请求及省略预取的所述读取请求两者的读取地址存储在所述先进先出移位缓冲器中。

3.根据权利要求1所述的存储器设备,

4.根据权利要求3所述的存储器设备,其中所述逻辑电路被配置为在接收到与所述读取预取地址连续的所述读取地址时,或在对应于所述保存读取地址的读取请求的p个读取请求内未接收到与保存读取地址连续的读取地址时,刷新所述保存的读取地址,其中p是大于m的正整数。

5.根据权利要求3所述的存储器设备,其中所述读取地址缓冲器是先进先出m个寄存器移位缓冲器,并且所述逻辑电路被配置为保存所述先进先出m个寄存器移位缓冲器的最后n个存储器寄存器中的所述读取地址。

6.根据权利要求3所述的存储器设备,包括:

7.根据权利要求1所述的存储器设备,其中所述逻辑电路被配置为在所述读取地址包括在存储器块中时预取所述额外数据,所述存储器块还包括存储在所述读取地址缓冲器中的至少一个其它地址。

8.根据权利要求1所述的存储器设备,其中所述逻辑电路被配置为在所述预取请求的地址与存储于所述读取地址缓冲器中的至少一个其它地址相距预定地址偏移内时预取所述额外数据。

9.一种操作存储器设备的方法,该方法包括:

10.根据权利要求9所述的方法,包括:

11.根据权利要求9所述的方法,包括:

12.根据权利要求11所述的方法,其中当接收到与所述保存的读取地址连续的所述读取地址时,或者在与所述保存的读取地址相对应的读取请求的p个读取请求内未接收到连续读取地址时,从所述m个寄存器缓冲器中刷新所述保存的读取地址,其中p是大于m的正整数。

13.根据权利要求11所述的方法,其中所述保存存储在所述m个寄存器缓冲器的n个寄存器中的读取地址包括存储存储在先进先出m个寄存器移位缓冲器的最后n个寄存器内的读取地址。

14.根据权利要求11所述的方法,其中所述保存读取地址包括:

15.根据权利要求9所述的方法,其中不预取额外数据包括当所述读取请求的地址对应于不包括存储在所述读取地址缓冲器中的其它读取地址中的任何读取地址的存储器块时,不预取该额外数据。

16.一种计算系统,包括:

17.根据权利要求16所述的计算系统,

18.根据权利要求17所述的计算系统,其中所述逻辑电路被配置为当接收到与所述保存的读取地址连续的读取地址时,或者在与所述保存的读取地址相对应的读取请求的p个读取请求内未接收到与该保存的读取寻址连续的读取寻址时,从所述读取地址缓冲器中刷新所述保存的读取地址,其中p是大于m的正整数。

19.根据权利要求17所述的计算系统,其中所述存储器控制器的读取地址缓冲器是先进先出m个寄存器移位缓冲器,并且所述逻辑电路被配置为保存所述先进先出n个寄存器移位缓冲器的最后n个存储器寄存器中的读取地址。

20.根据权利要求17所述的计算系统,包括:

21.根据权利要求16所述的计算系统,其中所述读取地址缓冲器是先进先出移位寄存器,存储用于存储器读取请求的读取地址的记录。

技术总结

本公开涉及智能预取缓冲器和队列管理。存储器设备包括存储器阵列和可操作地耦合到存储器阵列的存储器控制器。存储器阵列包括用于存储存储器数据的存储器单元。存储器控制器包括:预取缓冲器,读取地址缓冲器,包括用于存储从至少一个单独设备接收的存储器读取请求的地址的存储器寄存器、和逻辑电路。所述逻辑电路被配置为当读取请求的地址是存储在所述读取地址缓冲器中的地址的连续地址时,将额外读取数据存储在所述预取缓冲器中,并且当所述读取请求的地址是存储在所述读取地址缓冲器中的地址的非连续地址时,省略预取所述额外数据。

技术研发人员:A·A·萨拉夫,K·坎都库瑞,T·纳特瑞严,S·斯瑞瓦斯塔瓦

受保护的技术使用者:亚德诺半导体国际无限责任公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!