一种基于FPGA的通用共轭对称矩阵求逆架构、方法及应用与流程

本发明属于现场可编程门阵列(fpga),具体地说是通过fpga复杂状态机控制逻辑设计实现cholesky矩阵求逆算法,满足任意阶共轭对称矩阵求逆,具备通用性。

背景技术:

1、近年来随着数字技术的飞速发展,通信电子产品对矩阵求逆的工程需求较为广泛。传统的矩阵求逆算法主要思想为矩阵分解,常用的矩阵求逆算法有qr分解、lu分解、cholesky分解等。其中qr分解与lu分解适用于任意可逆方阵,cholesky分解是lu分解的特殊形式,其要求矩阵为共轭对称矩阵。矩阵求逆过程中对矩阵元素的迭代消耗大量时间,矩阵求逆的运算时间与矩阵阶数呈3次方关系,因此随着矩阵阶数的增加,矩阵求逆运算时间成为系统级的技术瓶颈。

2、现场可编程门阵列(fpga)是诞生于二十世纪八十年代,其具备高并行、大吞吐、高灵活性等优势,现阶段已经广泛应用于通信电子相关领域。对于矩阵求逆复杂的迭代运算,fpga能够通过增加并行度的方式降低处理延时,同时通过分时复用计算单元的方式降低资源占用。因此fpga对矩阵求逆运算时间具备显著优势。

3、在特定场景下,例如雷达系统中的旁瓣对消、空时自适应处理等算法,需要应用矩阵求逆方法,所以怎么缩短矩阵求逆运算时间是一个有待解决的问题。

技术实现思路

1、本发明所要解决的技术问题是:

2、为了解决现有矩阵求逆运算时间太长、效率低的问题,本发明针对共轭对称矩阵的特点,提供一种基于fpga的cholesky分解矩阵求逆方法。

3、为了解决上述技术问题,本发明采用的技术方案为:

4、一种基于fpga的通用共轭对称矩阵求逆架构,其特征在于,包括存储单元、状态控制单元和运算单元;

5、存储单元,存储输入的共轭对称矩阵和对应的矩阵阶数、中间计算矩阵和最终结果矩阵;

6、状态控制单元,控制运算单元的运算功能以及控制从存储单元读取矩阵数据;

7、运算单元,对矩阵数据进行运算,所述的运算包括乘法、加减法、除法和开根号。

8、本发明进一步的技术方案:所述的存储单元包括ram_r、ram_l1、ram_l2、ram_l3、ram_s1、ram_s2;其中ram_r用于存储输入的共轭对称矩阵r和结果矩阵a,ram_l1、ram_l2、ram_l3、ram_s1、ram_s2用于存储中间计算矩阵。

9、本发明进一步的技术方案:所述的运算单元包括复乘子模块、加减子模块、除法子模块、开根子模块,状态控制单元分别通过控制复乘开关、加减开关、除法开关、开根开关对复乘子模块、加减子模块、除法子模块、开根子模块进行控制。

10、一种基于fpga的通用共轭对称矩阵求逆方法,其特征在于步骤如下:

11、步骤1:对于n阶共轭对称矩阵r,按先列后行输入数据;输入矩阵阶数n,输入处理时钟;矩阵求逆模块收到数据后存入初始存储器ram_r,其中高地址存矩阵的行数据,低地址存矩阵的列数据;

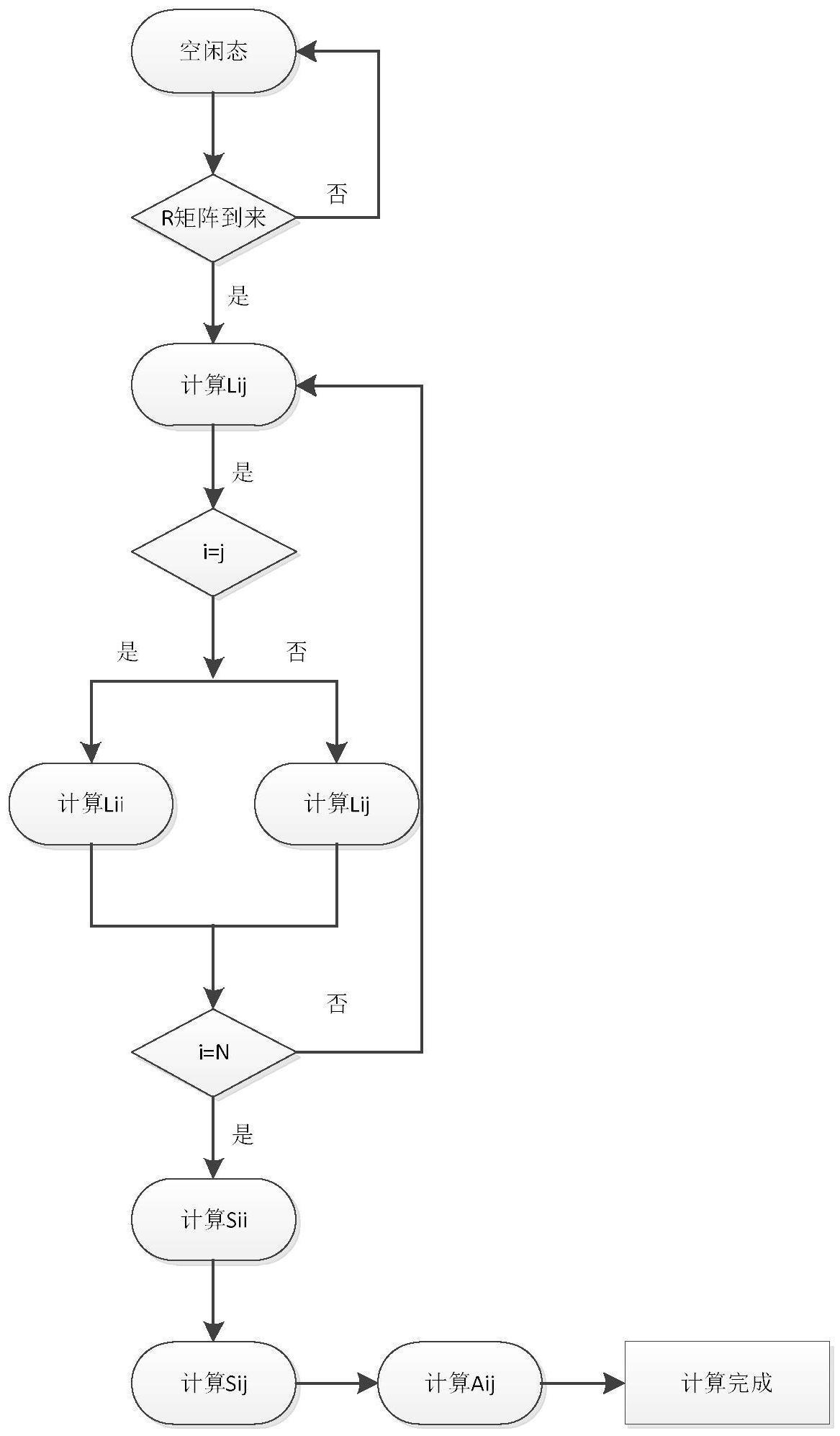

12、步骤2:状态控制单元收到矩阵r数据后由空闲状态转入计算lij状态,判断若i=j则为l的对角元素,状态控制单元将运算单元的乘法、加减法和开根号运算功能打开,同时控制读出ram_r中的rjj和ram_l1中的ljk,计算完成后的ljj存入3个l矩阵的ram;判断若i≠j,状态控制单元将运算单元的乘法、加减法和除法功能打开,同时控制读出ram_r中的rij、ram_l1中的lik、ram_l2中的ljk和ram_l3中的ljj,计算完成后的lij存入3个l矩阵的ram;判断若i=j=n,则l矩阵计算完成,开始计算s矩阵,否则循环计算l矩阵;

13、步骤3:步骤2计算l矩阵完成后,开始计算s矩阵;判断若i=j则计算s矩阵的对角元素,状态控制单元将除法功能打开,直接将ram_l1中的lii连续读出,流水送入运算单元完成除法运算;判断若i≠j,状态控制单元将运算单元的乘法、加法和除法功能打开,同时控制读出ram_l1中的lik、ram_s中的skj和ram_l2中的lii送入运算单元,计算完成后的sij存入2个s矩阵的ram;判断若i=j=n,则s矩阵计算完成,开始计算a矩阵,否则循环计算s矩阵;

14、步骤4:步骤3计算s矩阵完成后,开始计算a矩阵;状态控制单元将乘法和加法功能打开,计算aij时将ram_s1中的ski与ram_s2中的skj读出送入运算单元,其中k=1,2,…n;计算完成后的a矩阵各元素存入初始存储器ram_r,完成矩阵求逆计算。

15、本发明进一步的技术方案:所述的输入数据:位宽64bit,格式为单精度浮点,其中低32bit为实部,高32bit为虚部。

16、本发明进一步的技术方案:所述的时钟频率为80~250mhz。

17、一种基于fpga的通用共轭对称矩阵求逆方法的应用,其特征在于用于雷达系统中的旁瓣对消、空时自适应处理算法中。

18、一种计算机系统,其特征在于包括:一个或多个处理器,计算机可读存储介质,用于存储一个或多个程序,其中,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器实现上述的方法。

19、一种计算机可读存储介质,其特征在于存储有计算机可执行指令,所述指令在被执行时用于实现上述的方法。

20、本发明的有益效果在于:

21、本发明提供的一种基于fpga的通用共轭对称矩阵求逆方法,针对高阶共轭对称矩阵的求逆问题,基于fpga实现cholesky算法,提出了一种fpga实现架构,技术架构主要包含存储单元、状态控制单元与运算单元,通过参数化矩阵阶数以实现任意阶的共轭对称求逆运算。通过分时复用运算单元的方法节约了fpga资源,通过每个运算状态流水的方法降低了运算时间,满足计算精度和运算时间,且共轭对称矩阵求逆的通用需求。

技术特征:

1.一种基于fpga的通用共轭对称矩阵求逆架构,其特征在于,包括存储单元、状态控制单元和运算单元;

2.根据权利要求1所述的基于fpga的通用共轭对称矩阵求逆架构,其特征在于,所述的存储单元包括ram_r、ram_l1、ram_l2、ram_l3、ram_s1、ram_s2;其中ram_r用于存储输入的共轭对称矩阵r和结果矩阵a,ram_l1、ram_l2、ram_l3、ram_s1、ram_s2用于存储中间计算矩阵。

3.根据权利要求1所述的基于fpga的通用共轭对称矩阵求逆架构,其特征在于,所述的运算单元包括复乘子模块、加减子模块、除法子模块、开根子模块,状态控制单元分别通过控制复乘开关、加减开关、除法开关、开根开关对复乘子模块、加减子模块、除法子模块、开根子模块进行控制。

4.一种基于fpga的通用共轭对称矩阵求逆方法,其特征在于步骤如下:

5.根据权利要求4所述的一种基于fpga的通用共轭对称矩阵求逆方法,其特征在于,所述的输入数据:位宽64bit,格式为单精度浮点,其中低32bit为实部,高32bit为虚部。

6.根据权利要求4所述的一种基于fpga的通用共轭对称矩阵求逆方法,其特征在于,所述的时钟频率为80~250mhz。

7.一种基于fpga的通用共轭对称矩阵求逆方法的应用,其特征在于用于雷达系统中的旁瓣对消、空时自适应处理算法中。

8.一种计算机系统,其特征在于包括:一个或多个处理器,计算机可读存储介质,用于存储一个或多个程序,其中,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器实现权利要求4所述的方法。

9.一种计算机可读存储介质,其特征在于存储有计算机可执行指令,所述指令在被执行时用于实现权利要求4所述的方法。

技术总结

本发明涉及一种基于FPGA的通用共轭对称矩阵求逆架构、方法及应用,属于现场可编程门阵列FPGA技术领域,应用于雷达上。针对高阶共轭对称矩阵的求逆问题,基于FPGA实现Cholesky算法,提出了一种FPGA实现架构,技术架构包含存储单元、状态控制单元与运算单元,通过参数化矩阵阶数以实现任意阶的共轭对称求逆运算。通过分时复用运算单元的方法节约了FPGA资源,通过每个运算状态流水的方法降低了运算时间,满足计算精度和运算时间,且共轭对称矩阵求逆的通用需求。

技术研发人员:陈亮,田剑锋,崔向阳,钟凡

受保护的技术使用者:西安电子工程研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!