一种基于随机计算原理的存内乘加计算架构芯片电路的制作方法

本公开属于信息和集成电路领域,具体涉及一种基于随机计算原理的存内乘加运算架构芯片电路。

背景技术:

1、随着信息时代的进步,图像处理、科学计算、机器学习、5g通信等领域都得到了快速发展。数据处理量和计算能耗的增加向传统的冯·诺伊曼(von·neumann)计算架构提出挑战。矩阵向量相乘(matrixvector multiplication,mvm),即乘加运算(multiplicationandaccumulation,mac)在每个领域中都扮演着重要的角色。在传统计算架构中,乘加运算需要乘法器和加法器构成,且随着计算精度的上升,所需晶体管数量和电路面积能耗都在急剧增加。

2、随机计算(stochastic computing,sc)作为新型的计算范式逐渐受到人们的关注。不同于传统的二进制数据表示方式,随机计算中数据是通过由0和1比特构成的随机比特流中比特1的占比对数据进行表示。随机计算具有结构简单、容错率高、精度可调等优点。

3、现有的随机计算包括两部分:随机数发生器(rng)生成随机比特流和逻辑门进行计算。例如,通过与门(and gate)可以实现乘法运算,通过选通器(mux)可以实现部分加法运算,但是无法实现完整的乘加运算,因此使得随机计算的应用受到限制。因此,亟需一种基于随机计算原理的存内乘加运算架构的设计,来有效减少实现矩阵向量乘法所需的硬件和功耗代价。

技术实现思路

1、针对现有技术中的不足,本公开的目的在于提供一种基于随机计算原理的存内乘加运算架构芯片电路,该电路通过计数单元对随机比特流进行计数,能够完善现有随机计算无法实现加法运算的不足,从而实现存内乘加运算。

2、为实现上述目的,本公开提供以下技术方案:

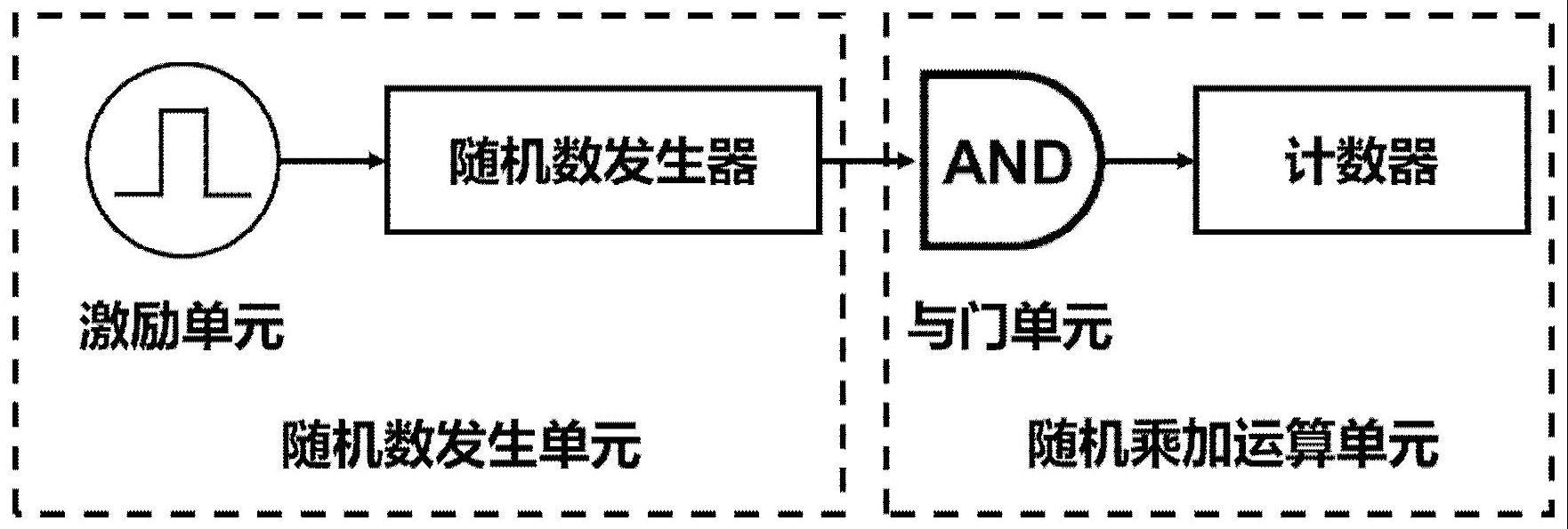

3、一种基于随机计算原理的存内乘加运算架构芯片电路,包括:

4、激励单元,用于产生激励信号;

5、随机数发生单元,用于在所述激励信号的激励下生成比特1具有特定占比的随机比特流;

6、与门逻辑单元,用于对具有特定占比的随机比特流进行随机乘法运算,并输出与随机乘法结果对应概率的随机比特流;

7、计数单元,用于对与门逻辑单元输出的随机比特流进行计数,以实现随机加法运算。

8、优选的,所述激励信号为电压激励或电流激励。

9、优选的,所述电压激励或电流激励包括但不限于方波、正弦波、三角波、梯形波、阶梯波、锯齿波和混合波中任意一种。

10、优选的,所述随机数发生单元包括如下任一:硅基、二维材料金属-氧化物半导体场效应晶体管和存储器。

11、优选的,通过调控激励信号的幅值大小和脉冲宽度以调整随机数发生单元所生成的随机比特流中比特1的占比。

12、优选的,所述计数单元包括第一计数器和第二计数器。

13、本公开还提供一种基于随机计算原理的存内乘加运算方法,包括如下步骤:

14、s100:激励生成比特1具有特定占比的随机比特流;

15、s200:对特定占比的随机比特流进行随机乘法运算,以输出与随机乘法结果对应概率的随机比特流;

16、s300:对与随机乘法结果对应概率的随机比特流进行计数,以实现随机加法运算。

17、本公开还提供一种计算机存储介质,其中,所述计算机存储介质存储有计算机可执行指令,所述计算机可执行指令用于执行如前所述的方法。

18、本公开还提供一种电子设备,包括:

19、存储器,处理器及存储在存储器上并可在处理器上运行的计算机程序,其中,

20、所述处理器执行所述程序时实现如前所述的方法。

21、与现有技术相比,本公开带来的有益效果为:

22、1、相比于传统的随机计算通过选通器实现部分加法功能,本公开通过选用2个计数器实现随机加法运算,能够使得加法运算功能更加完善,利于加速实现乘加运算;

23、2、本公开中的与门单元和计数单元可以实现并行操作,随机比特流可以进行并行生成、并行乘法和并行加法运算,使得本公开中的随机乘加运算的可扩展性和并行性;

24、3、本公开中用计数器代替选通器实现随机计算,使得本公开所述电路结构简单、电路面积小、便于进行大规模集成,大大降低了随机计算的成本,在5g通信、机器学习、科学计算等信息技术领域具有良好的应用前景。

技术特征:

1.一种基于随机计算原理的存内乘加运算架构芯片电路,包括:

2.根据权利要求1所述的电路,其中,优选的,所述激励信号为电压激励或电流激励。

3.根据权利要求2所述的电路,其中,所述电压激励的脉冲幅值为1mv到10v;所述电流激励的脉冲幅值为1na到10ma。

4.根据权利要求1所述的电路,其中,所述电压激励或电流激励包括但不限于方波、正弦波、三角波、梯形波、阶梯波、锯齿波和混合波中任意一种。

5.根据权利要求1所述的电路,其中,所述随机数发生单元包括如下任一:硅基、二维材料金属-氧化物半导体场效应晶体管和存储器。

6.根据权利要求1所述的电路,其中,通过调控激励信号的幅值大小和脉冲宽度以调整随机数发生单元所生成的随机比特流中比特1的占比。

7.根据权利要求1所述的电路,其中,所述计数单元包括第一计数器和第二计数器。

8.一种基于随机计算原理的存内乘加运算方法,包括如下步骤:

9.一种计算机存储介质,其中,所述计算机存储介质存储有计算机可执行指令,所述计算机可执行指令用于执行权利要求8所述的方法。

10.一种电子设备,包括:

技术总结

本公开揭示了一种基于随机计算原理的存内乘加运算架构芯片电路,包括:激励单元,用于产生激励信号;随机数发生单元,用于在所述激励信号的激励下生成具有特定占比的随机比特流;与门逻辑单元,用于对具有特定占比的随机比特流进行随机乘法运算,并输出与随机乘法结果对应概率的随机比特流;计数单元,用于对与门逻辑单元输出的随机比特流进行计数,以实现随机加法运算。本公开能够完善随机计算的加法功能,提高乘加运算的并行度和可扩展性,以较低的功耗得到准确的乘加运算结果。

技术研发人员:柴正,石光明,袁玺惠,简佳佳,闵泰

受保护的技术使用者:鹏城实验室

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!