一种NVMe非连续地址传输的数据缓存系统的制作方法

本发明涉及一种nvme非连续地址传输的数据缓存系统,属于数据存储。

背景技术:

1、非易失性内存主机控制器接口规范(nvme)是一种低延时、内部并发化的总线传输协议规范,多用于固态硬盘(ssd)等存储系统。nvme可连接主机(host)和内存子系统,并提供高速、非统一内存访问优化、高度可扩展的传输。nvme控制器往往通过直接内存访问(direct memory access)进行数据的搬移,实现数据在host端和内存子系统之间的双向传输。目前通用的直接内存访问往往通过配置一个源地址和一个目的地址来实现数据的传输,然而这极大限制了数据传输的灵活性。在实际应用中,为实现内存空间的灵活管理,常需要数据在内存子系统中以非连续地址存放。此时,直接内存访问则无法满足多源地址或多目的地址传输的需求。

技术实现思路

1、本发明目的是提供了一种nvme非连续地址传输的数据缓存系统,提高了nvme存储系统的灵活性。

2、本发明为实现上述目的,通过以下技术方案实现:

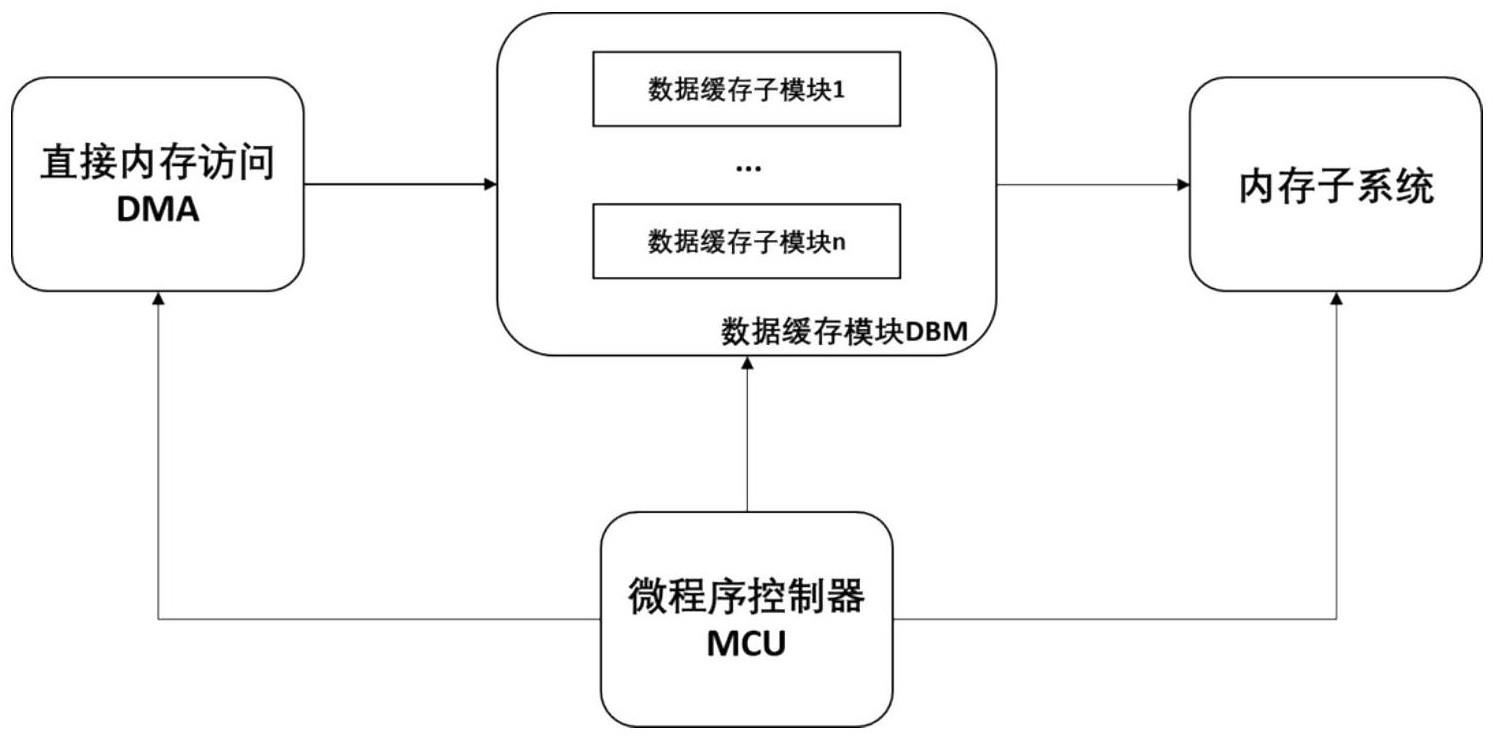

3、包括直接内存访问、数据缓存模块、内存子系统和微程序控制器;所述微程序控制器与直接内存访问、数据缓存模块、内存子系统连接,所述直接内存访问、内存子系统还与数据缓存模块连接;

4、所述微程序控制器将直接内存访问的源地址或者目的地址配置为描述符,并将该描述符发送到数据缓存模块;host读数据时,直接内存访问的源地址为内存地址;host写数据时,直接内存访问的目的地址为内存地址;

5、直接内存访问将该描述符作为访问地址,发给数据缓存模块;

6、所述数据缓存模块对数据进行划分,并以缓存包为单位进行缓存和传输数据,所述缓存包具有标识符,其大小为逻辑区块数量的整数倍,所述数据缓存模块接收直接访问内存发送的描述符,并对描述符解析,获取数据传输地址信息;

7、所述内存子系统为系统提供内存。

8、优选的,所述描述符包括内存基地址,缓存包标识符,缓存包数量,地址模式,数据缓存模块配置信息。

9、优选的,所述描述符中地址模式包括缓存包地址模式和缓存包地址链表模式,所述缓存包地址模式将缓存包在内存子系统中连续存储,所述缓存包地址链表模式将缓存包在内存子系统中非连续存储。

10、优选的,所述缓存包地址模式下,微程序控制器在描述符中配置内存基地址ba、缓存包标识符bid和缓存包数量bn信息,数据缓存模块根据描述符以及微程序控制器配置的bs,计算每个缓存包对应的内存首地址,并将bn个缓存包连续存入内存,其中,内存首地址=ba+bid*bs。

11、优选的,缓存包地址链表模式下,微程序控制器在描述符中配置内存基地址ba和地址链所存放的地址,并在该地址上写入地址链信息,数据缓存模块首先从描述符中获取地址链存放地址,随后从地址链存放地址中获取多个地址链信息,并解析出缓存包的地址;其中,每个地址链所指示地址范围连续,所述地址链表存放于内存子系统中或数据缓存模块中。

12、优选的,缓存包地址链表模式下,地址链信息包含缓存包的缓存包标识符bid,缓存包数量bn和链表连接信息,其中链表信息包括下一地址链地址、链表结束符信息;地址链规定为在地址空间中连续存储或通过在地址链中指示下一链表地址非连续存储。

13、优选的,缓存包地址链表模式下,数据缓存模块根据每一链表中的缓存包标识符bid和缓存包数量bn信息,计算出每一地址链指向的内存首地址,并将bn个缓存包连续存入内存,其中,地址链指向内存首地址=ba+bid*bs。

14、优选的,所述数据缓存模块中包含一个及以上数据缓存子模块;所述数据缓存模块中配置用于缓存传输数据的缓存空间。

15、本发明的优点在于:本发明实现了数据在内存子系统中的分段存储,并且具备一定处理器可管理的地址灵活性。所设计系统内部可包含多个数据缓存子系统以及数据缓存空间,实现了数据并行处理的需求,并提高了数据传输性能。该系统同时可支持内部执行状态及运行错误信息的反馈,以便处理器及外部模块可感知数据传输状态及进行使用中的调试与分析。

技术特征:

1.一种nvme非连续地址传输的数据缓存系统,其特征在于,包括直接内存访问、数据缓存模块、内存子系统和微程序控制器;所述微程序控制器与直接内存访问、数据缓存模块、内存子系统连接,所述直接内存访问、内存子系统还与数据缓存模块连接;

2.根据权利要求1所述的nvme非连续地址传输的数据缓存系统,其特征在于,所述描述符包括内存基地址,缓存包标识符,缓存包数量,地址模式,数据缓存模块配置信息。

3.根据权利要求1所述的nvme非连续地址传输的数据缓存系统,其特征在于,所述描述符中地址模式包括缓存包地址模式和缓存包地址链表模式,所述缓存包地址模式将缓存包在内存子系统中连续存储,所述缓存包地址链表模式将缓存包在内存子系统中非连续存储。

4.根据权利要求3所述的nvme非连续地址传输的数据缓存系统,其特征在于,所述缓存包地址模式下,微程序控制器在描述符中配置内存基地址ba、缓存包标识符bid和缓存包数量bn信息,数据缓存模块根据描述符以及微程序控制器配置的缓存包大小bs,计算每个缓存包对应的内存首地址,并将bn个缓存包连续存入内存,其中,内存首地址=ba+bid*bs。

5.根据权利要求3所述的nvme非连续地址传输的数据缓存系统,其特征在于,缓存包地址链表模式下,微程序控制器在描述符中配置内存基地址ba和地址链所存放的地址,并在该地址上写入地址链信息,数据缓存模块首先从描述符中获取地址链存放地址,随后从地址链存放地址中获取多个地址链信息,并解析出缓存包的地址;其中,每个地址链所指示地址范围连续,所述地址链表存放于内存子系统中或数据缓存模块中。

6.根据权利要求5所述的nvme非连续地址传输的数据缓存系统,其特征在于,缓存包地址链表模式下,地址链信息包含缓存包的缓存包标识符bid,缓存包数量bn和链表连接信息,其中链表信息包括下一地址链地址、链表结束符信息;地址链规定为在地址空间中连续存储或通过在地址链中指示下一链表地址非连续存储。

7.根据权利要求6所述的nvme非连续地址传输的数据缓存系统,其特征在于,缓存包地址链表模式下,数据缓存模块根据每一链表中的缓存包标识符bid和缓存包数量bn信息,计算出每一地址链指向的内存首地址,并将bn个缓存包连续存入内存,其中,地址链指向内存首地址=ba+bid*bs。

8.根据权利要求1所述的nvme非连续地址传输的数据缓存系统,其特征在于,所述数据缓存模块中包含一个及以上数据缓存子模块;所述数据缓存模块中配置用于缓存传输数据的缓存空间。

技术总结

本发明提供了一种NVMe非连续地址传输的数据缓存系统,属于数据存储技术领域。将NVMe控制器中直接内存访问的单一源地址或目的地址进行扩展,将其配置为描述符格式,用于包含多地址和配置信息。所设计的数据缓存系统接收直接内存访问发出的读地址或写地址信息,即配置的描述符信息,并进行解析,获取数据所需传输的多段地址,并将数据进行读出或写入。该系统内部可包含多个数据缓存子系统以及数据缓存空间,实现数据并行处理的需求,并提高数据传输性能。该系统同时可支持内部执行状态及运行错误信息的反馈,以便处理器及外部模块可感知数据传输状态及进行使用中的调试与分析。

技术研发人员:付溢华,李瑞东,刘奇浩

受保护的技术使用者:山东华芯半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!