一种基于双同步寄存器的全局同步方法及芯片实现与流程

本申请涉及芯片,特别是涉及一种基于双同步寄存器的全局同步方法及芯片实现。

背景技术:

1、目前,在针对计算机设备中的各个节点进行控制同步时,通常需要针对各个节点对应的节点处理机的操作事件进行全局同步。此外,在针对各个节点处理机进行全局同步时,各个节点处理机对应的不同的同步进程之间存在执行冲突,该冲突会阻塞节点处理机的执行线程,进而影响并行程序的执行效率。

2、然而,鉴于现有技术并未解决各个节点处理机对应的不同的同步进程之间存在的执行冲突,故基于现有技术进行的全局同步,难以有效提升并行程序的执行效率。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种基于双同步寄存器的全局同步方法及芯片实现。

2、第一方面,本申请提供了一种基于双同步寄存器的芯片,所述芯片配置有若干节点;各所述节点配置有对应的时钟模块和节点处理机;其中:

3、所述时钟模块包括第一同步寄存器和第二同步寄存器;

4、所述第一同步寄存器和所述第二同步寄存器用于交替记录各所述节点处理机对应的信号同步状态;在所述第一同步寄存器处于活动状态的情况下,所述第二同步寄存器处于非活动状态。

5、在其中一个实施例中,所述第一同步寄存器的数量与所述第二同步寄存器的数量的和等于所述节点处理机的数量。

6、在其中一个实施例中,所述芯片还包括控制器;所述控制器用于分别将时钟同步信号和时钟同步报文发送至各所述节点,并对应调整各所述节点在所述第一同步寄存器中的奇偶标识符或所述第二同步寄存器中的奇偶标识符。

7、在其中一个实施例中,所述时钟模块为栅极移位时钟模块。

8、第二方面,本申请还提供了一种全局同步方法,应用于上述芯片,所述方法包括:

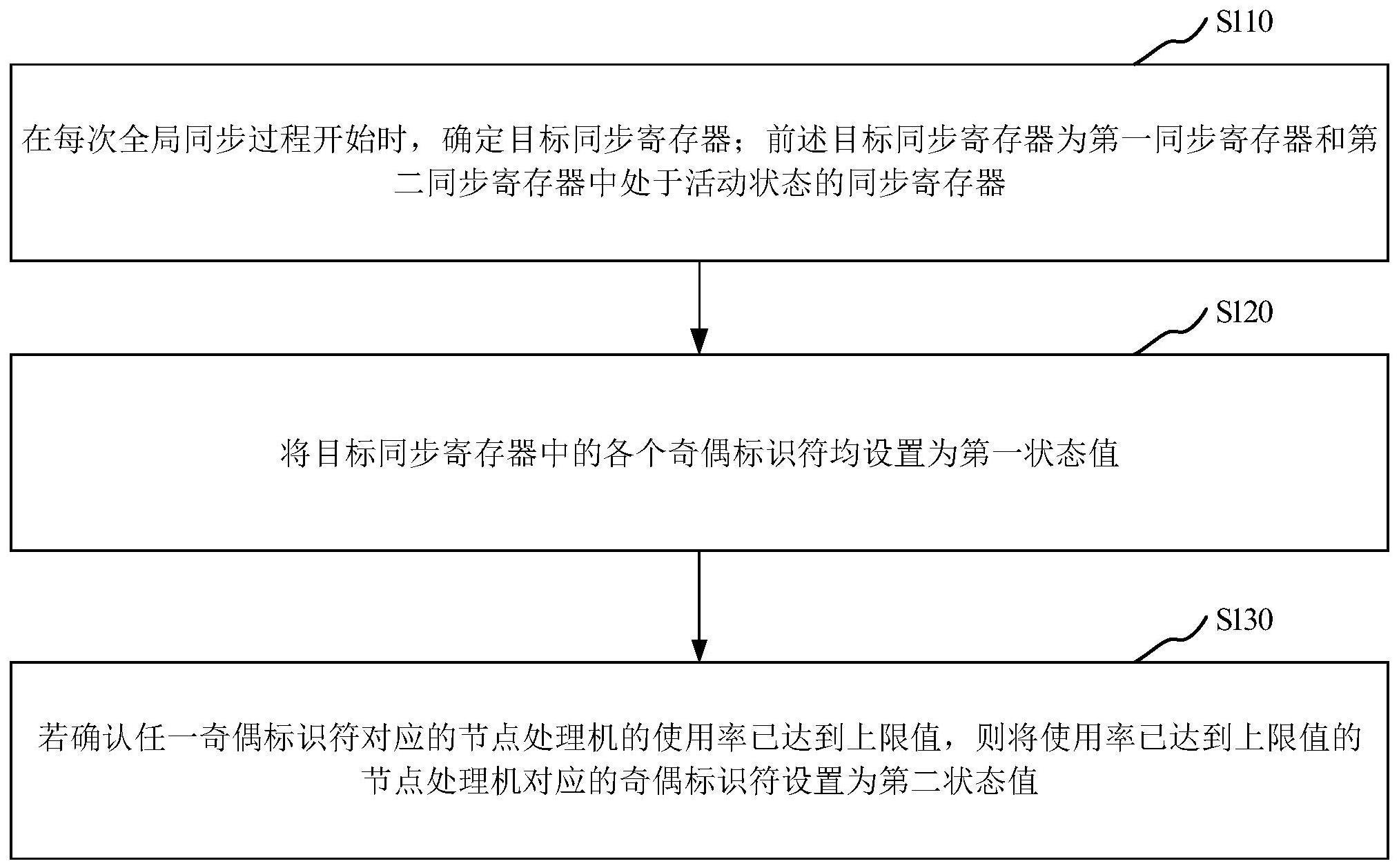

9、在每次全局同步过程开始时,确定目标同步寄存器;所述目标同步寄存器为所述第一同步寄存器和所述第二同步寄存器中处于所述活动状态的同步寄存器;

10、将所述目标同步寄存器中的各个奇偶标识符均设置为第一状态值;

11、若确认任一所述奇偶标识符对应的节点处理机的使用率已达到上限值,则将所述使用率已达到上限值的节点处理机对应的奇偶标识符设置为第二状态值。

12、在其中一个实施例中,所述将所述使用率已达到上限值的节点处理机对应的奇偶标识符设置为第二状态值之后,所述方法还包括:

13、将所述使用率已达到上限值的节点处理机对应的节点,作为初始节点;基于所述初始节点和广度优先搜索算法,确定各所述节点所在的通信层;根据各所述节点对应的节点处理机的使用率,在各所述通信层中生成所述时钟同步报文。

14、在其中一个实施例中,所述方法还包括:在各所述节点处理机的使用率均已达到上限值,且各所述节点所在的通信层均已完成层通信的情况下,将所述目标同步寄存器中的各个奇偶标识符均设置为所述第二状态值;将所述目标同步寄存器对应的硬件按位和操作结果,分别设置为所述第二状态值。

15、第三方面,本申请还提供了一种全局同步装置,应用于上述芯片,所述装置包括:

16、目标同步寄存器获取单元,用于在每次全局同步过程开始时,确定目标同步寄存器;所述目标同步寄存器为所述第一同步寄存器和所述第二同步寄存器中处于所述活动状态的同步寄存器;

17、第一状态值设置单元,用于将所述目标同步寄存器中的各个奇偶标识符均设置为第一状态值;

18、第二状态值调整单元,用于若确认任一所述奇偶标识符对应的节点处理机的使用率已达到上限值,则将所述使用率已达到上限值的节点处理机对应的奇偶标识符设置为第二状态值。

19、第四方面,本申请还提供了一种计算机设备。所述计算机设备包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现上述方法的步骤。

20、第五方面,本申请还提供了一种计算机可读存储介质。所述计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述方法的步骤。

21、第六方面,本申请还提供了一种计算机程序产品。所述计算机程序产品,包括计算机程序,该计算机程序被处理器执行时实现上述方法的步骤。

22、上述基于双同步寄存器的全局同步方法及芯片实现,首先,在每次全局同步过程开始时,确定目标同步寄存器;前述目标同步寄存器为第一同步寄存器和第二同步寄存器中处于活动状态的同步寄存器。然后,将目标同步寄存器中的各个奇偶标识符均设置为第一状态值。最后,若确认任一奇偶标识符对应的节点处理机的使用率已达到上限值,则将使用率已达到上限值的节点处理机对应的奇偶标识符设置为第二状态值。本申请通过为芯片中的各个节点对应的节点处理机配置第一同步寄存器和第二同步寄存器,不仅能够避免在芯片中进行两次全局同步过程时可能发生的执行冲突,还能够有效提升并行程序的执行效率。

技术特征:

1.一种基于双同步寄存器的芯片,其特征在于,所述芯片配置有若干节点;各所述节点配置有对应的时钟模块和节点处理机;其中:

2.根据权利要求1所述的芯片,其特征在于,所述第一同步寄存器的数量与所述第二同步寄存器的数量的和等于所述节点处理机的数量。

3.根据权利要求2所述的芯片,其特征在于,所述芯片还包括控制器;所述控制器用于分别将时钟同步信号和时钟同步报文发送至各所述节点,并对应调整各所述节点在所述第一同步寄存器中的奇偶标识符或所述第二同步寄存器中的奇偶标识符。

4.根据权利要求1所述的芯片,其特征在于,所述时钟模块为栅极移位时钟模块。

5.一种全局同步方法,其特征在于,应用于权利要求1至4中任一项所述的芯片,所述方法包括:

6.根据权利要求5所述的方法,其特征在于,所述将所述使用率已达到上限值的节点处理机对应的奇偶标识符设置为第二状态值之后,所述方法还包括:

7.根据权利要求5所述的方法,其特征在于,所述方法还包括:

8.一种全局同步装置,其特征在于,应用于权利要求1至4中任一项所述的芯片,所述装置包括:

9.一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器执行所述计算机程序时实现权利要求5至7中任一项所述的方法的步骤。

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求5至7中任一项所述的方法的步骤。

技术总结

本申请涉及一种基于双同步寄存器的全局同步方法及芯片实现,该芯片配置有若干节点;各所述节点配置有对应的时钟模块和节点处理机;其中:所述时钟模块包括第一同步寄存器和第二同步寄存器;所述第一同步寄存器和所述第二同步寄存器用于交替记录各所述节点处理机对应的信号同步状态;在所述第一同步寄存器处于活动状态的情况下,所述第二同步寄存器处于非活动状态。本申请通过为芯片中的各个节点对应的节点处理机配置第一同步寄存器和第二同步寄存器,不仅能够避免在芯片中进行两次全局同步过程时可能发生的执行冲突,还能够有效提升并行程序的执行效率。

技术研发人员:陶伟,董飞龙,姚浩,陈军健,蔡田田,关志华,邝野

受保护的技术使用者:南方电网数字电网研究院有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!